最近看到行業(yè)群里面經(jīng)常有人問什么是形式驗證,今天的文章和大家介紹下形式驗證(Formal verification)。

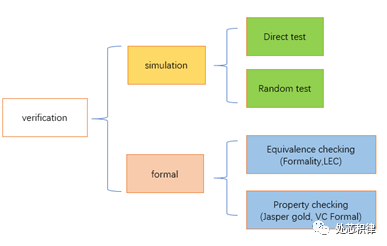

相信很多人已經(jīng)接觸過驗證。如我前面有篇文章所寫驗證分為IP驗證,FPGA驗證,SOC驗證和CPU驗證,這其中大部分是采用動態(tài)仿真(dynamic simulation)實現(xiàn),即通過給定設(shè)計(design)端口測試激勵,結(jié)合時間消耗判斷設(shè)計的輸出結(jié)果是否符合預期。動態(tài)仿真又分為定向測試和隨機測試。現(xiàn)在很多公司用的UVM驗證方法學便是建立在動態(tài)仿真的基礎(chǔ)上的。

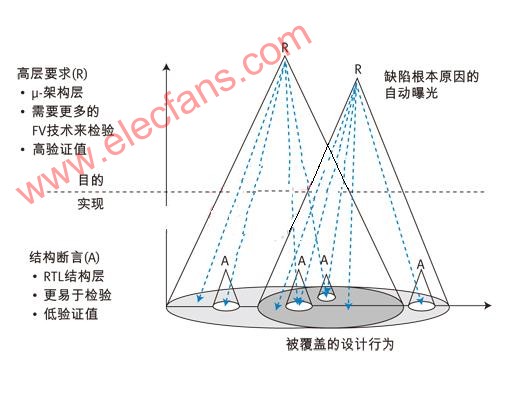

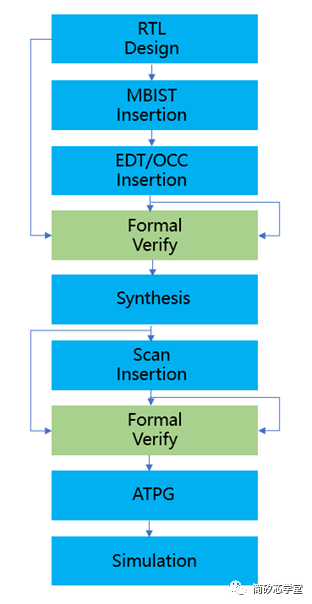

形式驗證不同于仿真驗證,它是通過數(shù)學上完備地證明或驗證電路的實現(xiàn)方法是否確實實現(xiàn)了電路設(shè)計所描述的功能。形式驗證方法分為等價性檢查(equivalence checking)如Formality,LEC等和屬性檢查(Property checking)如Jasper gold,VC Formal 等。我們這里講的形式驗證特指屬性的檢查(Property checking)。

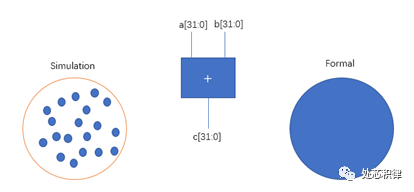

如上圖所示,在一個簡單的加法設(shè)計中,我們采用動態(tài)仿真的方式去驗證上述運算是類似一種丟飛鏢的過程,想要驗到所有的場景要運行2的64次方即18446744073709551616次,這只是簡單的加法運算,如果再加入其它稍微復雜的邏輯,想用動態(tài)仿真的方式打完所有情況是非常困難的。

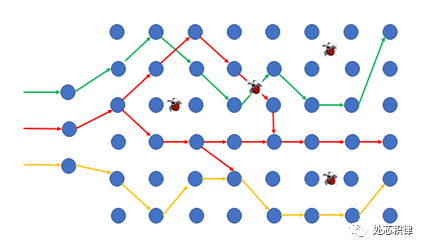

另外一種場景是當信號從設(shè)計的端口輸入,信號流的走向會根據(jù)不同設(shè)定或者狀態(tài)選擇走向不同的路徑。如上圖所示,當信號流可選擇的路徑很多時,通過動態(tài)仿真也是很難覆蓋到所有路徑的。

上述兩個問題用Formal就可以很好的解決掉。

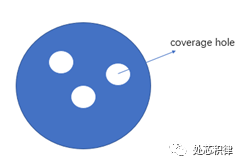

除了功能驗證上的使用,F(xiàn)ormal也可以被用在coverage的收集上。在設(shè)計里面有不少代碼是無法執(zhí)行到的。如果用動態(tài)仿真去找這些點,一般的做法是跑大量的回歸測試(regression),收集coverage,然后針對沒打到的coverage hole找designer去review。整個過程走下來會花費不少人力。而用formal可以比較輕松高效的找到其中的一些點。

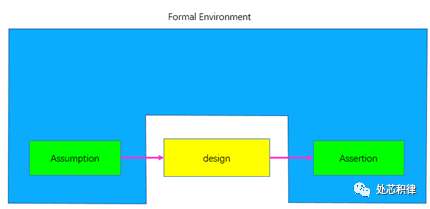

介紹了這么多,那么Formal是怎么實現(xiàn)的呢?用Formal驗證需要輸入設(shè)計(design),約束(constraint)和待驗證的property。這里的設(shè)計一般是指RTL,約束指的是assumption,clock,reset等,propert是指assertion。

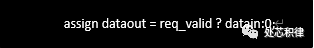

下面是一個簡單的例子,當設(shè)計如下

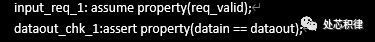

我們可以通過下面描述來驗證該段邏輯,先驗證req_valid 為高時,dataout等于datain;

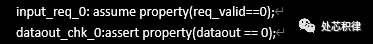

再驗證req_valid 為低時,dataout等于0。

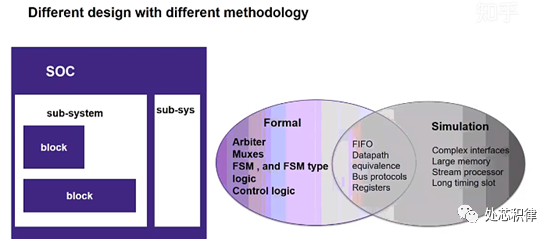

Formal適合所有驗證場景嗎?當然不是,因為formal是通過數(shù)學運算去完成完備性驗證,在一些簡單的邏輯如arbiter,muxes,F(xiàn)SM,Control logic上比較適合用formal去驗證,但是對一些復雜的場景,比如涉及到大量的memory,復雜的總線傳輸,多模塊協(xié)助工作等場景都不太適合用Formal。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605177 -

仿真器

+關(guān)注

關(guān)注

14文章

1019瀏覽量

83883 -

SoC芯片

+關(guān)注

關(guān)注

1文章

617瀏覽量

34989 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59911 -

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19207

原文標題:什么是形式驗證(Formal 驗證)

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

EDA形式化驗證漫談:仿真之外,驗證之內(nèi)

A Roadmap for Formal Property

深層解析形式驗證

新思科技憑借突破性機器學習技術(shù)將形式屬性驗證性能提高10倍

從C/C++到RTL,提速100倍的形式化驗證加快AI算法到芯片的迭代

形式驗證工具對系統(tǒng)功能的設(shè)計

Formal Verification:形式驗證的分類、發(fā)展、適用場景

可以通過降低約束的復雜度來優(yōu)化Formal的執(zhí)行效率嗎?

談?wù)?b class='flag-5'>Formal驗證中的Equivalence Checking

Formal Verification的基礎(chǔ)知識

數(shù)字驗證中Formal Verification在國內(nèi)的應(yīng)用以及前景如何?

Formal Verify形式驗證的流程概述

什么是形式驗證(Formal驗證)?Formal是怎么實現(xiàn)的呢?

什么是形式驗證(Formal驗證)?Formal是怎么實現(xiàn)的呢?

評論