內(nèi)容摘要

電力電子元件可提高所有行業(yè)和應(yīng)用中電機(jī)和馬達(dá)的能源效率。這些電力電子元件越來(lái)越多地被更密集地封裝在一起,靠近或放置在電機(jī)本身附近或上面,因此受到應(yīng)用中的聲振粗糙度和振動(dòng)的影響。必須有效地消除這些組件的散熱,以防止器件過早失效,或者在最嚴(yán)重的情況下,泄漏電流隨著溫度的升高而增加,導(dǎo)致熱失控,進(jìn)一步增加散熱,直到半導(dǎo)體芯片實(shí)際熔化。

安森美半導(dǎo)體承諾向客戶提供最高質(zhì)量的產(chǎn)品,為此,必須了解如何以盡可能少的缺陷引入和生產(chǎn)寬帶隙半導(dǎo)體等新技術(shù),以便在部件經(jīng)歷溫度波動(dòng)時(shí)提高器件性能和可靠性。

這些溫度波動(dòng)會(huì)導(dǎo)致焊料芯片貼裝開裂,或芯片貼裝與芯片之間或芯片貼裝與基板之間分層。這反過來(lái)又導(dǎo)致芯片溫度升高,因?yàn)閺男酒江h(huán)境的熱流路徑被破壞,進(jìn)一步提高了溫度波動(dòng)的大小,從而進(jìn)一步加快了損壞速度。器件壽命取決于許多因素,但根據(jù)芯片的工作溫度,安森美半導(dǎo)體知道,在相同的負(fù)載率下,溫度升高 10° C 大致相當(dāng)于壽命減少兩到三倍。

焊料芯片貼裝中可能發(fā)生的孔洞具有使芯片貼裝導(dǎo)熱性降低的綜合效應(yīng),并充當(dāng)可能形成裂紋的部位,因此焊料芯片貼裝孔洞是電力電子封裝中的主要可靠性問題之一。芯片貼裝孔洞的影響取決于焊料中孔洞的類型、圖案和孔洞的位置,因此真正了解這些孔洞對(duì)芯片貼裝熱阻的影響至關(guān)重要。

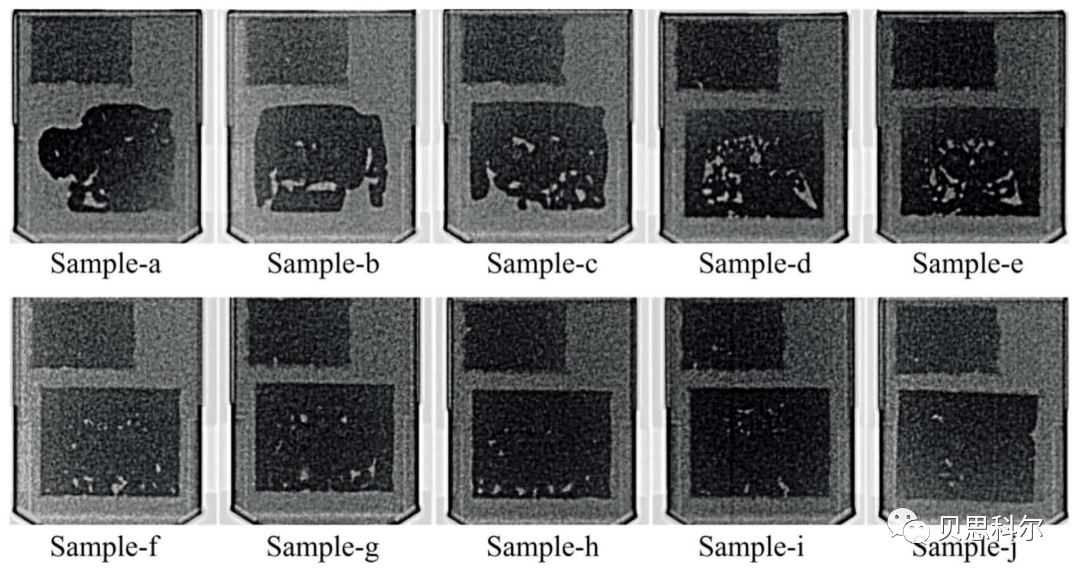

為了研究這一點(diǎn),安森美半導(dǎo)體選擇了一種絕緣柵雙極晶體管(IGBT),該晶體管與 TO-247 封裝中的二極管共同封裝。選擇十個(gè)樣品,這些樣品在芯片貼裝中具有不同的孔洞量,使用 X 射線成像檢測(cè),如圖 1 所示。

圖 1:樣品按 IBGT 芯片貼裝孔洞的降序排列。

這些樣品按孔洞總量(占芯片面積的百分比)和最大孔洞的大小(通常由芯片外圍的孔洞聚結(jié)引起)分類。

測(cè)量孔洞對(duì)芯片貼裝熱阻的影響需要一個(gè)高度靈敏的測(cè)量系統(tǒng),以及能夠識(shí)別芯片貼裝對(duì)所測(cè)量的整體熱阻貢獻(xiàn)的方法。這意味著遵循 JEDEC JESD51-14 標(biāo)準(zhǔn),使用瞬態(tài)雙界面測(cè)量(TDIM)方法測(cè)量結(jié)殼熱阻 θJC。熱阻Zth測(cè)量使用西門子Simcenter POWERTESTER ?1500A 進(jìn)行,它提供了必要的測(cè)量保真度,并結(jié)合 Zth 曲線的內(nèi)置結(jié)構(gòu)函數(shù)分析,以識(shí)別由于芯片貼裝引起的部分熱阻。

結(jié)構(gòu)函數(shù)是熱流路徑的一維表示,提供有關(guān)系統(tǒng)中熱特性空間分布的信息,將此信息顯示為熱量從芯片表面上的源傳遞到 Simcenter POWERTESTER ? 1500A中貼裝零件的冷板時(shí)累積熱阻與累積熱電容的圖表。該方法完全符合 JEDEC JESD51-14 標(biāo)準(zhǔn),屬于非侵入式方法,因?yàn)樗褂?JEDEC JESD51-1 中描述的電氣測(cè)試方法在測(cè)量過程中對(duì)芯片進(jìn)行電加熱和檢測(cè)芯片溫度。

“熱結(jié)構(gòu)函數(shù)分析提供了一種有效且非侵入式的方法來(lái)識(shí)別封裝設(shè)備各個(gè)層的物理特性。該技術(shù)補(bǔ)充了其他非破壞性故障分析技術(shù),例如 X 射線和 C-SAM,這些技術(shù)可以明確識(shí)別缺陷,但是,這些技術(shù)不提供任何有關(guān)這些缺陷對(duì)零件熱行為的影響信息。”

——蘇杰·辛格

安森美半導(dǎo)體

首席可靠性工程師

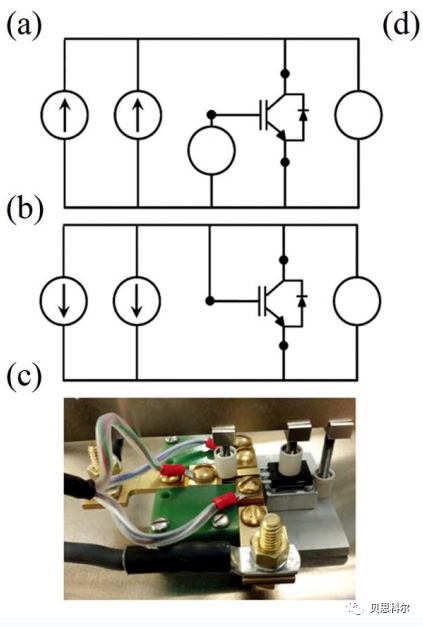

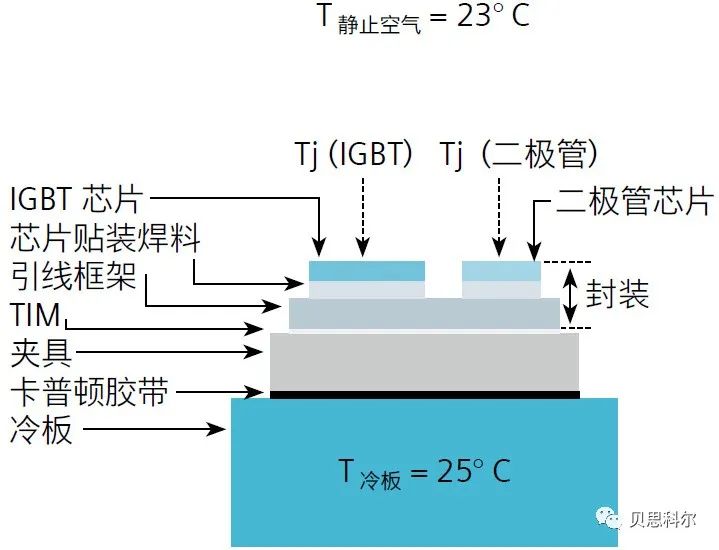

圖 3:(a)和(b)分別為 θ JC(IGBT) 和 θ JC(二極管)測(cè)量電路圖。(c)θ JC(IGBT)測(cè)量的實(shí)驗(yàn)裝置。(d)顯示不同層的橫截面和邊界條件的示意圖。

圖3(a)和(b)分別顯示了 IGBT 和二極管結(jié)溫的加熱和傳感電氣原理圖。IGBT 上的 Zth 測(cè)量是在飽和模式下完成的。圖3(c)顯示了 IGBT 測(cè)量的實(shí)驗(yàn)夾具。夾具通過 6 “/lb 的夾緊扭矩夾在冷板上,以確保良好的熱傳導(dǎo)。圖3(d)顯示了封裝結(jié)構(gòu)以及 IGBT 和二極管的物理隔離,它們都安裝在引線框架上。雖然Simcenter POWERTESTER ? 1500A 能夠?yàn)閱蝹€(gè)封裝提供高達(dá) 1500A 的電流,但用于測(cè)量的加熱電流為 20A。所有測(cè)量均在 25° C 的冷板溫度下進(jìn)行,功率測(cè)試儀在測(cè)量過程中自動(dòng)捕獲數(shù)據(jù)。使用 Simcenter T3STER ? Master 軟件對(duì)數(shù)據(jù)進(jìn)行分析。測(cè)量前幾微秒內(nèi)發(fā)生的電瞬變是由電源從 20A 加熱電流調(diào)低到0.1A 測(cè)量電流引起的,通過內(nèi)置的“平方根” 方法進(jìn)行校正,該方法使用合適選定時(shí)間窗口內(nèi)的擬合平方根外推的曲線代替初始/ 寄生瞬變。

使用 JESD51-14 測(cè)量 θ JC 包括進(jìn)行兩次測(cè)量,一次是將樣品安裝在冷板上,樣品和冷板之間沒有潤(rùn)滑脂,另一次是使用潤(rùn)滑脂。

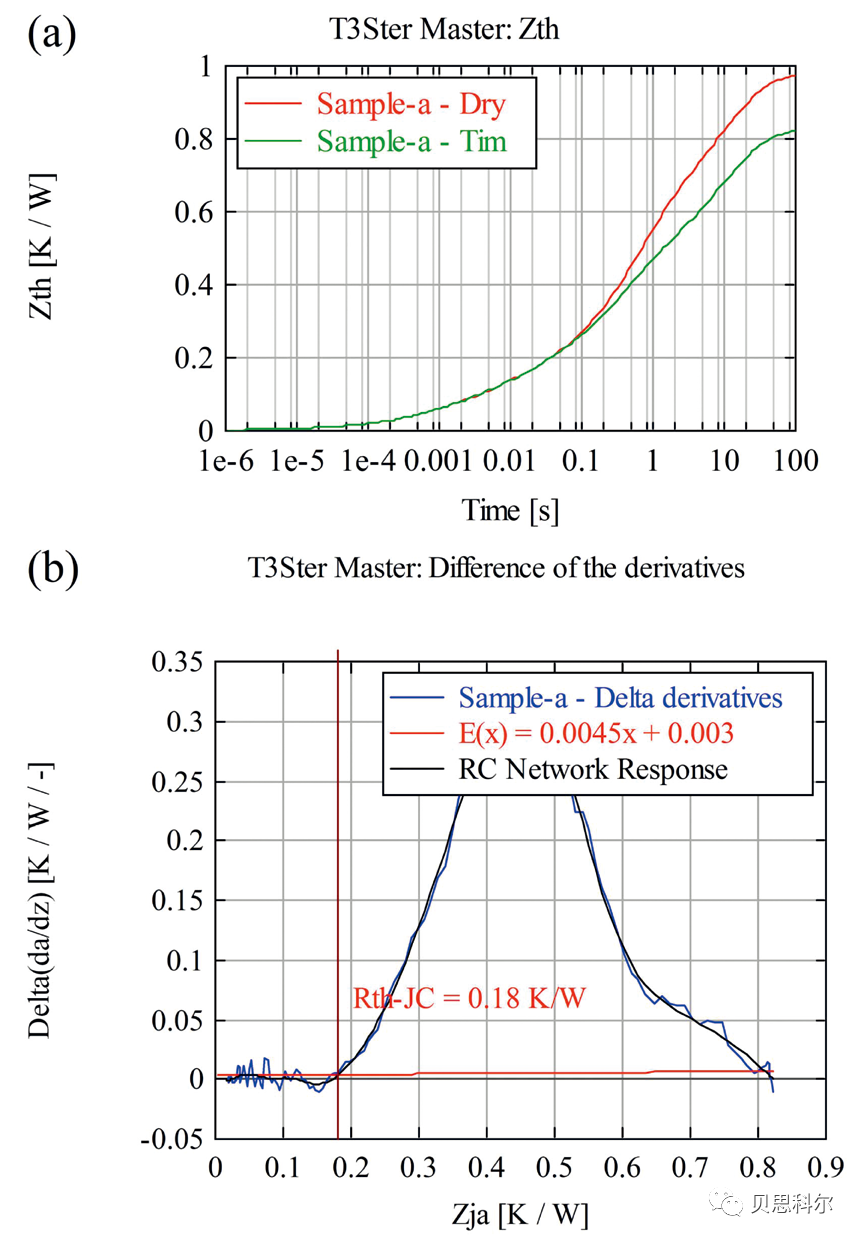

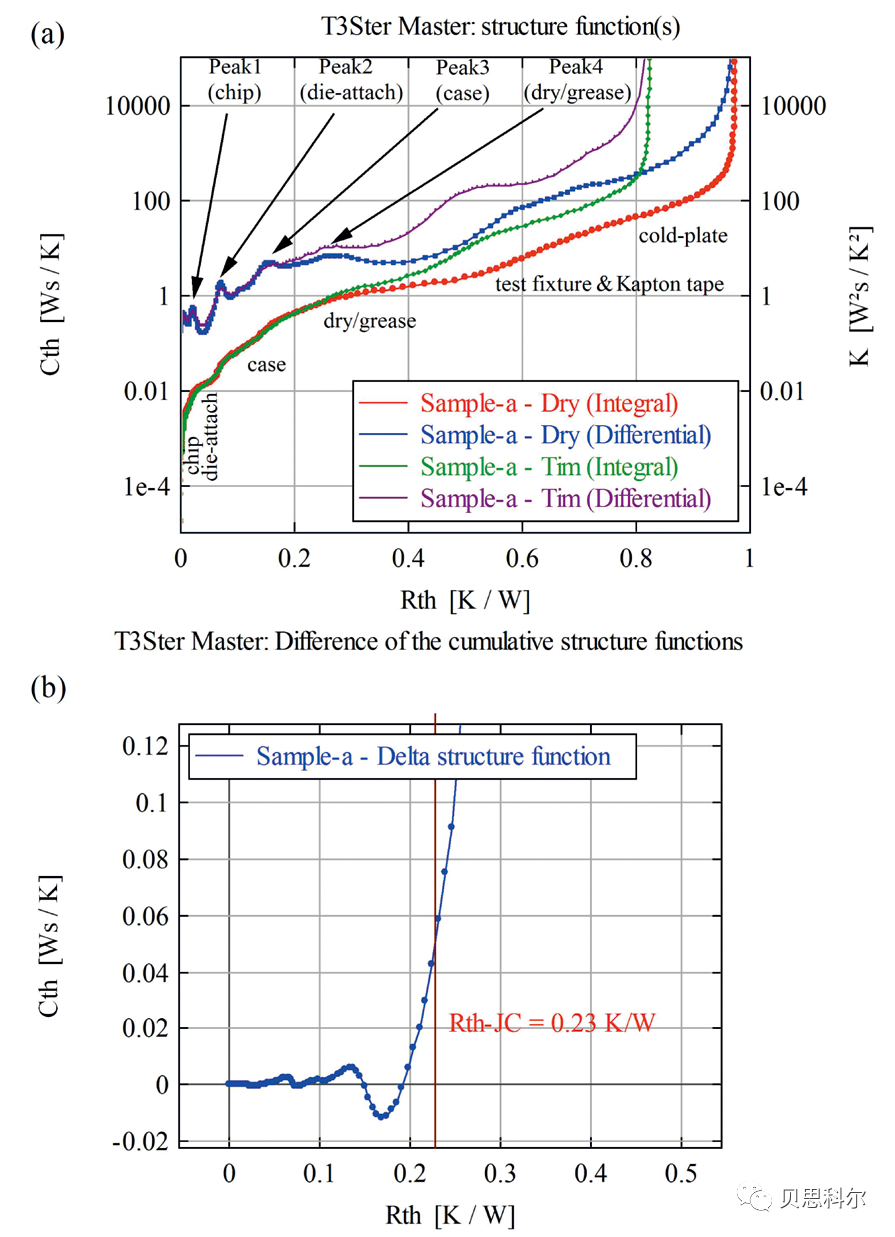

夾具和封裝的微觀粗糙度可抵抗干燥外殼的熱流,而TIM/ 潤(rùn)滑脂可最大限度地減少表面粗糙度并降低界面熱阻。因此,兩條曲線分離是由于兩次測(cè)量的熱路徑不同。一旦熱通量到達(dá)封裝- 夾具界面,即當(dāng)通量離開封裝外殼時(shí),兩條曲線就開始分離。兩條曲線的分割點(diǎn)表示 θ JC。然而,兩條曲線逐漸分開,而不是在一個(gè)明確的點(diǎn)上, 如圖 4(a)所示。因此,有必要更精確地定義時(shí)間上的分離點(diǎn)。如果使用曲線的導(dǎo)數(shù),則任務(wù)相對(duì)容易,如圖 4(b)所示。圖中的噪聲是通過將電阻- 電容梯形圖擬合到實(shí)驗(yàn)響應(yīng)中,并通過該梯形圖與瞬態(tài)開始和結(jié)束時(shí)擬合導(dǎo)數(shù)差值的趨勢(shì)線相交的位置來(lái)解釋。

圖 4:(a)使用和不使用潤(rùn)滑脂測(cè)量的樣品 a 的 Zth 曲線。(b)θ JC評(píng)估遵循樣品 a 的導(dǎo)數(shù)增量方法。基于 RC 網(wǎng)絡(luò)響應(yīng)的擬合曲線與趨勢(shì)線之間的交點(diǎn)的 x 值定義了 θ JC。

使用這種方法,對(duì)應(yīng)于樣品 a 的結(jié)殼熱阻的分離點(diǎn)為0.18K/W。用于對(duì)樣品的溫度與時(shí)間響應(yīng)進(jìn)行后處理的Simcenter T3STER Master 軟件提供了一種使用結(jié)構(gòu)函數(shù)評(píng)估結(jié)殼熱阻的替代方法。結(jié)構(gòu)函數(shù)是總累積熱電容的圖形表示,作為從熱源或驅(qū)動(dòng)點(diǎn)(結(jié)點(diǎn))測(cè)量的總累積熱阻的函數(shù),熱量通過封裝到達(dá)環(huán)境,在本例中為冷板。結(jié)構(gòu)函數(shù)是通過測(cè)量的瞬態(tài)響應(yīng)的數(shù)學(xué)變換來(lái)計(jì)算的,該變換涉及此處未描述的幾個(gè)步驟。

圖 5:(a) 樣品 a 的熱電容與熱阻的關(guān)系,顯示由于封裝外殼之間界面的變化而導(dǎo)致的熱路徑差異。

對(duì)于一維熱流路徑,熱結(jié)構(gòu)函數(shù)提供有關(guān)封裝器件內(nèi)各層的熱特性的信息。由于封裝器件中的缺陷而導(dǎo)致的熱流變化將改變結(jié)構(gòu)函數(shù)。換句話說,累積熱阻或累積熱電容的變化對(duì)應(yīng)于熱流路徑內(nèi)熱結(jié)構(gòu)或材料特性的變化。例如,如果外殼和夾具之間的熱界面從干接觸更改為潤(rùn)滑脂,則這兩個(gè)測(cè)量的結(jié)構(gòu)函數(shù)將在相應(yīng)點(diǎn)分離,分離點(diǎn)處的熱阻指示結(jié)殼熱阻的值,從而提供另一種測(cè)量方法。

無(wú)論使用哪種方法,清楚地確定曲線在哪一點(diǎn)上分離都具有挑戰(zhàn)性。在結(jié)構(gòu)函數(shù)方法的情況下,累積結(jié)構(gòu)函數(shù)的差異也有一些噪聲,因此同樣沒有曲線突然相互偏離的唯一點(diǎn)。雖然該方法在 JEDEC JESD51-14 標(biāo)準(zhǔn)中進(jìn)行了標(biāo)準(zhǔn)化和記錄,但它沒有包含明確的指南來(lái)選擇熱電容差值以判斷在該處曲線已分離。差值為曲線似乎分離時(shí)電容值的 5%。使用較低的值會(huì)導(dǎo)致結(jié)殼熱阻變化較大。

根據(jù) JESD51-14,低熱阻封裝通過結(jié)構(gòu)函數(shù)差分法獲得的結(jié)殼熱阻常受到數(shù)值效應(yīng)的阻礙;因此,在這種情況下,導(dǎo)數(shù)增量方法似乎更可靠,因?yàn)?TO-247 封裝具有低熱阻。

在選擇了最可靠的方法來(lái)測(cè)量結(jié)殼電阻后,安森美半導(dǎo)體能夠?qū)⒆⒁饬D(zhuǎn)向檢查芯片貼裝層中的孔洞對(duì)結(jié)殼電阻的影響。先前的研究發(fā)現(xiàn),與分布式或隨機(jī)孔洞相比,本質(zhì)上是大型聚結(jié)孔洞對(duì)散熱的影響更嚴(yán)重。為了提供高質(zhì)量和高性價(jià)比的產(chǎn)品,必須準(zhǔn)確了解孔洞的尺寸、位置和分布如何影響封裝的熱性能。

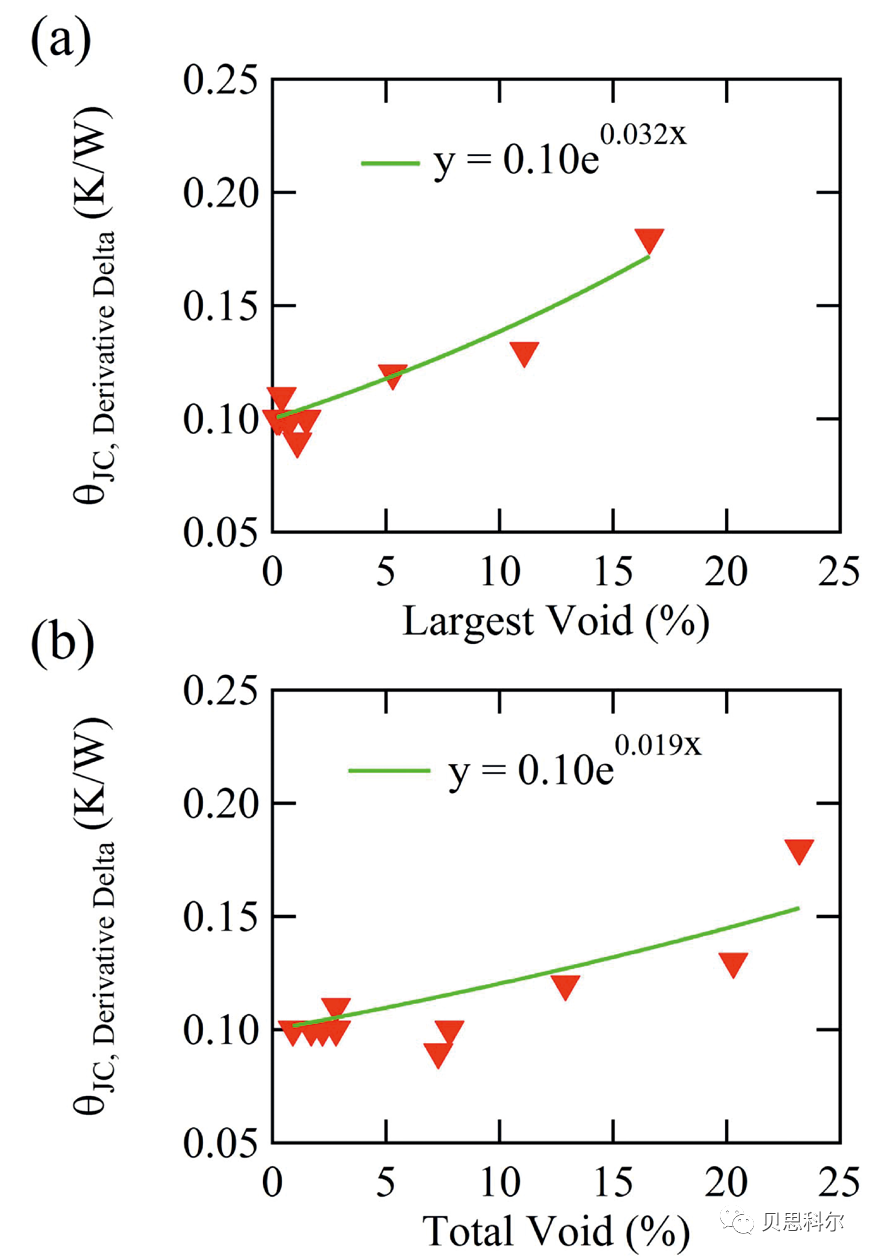

使用溫度與時(shí)間導(dǎo)數(shù)法測(cè)量了樣品 a 至樣品 j 的 10 個(gè)封裝,并測(cè)量了結(jié)殼電阻,結(jié)果與最大孔洞對(duì)應(yīng)的面積百分比和總孔洞百分比相關(guān)。圖 6 顯示了該分析的結(jié)果。

從結(jié)果可以清楚地看出,在約 10% 的總孔洞面積以下,孔洞的存在不會(huì)明顯增加結(jié)殼電阻。由此得出的結(jié)論是,包含在總孔洞百分比中的分布式孔洞不會(huì)顯著嚴(yán)重影響散熱。最大的孔洞尺寸(占總面積的百分比)對(duì)結(jié)殼電阻的影響更為明顯。

隨著最大孔洞百分比的增加,結(jié)殼熱阻的行為可以用指數(shù)擬合來(lái)描述,如圖6(a)所示。選擇指數(shù)函數(shù)是為了評(píng)估加速度行為的性質(zhì)。

圖 6:(a)和(b)結(jié)殼熱阻(對(duì)于 IGBT 芯片)分別占最大孔洞百分比和總孔洞百分比的函數(shù)。

很明顯,孔洞水平的增加會(huì)減少熱傳導(dǎo)的有效面積,這將導(dǎo)致結(jié)殼電阻的增加。對(duì)于較高的孔洞水平,隨著孔洞百分比的增加,阻力的變化可能是巨大的,并且很難預(yù)測(cè)確切的行為,因?yàn)樗Q于這些孔洞的分布方式。封裝器件的散熱受到芯片貼裝孔洞的嚴(yán)重影響,從可靠性的角度來(lái)看,最大限度地減少這些孔洞非常重要。最大的孔洞百分比對(duì)器件的熱阻影響最大。對(duì)二極管結(jié)殼電阻的測(cè)量表明,這不受 IGBT 芯片貼裝中的孔洞影響,這意味著二極管熱路徑與 IGBT 熱路徑無(wú)關(guān)。

審核編輯:湯梓紅

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27687瀏覽量

221456 -

IGBT

+關(guān)注

關(guān)注

1268文章

3830瀏覽量

249692 -

晶體管

+關(guān)注

關(guān)注

77文章

9744瀏覽量

138714 -

芯片貼裝

+關(guān)注

關(guān)注

0文章

7瀏覽量

6151

原文標(biāo)題:【技術(shù)文章】了解芯片貼裝熱性能

文章出處:【微信號(hào):BasiCAE,微信公眾號(hào):貝思科爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

貼裝技術(shù)的特點(diǎn)

貼裝技術(shù)原理與過程

PCB提高中高功耗應(yīng)用的散熱性能

元器件的貼裝性能

smt表面貼裝技術(shù)

如何提高PCB原型制造的貼裝質(zhì)量和貼裝效率

半導(dǎo)體集成電路芯片貼裝的方法有哪些?

貼裝技術(shù)特點(diǎn)

貼裝效率的改善

了解芯片貼裝熱性能

了解芯片貼裝熱性能

評(píng)論