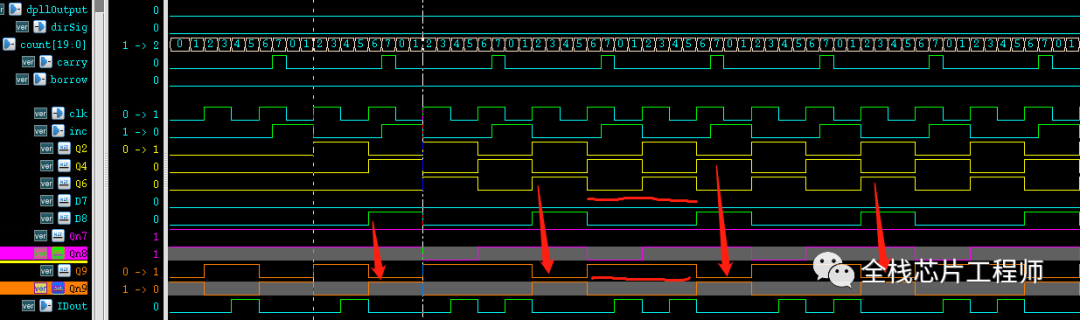

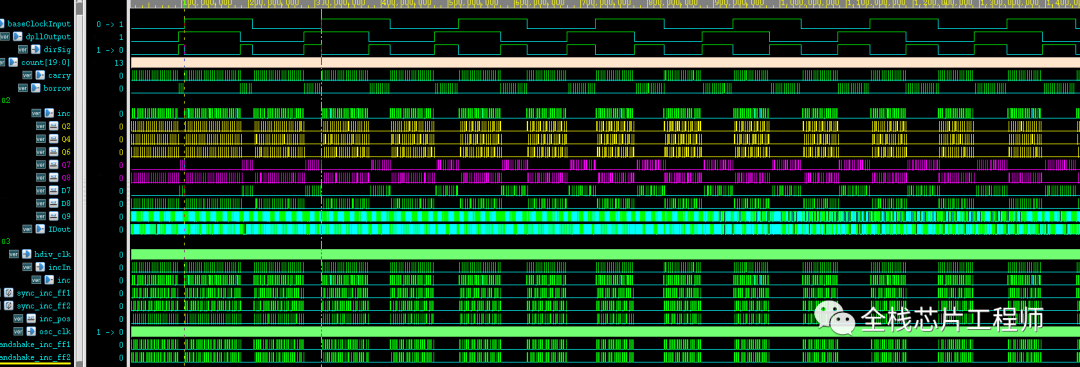

數字PLL中會利用到JK觸發器,JK觸發器的J=1,K=1時,JK觸發器輸出取反,即二分頻。

當有進位脈沖信號CARRY時,則在輸出的二分頻信號中插入半個脈沖,以提高輸出信號的頻率;

當有借位脈沖信號BORROW時,則在輸出的二分頻信號中減去半個脈沖,以降低輸出信號的頻率。

DRC、LVS run一下:

最近準備集成64位雙核RISCV處理器、LPDDR4、MIPI、ISP、VPU,開發一款多媒體SoC芯片,TSMC12nm工藝。數據涉密,架構開放討論。

歡迎加入【全棧芯片工程師】知識星球,手把手教你設計MCU、ISP圖像處理,從算法、前端、DFT到后端全流程設計。

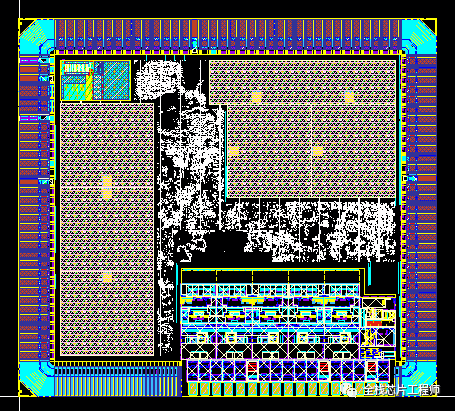

實戰MCU+ISP圖像處理芯片版圖

實戰ISP圖像算法效果

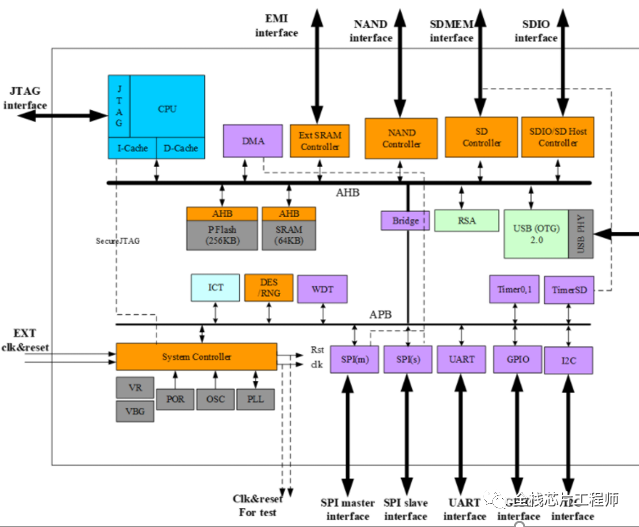

知識星球發起MCU項目啟動,大家一起參與MCU項目規格啟動討論,我把設計、驗證、DFT、后端的知識點全部羅列出來,大家一起來完善。

以項目驅動的方式介紹MCU芯片全流程設計的方法;提煉相關的檢查列表、signoff checklist的樣本;讓星球成員熟悉SoC架構、設計流程、開發進度、項目管理;

責任編輯:彭菁

-

soc

+關注

關注

38文章

4193瀏覽量

218758 -

觸發器

+關注

關注

14文章

2002瀏覽量

61284 -

MCU芯片

+關注

關注

3文章

253瀏覽量

11586

原文標題:數字PLL設計實戰(一)

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

EDA全流程的重要意義,以及國內EDA全流程進展

無線充電器方案XS016MCU+全橋/半橋驅動芯片

建立完善的硬件設計全流程解決方案

芯片制造全流程及詳解

芯片的制造全流程

芯片的制造全流程

數字芯片驗證流程

MCU芯片全流程設計的方法

MCU芯片全流程設計的方法

MCU芯片全流程設計的方法

評論