英特爾在巴塞羅那世界移動通信大會 (Mobile World Congress, MWC) 期間宣布推出全新英特爾 Agilex 7 FPGA 和 SoC (AGI 041),為在現代數據中心、通信和企業網絡中創建高速、低時延、安全的基礎設施提供支持。這些設備可用于開發先進的 SmartNIC 和基礎設施處理單元 (IPU),用以管理高速存儲和加速服務器,并可通過多個獨立的 PCIe 5.0 端口連接至多個服務器 CPU,同時支持 100G、200G 和 400G 以太網數據中心基礎設施連接。英特爾 AGI 041 FPGA 和 SoC 配備全新內核芯片,內含 400 萬個邏輯單元、335 Mbit M20K 模塊和兩個嵌入式 SRAM(eSRAM,位于可編程邏輯結構中),以及 4 個高性能 200G 加解密模塊(可組合使用,為 400G 和 800G 密碼操作任務提供支持)。全新設備旨在滿足數據中心基礎設施、云服務提供商 (CSP)、5G 通信服務提供商 (CoSP) 當前和未來的多種需求。

英特爾 Agilex 7 FPGA 和 SoC (AGI 041) 是英特爾 Agilex 7 FPGA I 系列 產品家族中的最新產品

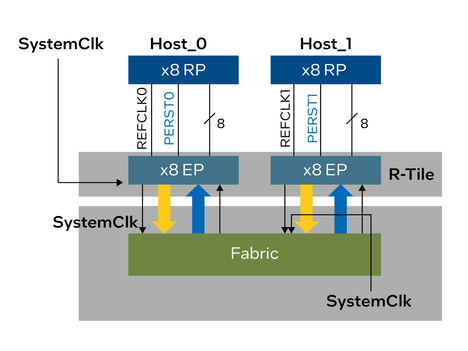

全新 I 系列產品還包含配備 116 Gbps SERDES 收發器的 F-Tile 和配備 PCIe 5.0 控制器和收發器的 R-Tile。AGI 041 FPGA 和 SoC 中包含的 R-Tile 支持多主機部署。全新設備中經過升級的 R-Tile 支持 Compute Express Link (CXL) 2.0,可通過獨立的 PCIe 端口與多個獨立的 CPU 主機連接。這些獨立的 PCIe 5.0 和 CXL 2.0 端口大大擴展了主機的連接性能,對于數據中心應用尤其有用。在這些應用中,一個 FPGA 或 SoC 可用作多達 6 個英特爾 至強 CPU 的加速器,并通過 6 組獨立的 PCIe 5.0 x8 端口進行通信。

英特爾 Agilex 7 FPGA 和 SoC FPGA (AGI 041) 中的 R-Tile 可通過完全獨立的 PCIe 5.0 和 CXL 2.0 端口支持多主機連接

全新設備將為英特爾的客戶與合作伙伴在要求 400GbE 帶寬的 IPU 應用中提供強大助力。英特爾數據中心與人工智能事業部執行副總裁兼總經理 Sandra Rivera 表示,IPU 和其他數據中心應用目前是英特爾 可編程邏輯器件增長最快的市場。

英特爾還在 MWC 期間展示了兩個 FPGA 演示案例,即大規模 MIMO (mMIMO) 白盒硬件開發平臺和加速虛擬蜂窩基站路由器解決方案:

支持 400G 的英特爾 eASIC N5X080 設備

英特爾 eASIC 設備屬于結構化 ASIC(一種介于 FPGA 和標準單元 ASIC 之間的中間技術),其單位成本和功耗較 FPGA 更低,上市時間 (TTM) 比標準單元 ASIC 更短,一次性工程 (NRE) 成本比標準單元 ASIC 更低。英特爾 eASIC N5X080 設備專為 SmartNIC 和 IPU 應用設計,內含 8.77M eCell 和 229 Mbit M10K 內存模塊,以及 1 MB Mega SRAM 內存。兩個 200G 以太網 MAC 及 8 個 53G 收發器,最高支持 400G 以太網連接。PCIe 5.0 控制器可用于多主機連接,每個控制器支持 x8 或 2 個 x4 插槽配置。這些功能特性與英特爾 Agilex 7 AGI 041 FPGA 的功能特性相似,一旦 FPGA 實現得到驗證,即可進入批量部署階段,并可經硬核化成為成本和功耗更低的英特爾 eASIC N5X080 設備。

基于英特爾 eASIC N5X080 架構的 ASIC 設備可支持 400G 網絡連接、PCIe 5.0 多主機連接以及額外 8MB 片上內存

基于英特爾 Agilex 7 FPGA AGF027/014 R24C 雙 F-Tile 封裝的 MIMO 白盒:

全新英特爾 mMIMO 白盒是面向英特爾 mMIMO 支持包的硬件開發平臺。mMIMO 白盒由英特爾 Agilex 7 FPGA 提供支持,每個 FPGA 配備 2 個 F-Tile,并且包括所有必要的前傳接口、具有集成數字前端 (DFE) 的數據轉換器和集成射頻前端 (RFFE)。mMIMO 白盒是 mMIMO 無線電應用綜合開發平臺的重要部分。

mMIMO 白盒支持控制平面 (C-Plane)、用戶平面 (U-Plane) 和同步平面 (S-Plane),包括 IEEE1588 和 SyncE,并具有精確定時協議 (PTP) 軟件堆棧和伺服功能,可滿足 O-RAN 增強型 O-RU 規范(包括對電信配置文件的全部和部分定時支持)。

作為開放平臺,該 mMIMO 白盒可與英特爾廣泛的 Open RAN IP 庫(包括 mMIMO 波束成形 IP)和其他第三方 IP 結合使用,以創建完整的 mMIMO Open RAN 無線電產品。功能多樣的 mMIMO 白盒可用于概念驗證、實驗室驗證、室內現場測試、有一定限制的現場試驗,或作為量產硬件的基礎。

英特爾 Agilex 7 FPGA,賦能基于英特爾 FPGA SmartNIC N6000-PL 平臺的英特爾 加速虛擬蜂窩基站路由器解決方案

眾多通信服務提供商不斷追求更高的可擴展性和運營效率。無線接入網 (RAN) 虛擬化是將這些理想功能帶入 5G 部署的一種方法。采用虛擬蜂窩基站路由器 (CSR) 是創建虛擬 RAN (vRAN) 的一種方法,可幫助通信服務提供商提高自身的服務變現能力。虛擬 CSR (vCSR) 在將流量傳輸回通信服務提供商的核心網絡之前,可在 1 個蜂窩基站中聚合來自 1 個或多個無線電塔的移動數據流量。英特爾 vCSR 解決方案還支持網絡切片,助力運營商進一步提高自身的服務變現能力。

在 MWC 期間,該端到端無線通信案例演示展示了英特爾 加速虛擬蜂窩基站路由器解決方案使用基于英特爾 Agilex 7 FPGA 的 SmartNIC N6000-PL 平臺的諸多優勢。英特爾 加速 vCSR 解決方案具有集成的 vRouter 功能 (vCSR),具有符合 O-RAN 的精確時序,同時可選配前傳網關 (FHGW) 集成和基帶加速功能。包括 SuperMicro、Kontron 和 WNC 在內的多家供應商均支持英特爾 加速 vCSR 解決方案。

演示中的 vCSR 集成 vRouter 功能,可處理 L2 流量管理和 L3 路由。由 N6000 SmartNIC 生成的基準定時參考時鐘 (PRTC) 可提供符合 O-RAN 的下層拆分、LLS-C3 定時同步。該解決方案支持瞻博網絡云原生路由器,該路由器提供商業級的高性能可擴展路由,為集成有英特爾所開發 MPLS 數據平面的路由平面提供先進的解決方案。

該案例演示重點展示了由 FPGA 實現加速的 vCSR 解決方案如何通過將網絡路由和控制堆棧移植至英特爾 Agilex 7 FPGA 的硬核處理器子系統 (HPS) 內核上,大幅降低數據路徑時延,釋放主機服務器的處理器內核,以支持更多創收功能。MWC 案例演示展示了 vCSR 能夠滿足 5G Class B 和 Class C 系統所需的定時精度,同時支持互操作性。由于該解決方案是以標準的開源應用編程接口 (API) 和非專有軟件為基礎,因此可避免供應商綁定風險,為通信服務提供商與其他客戶提供更多選擇,同時簡化網絡部署和故障排除。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21788瀏覽量

605088 -

英特爾

+關注

關注

61文章

10002瀏覽量

172130 -

數據中心

+關注

關注

16文章

4847瀏覽量

72290 -

Agilex

+關注

關注

0文章

13瀏覽量

3757

原文標題:英特爾? Agilex? 7 FPGA,助力創建高速、低時延、安全的數據中心和網絡基礎設施

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMD數據中心營收首超英特爾

AMD數據中心業務首超英特爾,Nvidia異軍突起

英特爾與百度共同為AI時代打造高性能基礎設施

英特爾數據中心XPU產品最新進展:預計2027年發布

英特爾OCI芯粒在新興AI基礎設施中實現光學I/O(輸入/輸出)共封裝

英特爾實現光學IO芯粒的完全集成

英特爾?至強?6能效核處理器:Intel 3開山力作,每瓦性能提升2.6倍

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

使用英特爾Agilex3和Agilex5器件構建下一代數據中心平臺管理方案

英特爾Agilex 7 FPGA,助力創建高速、低時延、安全的數據中心和網絡基礎設施

英特爾Agilex 7 FPGA,助力創建高速、低時延、安全的數據中心和網絡基礎設施

評論