遠程通信系統和遠程監控系統對信號傳輸有兩方面的要求:一方面要求接口靈活且有較高的數據傳輸帶寬;另一方面要求系統的傳輸距離遠。傳統接口如UART,USB,以太網等在傳輸帶寬和傳輸距離上均無法滿足要求。

低壓差分信號(LVDS)是一種低擺幅的差分信號技術。LVDS的恒流源模式及低擺幅輸出使傳輸速度可以從數百Mb/s到2 Gb/s以上。差分傳輸方式使LVDS信號對共模輸入噪聲有更強的抵抗能力。LVDS技術功耗低,100Ω的負載電阻功耗僅有1.2 mW。這些特點使得LVDS技術廣泛應用在許多要求高速度與低功耗的領域。

隨著半導體工藝進步,現場可編程邏輯陣列(FPGA)的性能和集成度在不斷提高,同時成本在下降。FPGA片內資源豐富且靈活性強。通過配置邏輯資源和I/O,可以生成支持各種標準的接口,適合完成接口間的通信工作。FPGA的可重構性使相同的硬件環境可以實現不同的功能,節約了系統升級和更改的成本。

1 系統構成及原理

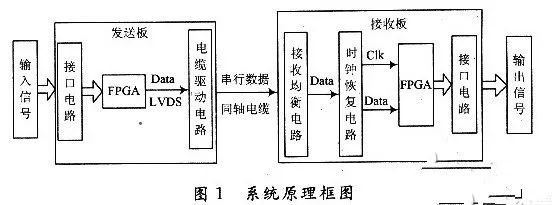

高速數據傳輸系統的原理框圖如圖1所示。整個系統由發送板、接收板和傳輸線三部分組成。

發送板主要由接口電路、FPGA和電纜驅動電路組成,完成的功能是將輸入的各種信號轉換為串行數據幀通過傳輸鏈路進行傳輸。接收板主要由接收均衡電路、時鐘恢復電路、FPGA和接口電路組成,實現將串行數據幀接收并恢復成原始信號的功能。傳輸線選用同軸電纜。與雙絞線相比同軸電纜的抗干擾能力強、傳輸距離遠,與光纜相比同軸電纜的成本低。同軸電纜適合本系統這種傳輸速率低于200 Mb/s,傳輸距離小于300 m的應用場合。

系統的輸入信號包括串口信號、網絡信號和并行視頻信號等。分別選用MAX232,RTL8201,SN74LVC4245等芯片組成接口電路,將輸入信號轉換為FPGA支持的LVTTL/LVCMOS電平信號,起到保護器件和增加信號驅動能力的作用。

接收板FPGA首先完成系統輸入信號的接收工作,再將異步時鐘域的信號轉換到統一的系統時鐘下,接下來將信號并串轉換并添加起始位、停止位和校驗位組成特定的幀格式,然后對其進行8 B/10 B編碼,通過差分I/O以LVDS電平輸出。接收板FPGA接收到串行信號后將信號解碼、解幀,抽取出原始數據進行恢復,通過相應的I/O將恢復后的信號輸出給各接口。

從FPGA直接輸出的LVDS信號在100 Mb/s傳輸速率下傳輸距離不足10 m,需要使用電纜驅動電路增加LVDS信號的驅動能力,同時使用接收均衡電路補償通過電纜傳輸后衰減的信號,達到加強系統長距離傳送能力的目的。

如果使用1根同軸電纜傳輸時鐘,其余傳輸數據,會因為無法保證這些電纜嚴格等長導致接收數據的建立時間和保持時間無法滿足后級電路的要求。另一方面,經過傳輸后時鐘信號的Jitter會增加,使FPGA內部的PLL無法鎖定時鐘。本系統電纜上傳輸的都是數據信號,接收端同步時鐘通過時鐘恢復電路從串行數據中還原。

2 系統的硬件設計

2.1 FPGA部分電路設計

系統選用Xilinx公司Spartan3系列的FPGA:S3C500E。它有10 476個邏輯單元,232個I/O,4個時鐘管理模塊(DCM),存儲器包括360 Kb的塊RAM和73 Kb的離散RAM。所有I/O可以組成92組LVDS差分對,輸入輸出速率高到622 Mb/s,所以系統不需要額外的電路實現LVDS接口。DCM模塊可以將輸入時鐘靈活的倍頻或降頻,工作頻率達到311 MHz。以上參數和性能不僅滿足當前的設計需求,而且為系統的升級保留了充足的設計余量。FPGA外圍電路包括時鐘部分和配置部分。時鐘使用電路板上的晶振提供,通過GCLK腳與FPGA相連。GCLK是專用時鐘引腳,這個腳的驅動能力強,到所有邏輯單元的延時基本相同。配置電路采用主動SPI模式。相比其他模式,主動SPI模式的外圍電路簡單、體積小、成本低。而且SPI FLASH的容量大,除了存儲配置文件,還可以存儲其他用戶數據。S3C500E的配置文件大小為2 Mb,本系統采用存儲量為16 Mb的M25P16作為配置存儲器。

2.2 傳輸部分電路設計

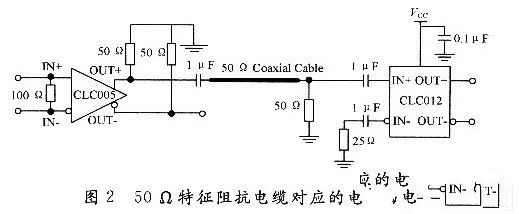

傳輸部分設計包括選擇同軸電纜和設計相應的發送接收電路。本系統選用的同軸電纜型號為SVY-50-3,成本低、性能好。這款電纜的特征阻抗為50 Ω,速率150 MHz時信號傳輸100 m的衰減為18.01 dB。它具有良好的屏蔽特性,可以在復雜的電磁環境中正常工作。電纜驅動電路和接收均衡電路分別選用National Semiconductor公司的芯片CLC005和CLC012。CLC005支持LVDS電平輸入,傳輸速率達到622 Mb/s,輸出信號峰一峰值從O.7~2 V。CLC012可以自動均衡頻率在50~650 MHz的信號。時鐘恢復器件選用CLC016,它的輸入信號來自CLC-012,輸出時鐘和數據接FPGA,恢復的時鐘在數據上升沿有效。CLC005和CLC012用于特征阻抗為75 Ω的傳輸系統,針對本系50 Ω特征阻抗的同軸電纜,需要改動外圍電阻配置,否則會因為阻抗不匹配引起信號反射,終導致信號傳輸質量下降。相應的配置方式如圖2所示。

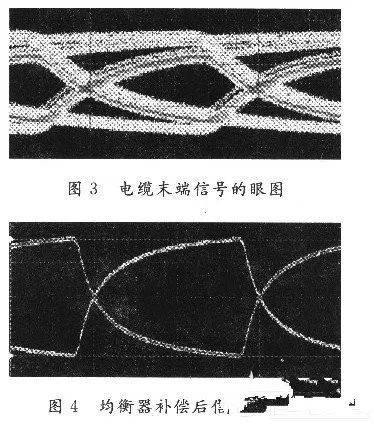

通過測試,此組傳輸器件可以驅動LVDS信號通過SVY-50-3型號電纜傳輸至少200 m。信號經過傳輸后,在電纜末端衰減嚴重,噪聲和抖動也較嚴重。此時信號眼圖如圖3所示,可以看出信號質量差。直接接收此信號,會產生信號電平誤判,而且信號的抖動將導致后級電路無法正常工作。接收均衡器CLC012自動為信號損耗提供補償后,信號上的噪聲和抖動均得到了改善,信號的眼圖如圖4所示。

LVDS驅動器由恒流源構成,因此需要做終端匹配。通常情況下在輸入端并聯100 Ω電阻從而滿足互聯系統要求的差分阻抗。在強噪聲環境下,交流耦合連接時可以采用戴維南終端匹配方式提供1.2 V的偏置電壓,同時滿足100 Ω差分阻抗的設計要求。具體方法是將LVDS的+/-端通過130 Ω電阻上拉至VCC,同時下拉82 Ω電阻到地,如圖5所示,電阻精度要求在1%。

2.3 電路PCB設計

在PCB設計過程中,要注意電路板的布局。模擬電路和數字電路需要分開,使用單點接地的方式相連。將邊沿速率變化快的VTTL/LVCMOS信號與LVDS信號布在不同信號層上,并用電源和底層隔開,減小耦合到LVDS線路上的串擾。LVDS走線要遵循以下規則:

(1)差分對兩根信號從芯片扇出后就盡量靠近(緊耦合),這樣有助于消除反射,確保耦合的噪聲是共模形式。

(2)對內信號的布線長度要保持一致,以減小信號延時,長度匹配控制在10 mil以內。

(3)對內信號保持固定的線間距,避免因為線間距變化導致差分阻抗不連續。

(4)差分對間盡量遠離,減少線間串擾,必要時在差分對間放置隔離用的接地過孔。

(5)盡量減少差分信號線上過孔的個數,避免走90°拐角,使用圓弧或者45°折線代替。

(6)LVDS信號不能跨平面分割,否則會因為缺少參考平面而導致阻抗不連續,要給LVDS信號設置完整的參考平面。

(7)匹配電阻盡可能靠近接收端。

3 系統的邏輯設計

3.1 時鐘部分設計

時鐘信號由電路板上40 MHz晶振提供。通過數字時鐘管理單元DCM鐘倍頻得到120 MHz的系統的工作時鐘。使用DCM模塊時,注意DCM的輸入和輸出需要通過BUFG單元與全局時鐘資源相連。全局時鐘資源使用全銅層工藝實現,并設計了專用時鐘緩沖與驅動結構,使全局時鐘到達芯片內部所有邏輯單元的時延和抖動都為。DCM在時鐘鎖定后使能LOCK信號,表示時鐘倍頻工作完成,使用這個信號作為FPGA內部其他邏輯的復位。

3.2 異步時鐘域變換

系統輸入信號工作在不同的異步時鐘域,需要在FPGA內部將信號變換到同一個時鐘域。

串口信號速度低,可以使用系統時鐘高速采集的方式。根據奈奎斯特抽樣定律,抽樣頻率大于2倍信號頻率,就可以從抽樣信號中無失真地恢復原信號。本系統使用高于5倍串口波特率的時鐘去采集串口數據。經過誤碼儀的大量測試,串口數據能夠被正確接收和恢復。

視頻信號是并行信號,采用高速采集的方法會增加數據量,不適合本系統。本系統采用雙口FIFO完成異步時鐘域轉換。S3C500E片內的Block RAM資源可以靈活的生成雙口FIFO,與普通邏輯單元生成的雙口FIFO相比,它的穩定性高,讀寫速度快,產生亞穩定狀態的概率小。雙口FIFO的輸入端連接系統輸入信號的時鐘和數據;在輸出端連接系統時鐘數據。雙口FIFO的讀取時鐘速度必須高于寫入速度,以避免FIFO存滿后溢出導致有效數據丟失。另一方面,慢時鐘域向快時鐘域轉換的時候,FIFO會出現讀取空的狀態,此時將取出無效數據(這些數據是FIFO中一個數據的重復)。無效數據通過串行數據幀傳輸到接收端,會導致恢復后輸出信號出現誤碼。所以系統將FIFO的空標志empty信號添加到數據幀,用于識別無效數據。

3.3 數據組幀及編碼

同步傳輸需要將原始數據組成數據幀再進行發送,即在數據間添加起始位、停止位和校驗位。數據幀的起始位過長會影響傳輸效率,過短會增加接收端識別的難度。本系統選用80 b為一幀,起始位為8 b,停止位為2 b,奇校驗位為1 b。接收端邏輯通過對多個數據幀分析后,定位數據幀的起始位。由于每幀數據長度固定,所以找到某一幀的起始位后可以周期性的計算出接下來各幀的起始位置,不再需要反復做識別工作。

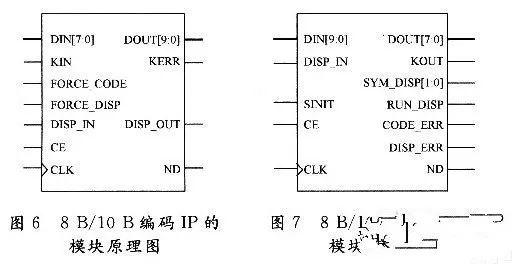

數據組幀后信號的平均位速率可能低于CLC012的工作頻率,不能直接用于傳輸,還需要對其進行8B/10B編碼。8B/10B技術是將8個數據位經過某種映射的機制轉化為10個數據位的字碼,可使發送的“O”、“1”數量保持一致,連續的“1”或“0”基本不超過5位。8 B/10 B編碼技術保證了傳輸的DC平衡,增加了信息傳輸的可靠性。系統使用Xilinx公司提供的8 B/10 B編碼和解碼IP核,減少了系統的開發周期,增加了系統的穩定性。8 B/10 B編碼及解碼IP的模塊原理圖如圖6和圖7所示。

4 結語

介紹了一種基于FPGA的高速通信系統,通過電纜驅動器和接收均衡器,拓展了LVDS信號的傳輸距離。經過測試,使用同軸電纜的傳輸距離達到200 m,單個通道傳輸速率達到120 Mb/s。FPGA的可重構性使系統靈活多變,可以適應不同的應用需求。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21753瀏覽量

604198 -

pcb

+關注

關注

4322文章

23119瀏覽量

398475 -

通信系統

+關注

關注

6文章

1195瀏覽量

53373 -

lvds

+關注

關注

2文章

1043瀏覽量

65845 -

高速通信

+關注

關注

0文章

25瀏覽量

10870

原文標題:基于FPGA的高速通信系統設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

采用MATLAB的FHSS通信系統設計與實現

ADS通信系統設計簡明教程

基于PC機與FPGA的脈沖雷達通信系統設計

基于FPGA的高速通信系統設計

基于FPGA的高速通信系統設計

評論