2.5 AXI總線

2.5.1 AXI總線簡介

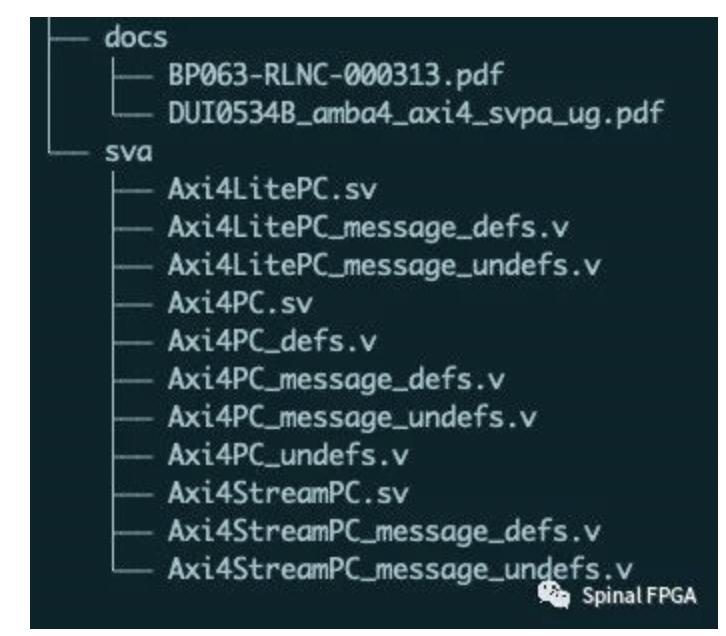

AXI作為AMBA總線協(xié)議的一部分,第一次出現(xiàn)在AMBA 3.0中。后面AMBA 4.0發(fā)布,AXI4出現(xiàn)了。AXI4總線和別的總線一樣,都用來傳輸bits信息(包含了數(shù)據(jù)或者地址)。AXI是一種面向高性能、高帶寬、低延遲的片內(nèi)總線。它的地址/控制和數(shù)據(jù)相位是分離的,支持不對齊的數(shù)據(jù)傳輸,同時在突發(fā)傳輸中,只需要首地址,同時分離的讀寫數(shù)據(jù)通道、并支持顯著傳輸訪問和亂序訪問,并更加容易進(jìn)行時序收斂。

AXI特點(diǎn)是單向通道體系結(jié)構(gòu),信息流只以單方向傳輸,簡化時鐘域間的橋接,減少門數(shù)量。當(dāng)信號經(jīng)過復(fù)雜的片上系統(tǒng)時,減少延時。支持多項(xiàng)數(shù)據(jù)交換。通過并行執(zhí)行猝發(fā)操作,極大地提高了數(shù)據(jù)吞吐能力,可在更短的時間內(nèi)完成任務(wù),在滿足高性能要求的同時,又減少了功耗。獨(dú)立的地址和數(shù)據(jù)通道。地址和數(shù)據(jù)通道分開,能對每一個通道進(jìn)行單獨(dú)優(yōu)化,可以根據(jù)需要控制時序通道,將時鐘頻率提到最高,并將延時降到最低。

AXI4總線有三種類型,分別是AXI4、AXI4-Lite、AXI4-Stream。AXI4是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解,AXI4-Lite是AXI4的輕量版。這里保留了memory-mapped的寫法,主要是為了與AXI4-Stream區(qū)分開。

可以這樣去理解memory-mapped,假設(shè)有master A, 和 slave B,A與B通過AXI4或者AXI4-Lite連接通訊,A可以把B這個外設(shè)看作A上的某個地址。當(dāng)A向B傳輸數(shù)據(jù)時,就等同于A向這個地址傳輸數(shù)據(jù)。AXI4-Stream與AXI4、AXI4-Lite不同, 它不需要地址通道。

2.5.2 AXI總線讀寫框架

1)AXI讀寫傳輸

AXI4 和 AXI4-Lite接口包含5個不同的通道:兩個讀通道和三個寫通道。每一個AXI傳輸通道都是單方向的。每一個傳輸都有地址和控制信息在地址通道(address channel)中,用來描述被傳輸數(shù)據(jù)的性質(zhì)。

- 兩個讀通道:讀地址通道(read address channel)、讀數(shù)據(jù)通道(read data channel)。

- 三個寫通道:寫地址通道(write address channel)、寫數(shù)據(jù)通道(write data channel)、寫響應(yīng)通道(write response channel)。

對于讀操作,主模塊通過地址通道發(fā)送讀傳輸?shù)刂罚瑥哪K通過讀數(shù)據(jù)通道返回給主模塊所需要的數(shù)據(jù)。

對于寫操作,主模塊通過寫地址通道發(fā)送寫傳輸?shù)刂罚⑼ㄟ^寫數(shù)據(jù)通道把數(shù)據(jù)發(fā)送給從模塊。而從模塊接受到數(shù)據(jù)后,需要通過寫響應(yīng)通道返回一個響應(yīng)給主模塊。

讀通道和寫通道是分開的,因此可以完成數(shù)據(jù)的雙向傳輸。此外AXI4能夠?qū)崿F(xiàn)burst傳輸,換句說就是,可以在一個地址后傳輸多個數(shù)據(jù),最多可以達(dá)256 字節(jié)。AXI4-Lite不支持burst傳輸。AXI4-Stream 只有一個通道,不需要地址,可以burst 傳輸無限的數(shù)據(jù)。

這5條獨(dú)立的通道都包含一個信息信號和一個雙路的VALD、READY握手機(jī)制。信息源通過VALID信號來指示通道中的數(shù)據(jù)和控制信息什么時候有效。目地源用READY信號來表示何時能夠接收數(shù)據(jù)。讀數(shù)據(jù)和寫數(shù)據(jù)通道都包括一個LAST信號,用來指明一個事物傳輸?shù)淖詈笠粋€數(shù)據(jù)。

讀和寫傳輸都有他們自己的地址通道,這地址通道攜帶著傳輸所必須的地址和信息。讀數(shù)據(jù)通道傳送著從模塊到主模塊的讀數(shù)據(jù)和讀響應(yīng)信息。讀響應(yīng)信息指明讀事務(wù)的完成狀態(tài)。寫數(shù)據(jù)通路傳送著主模塊向從模塊的寫數(shù)據(jù)。每八個數(shù)據(jù)都會有一個byte lane ,用來指明數(shù)據(jù)總線上面的哪些byte有效。寫響應(yīng)通道提供了設(shè)備響應(yīng)寫傳輸?shù)囊环N方式。這完成信號每一次突發(fā)式讀寫會產(chǎn)生一個。

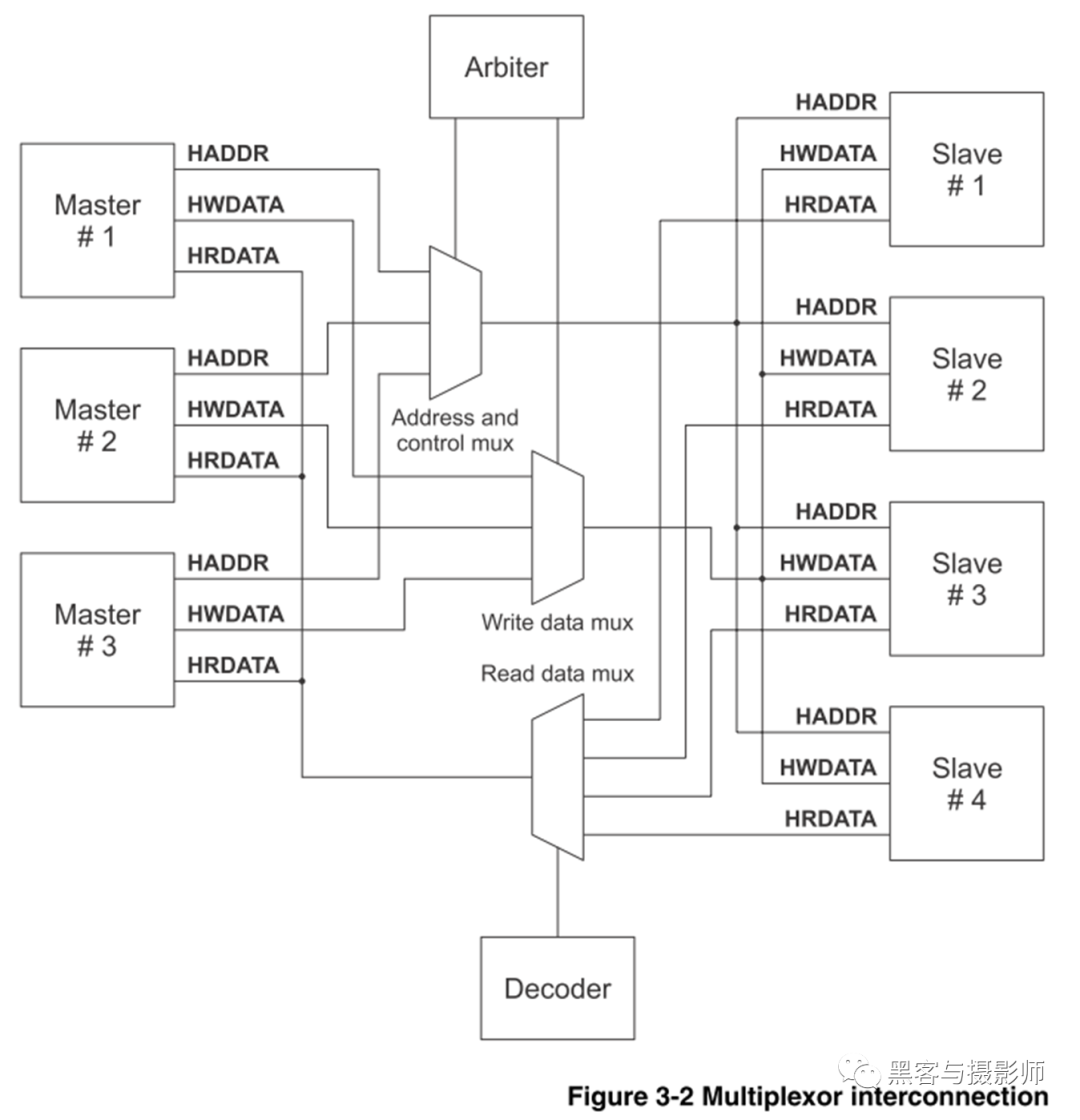

2)AXI典型連接圖

上圖是一個典型的一系列主設(shè)備與一系列從設(shè)備的連接系統(tǒng)。這些主設(shè)備與從設(shè)備通過interconnect連接在一起。

AXI協(xié)議提供單一的接口定義,主要包括:

- manager和interconnect之間。

- subordinate和interconnect之間。

- manager和subordinate之間。

AXI協(xié)議還提出了一個重要的概念,那就是 Register Slices,因?yàn)?上述五個通道之間沒有固定的關(guān)系,而且通道中傳輸?shù)男畔⑹菃畏较虻模敲纯梢钥梢栽谌我庖粋€通道中任意節(jié)點(diǎn) 插入register slices,通過插入register slice來抵消長路徑的延時,從而提高系統(tǒng)的性能。register slice的使用需要平衡 時鐘延時和最大工作頻率之間的關(guān)系。

2.5.2 AXI信號

2.5.3 握手信號

在了解AXI每個通道的定義信號后,下面對讀寫機(jī)制中的握手機(jī)制進(jìn)行說明。

五個獨(dú)立的通道均使用VALID/READY進(jìn)行握手,VALID由源端產(chǎn)生,用于指示源端發(fā)出的地址、數(shù)據(jù)、控制信息什么時候生效,READY則由目的端產(chǎn)生,用于指示源端發(fā)送信息什么時候被接收,只有當(dāng)VALID和READY同時為高時,才會表示本次傳輸完成。

VALID和READY握手可以分為下面三種情況:

- VALID早于READY生效。

- READY早于VALID生效。

- VALID和READY同時生效。

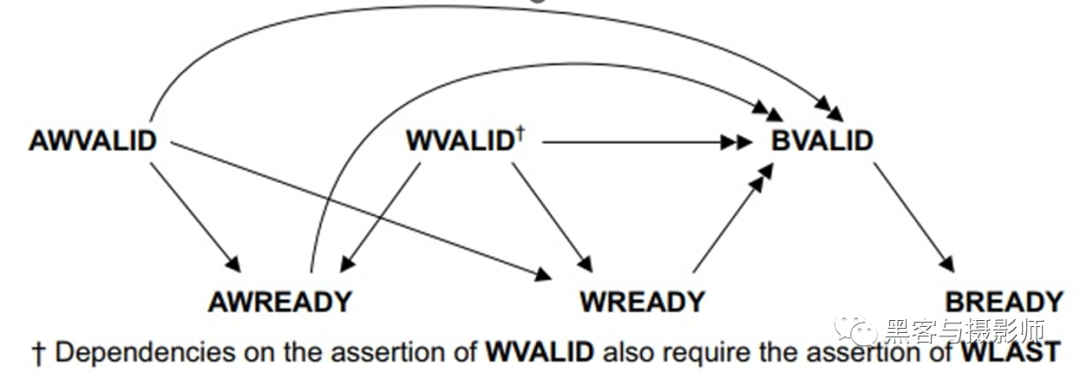

對于五個通道之間的關(guān)系,AXI協(xié)議僅定義了下面的關(guān)系:

- 寫響應(yīng)必須跟隨寫操作的最后一個傳輸。

- 讀數(shù)據(jù)必須緊跟讀地址數(shù)據(jù)。

除了上述兩點(diǎn)定義,AXI未定義其他任何通道間的關(guān)系,那么對于通道間的握手信號先后順序,必須按照特定的順序操作,不然很容易引起接口上的dead-lock。

具體的,讀操作時,對應(yīng)的讀地址通道和讀數(shù)據(jù)通道間握手信號的解釋如下: - ARVALID和ARREADY可以參考握手機(jī)制中的時序圖所示關(guān)系;

- RVALID和RREADY可以參考握手機(jī)制中的時序圖所示關(guān)系;

- RVALID必須在ARVALID和ARREADY同時生效后被使能;

寫操作時,對應(yīng)的寫地址通道、寫數(shù)據(jù)通道、寫響應(yīng)通道間的握手信號的解釋如下: - AWVALID和AWREADY之間的關(guān)系可以參考握手機(jī)制中的時序圖。

- WVALID和WREADY之間的關(guān)系可以參考握手機(jī)制中的時序圖。

- WVALID和AWREADY之間也可以參考握手機(jī)制中的時序圖。

- BAVALID和BREADY之間的關(guān)系可以參考握手機(jī)制中的時序圖。

- BVALID必須在WVALID和WREADY同時生效之后再被使能,同時必須是WLAST之后。

上述寫操作通道間握手順序是基于AXI3協(xié)議,AXI4/5在AXI3基礎(chǔ)上有改進(jìn),具體如下:

AXI4/5協(xié)議對于BVALID置位條件加強(qiáng)了,同時需要滿足WVALID/WREADY和AWVALID/AWREADY生效之后,且是在WLAST之后,才能被使能;

2.5.4 地址結(jié)構(gòu)

AXI協(xié)議傳輸數(shù)據(jù)時控制信息采用Start_address+Length形式,即Manager發(fā)出start_address、length以及burst類型、每次傳輸?shù)拇笮〉龋瑂ubordinate需要根據(jù)這些信息計(jì)算后續(xù)的地址,決定返回那些地址對應(yīng)的數(shù)據(jù)給manager;那么如何根據(jù)manager發(fā)送的address、length、burst類型、每個傳輸?shù)拇笮∵@些信息計(jì)算出manager需要訪問的地址,需要先看一下AXI協(xié)議所定義的地址結(jié)構(gòu);

2.5.5 burst length

AXI協(xié)議定義 ARLEN、AWLEN分別表示讀操作長度和寫操作長度,后面統(tǒng)一使用AxLEN統(tǒng)一表示。

AxLEN的含義:AxLEN+1 個傳輸(transfer)。

如AxLEN=7,AxSIZE=16byte(后面會講到),那么本次burst傳輸?shù)臄?shù)據(jù)量為:8*16=128byte。

AXI3協(xié)議定義AxLEN范圍:1~16;對應(yīng)的AxLEN使用4bit表示。

AXI4協(xié)議定義AxLEN范圍:1~256,對應(yīng)的AxLEN使用8bit表示。

對于Length還有如下幾點(diǎn)限制條件:

- 對于WARP類型的burst,burst length必須為2、4、8或者16。

- burst不能超過4KB地址邊界。

- burst不支持提前結(jié)束。

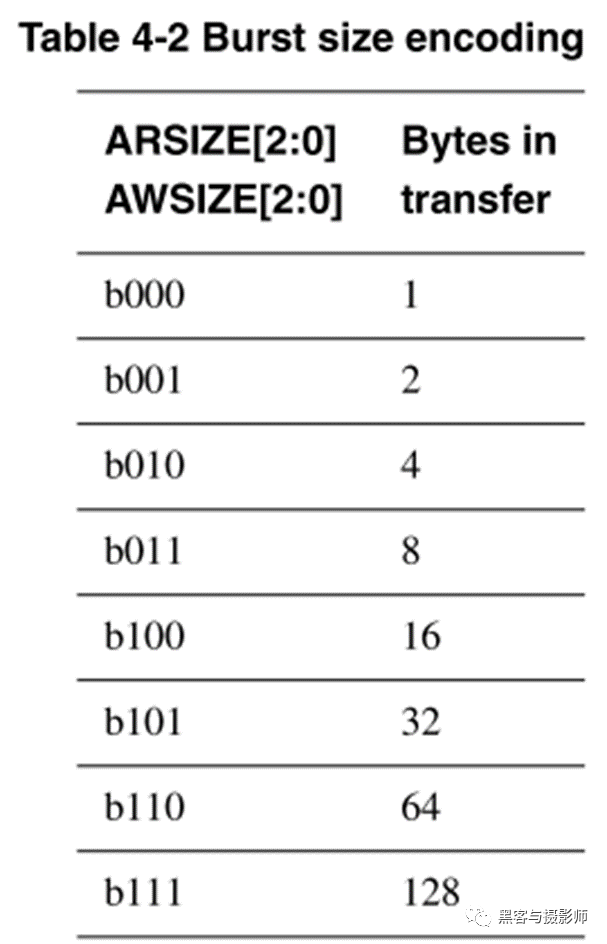

2.5.6 burst size

burst size表示每次傳輸(transfer)包含多少byte,分別定義了ARSIZE、AWSIZE分別表示讀傳輸、寫傳輸大小。

后面統(tǒng)一使用AxSIZE表示,AxSIZE使用3bit表示,具體的譯碼方式參見下圖:

AxSIZE指定的傳輸大小不能超過系統(tǒng)工作的數(shù)據(jù)位寬。

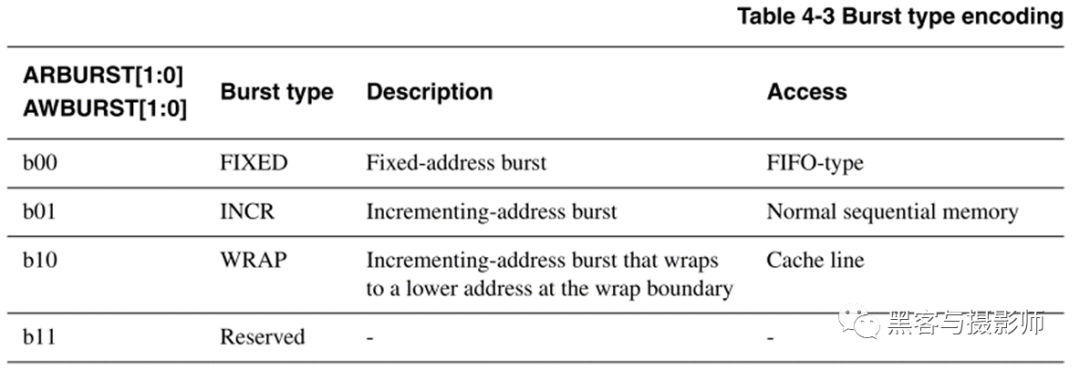

2.5.7 burst type

AXI協(xié)議規(guī)定下面三種burst類型:

同理,AxBURST為ARBURST和AWBURST的統(tǒng)稱,分別表示讀操作、寫操作burst類型。

- FIXED表示每次傳輸?shù)牡刂肥窍嗤牡刂罚S糜趯IFO的訪問。

- INCR表示每次地址都是按照遞增類型,下次傳輸?shù)牡刂?當(dāng)前傳輸?shù)刂?當(dāng)前傳輸?shù)拇笮 ?/li>

- WRAP表示每次地址都是按照遞增類型,只有在達(dá)到地址邊界的時候,會卷繞到低位的地址邊界開始,這種卷繞方式同AHB協(xié)議相同。

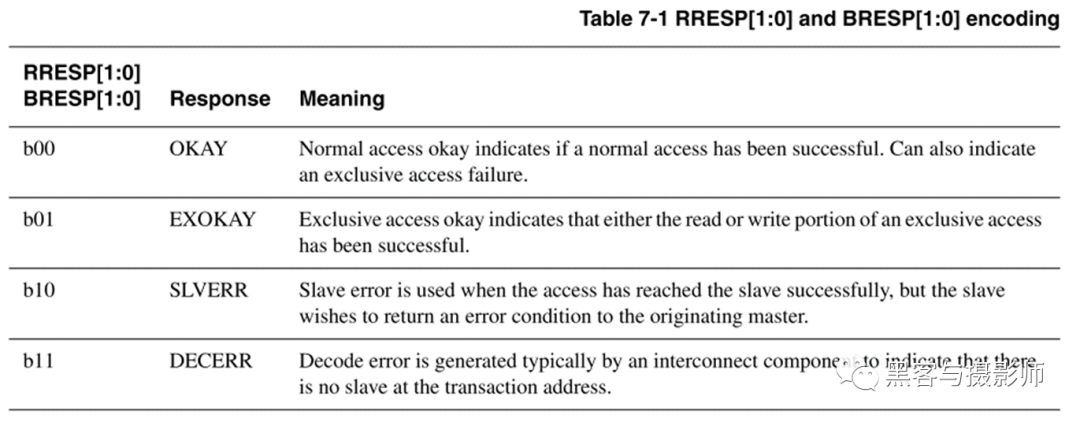

2.5.8 響應(yīng)類型

上面分析地址結(jié)構(gòu)、數(shù)據(jù)結(jié)構(gòu),接下來介紹一下響應(yīng)類型,BRESP、RRESP分別表示寫響應(yīng)、讀響應(yīng),后面統(tǒng)一使用xRESP表示,具體的譯碼規(guī)則如下:

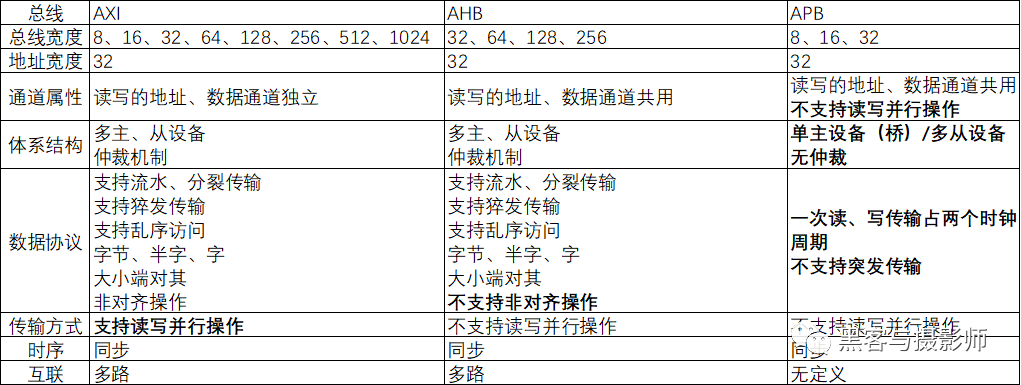

2.6 AXI、AHB、APB總線對比

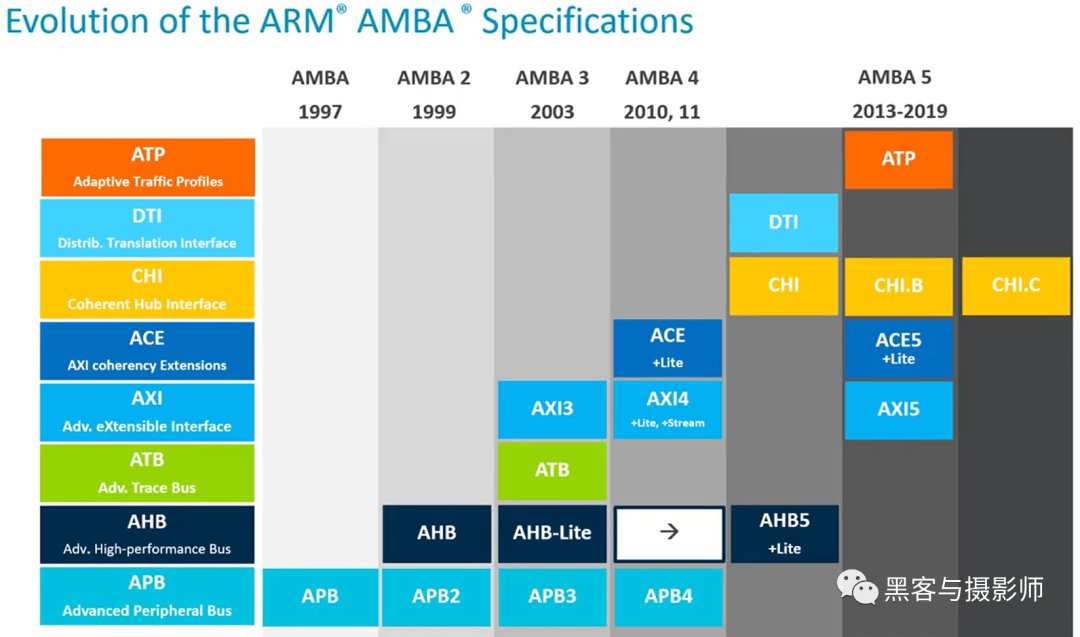

AHB:針對高效率、高頻寬及快速系統(tǒng)模塊所設(shè)計(jì)的總線,它可以連接如CPU、芯片上或芯片外的內(nèi)存模塊和DMA等高效率模塊。

APB:用在低速且低功耗的外圍設(shè)備,針對外圍設(shè)備作功率消耗及復(fù)雜接口的優(yōu)化。APB在AHB和低帶寬的外圍設(shè)備之間提供了通信的橋梁,所以APB是AHB的二級拓展總線。

AXI:高速度、高帶寬、管道化互聯(lián)、單向通道,只需要首地址、讀寫并行、支持亂序、支持非對齊操作,但連線非常多。

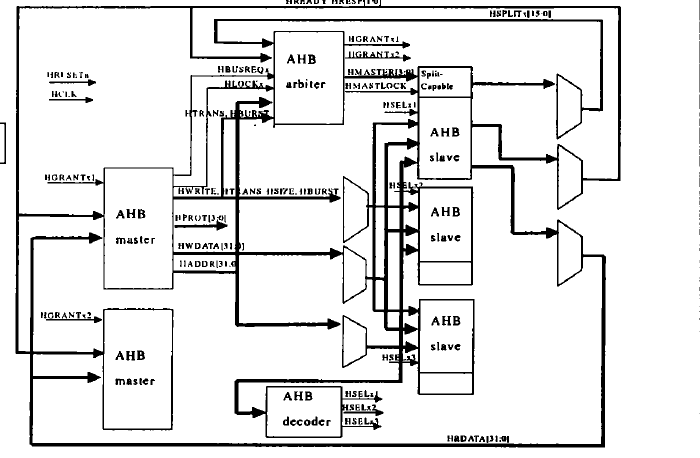

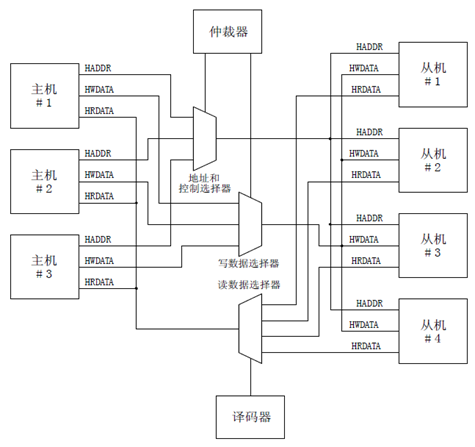

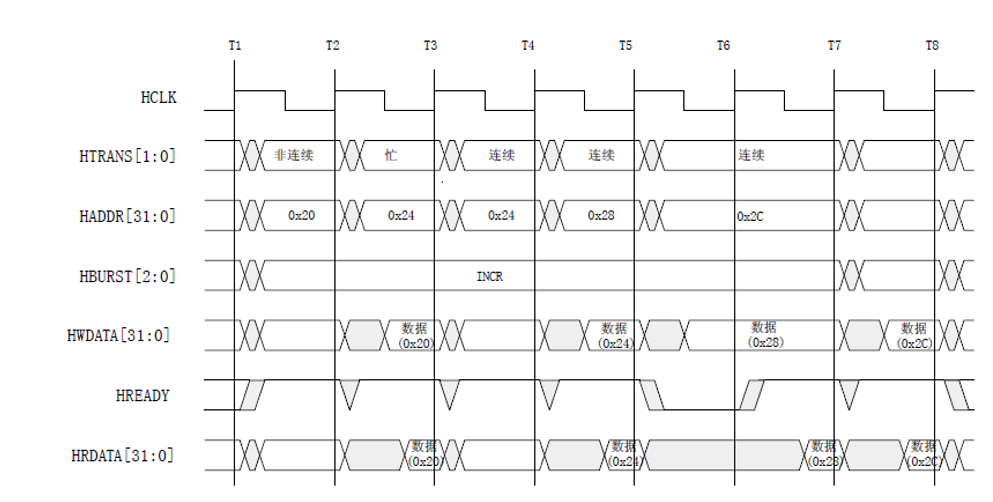

AXI、AHB、APB總線的性能對比分析:

AHB是高級高性能總線,AXI是高級可擴(kuò)展接口,APB是高級外圍總線。AHB和APB都是單通道總線,不支持讀寫并行。而AXI是多通道總線,總共分為五個通道,能夠?qū)崿F(xiàn)讀寫并行。AHB和AXI都是多主/從設(shè)備,且通過仲裁機(jī)制實(shí)現(xiàn)總線控制權(quán)的分配。而APB是單主設(shè)備多從設(shè)備,其主設(shè)備就是APB橋,不具有仲裁機(jī)制。在數(shù)據(jù)操作方面,AHB和AXI支持突發(fā)傳輸,APB不支持。此外,AXI支持?jǐn)?shù)據(jù)的非對齊操作,AHB不支持。

-

ARM

+關(guān)注

關(guān)注

134文章

9156瀏覽量

368555 -

總線

+關(guān)注

關(guān)注

10文章

2900瀏覽量

88280 -

AMBA

+關(guān)注

關(guān)注

0文章

69瀏覽量

15020

發(fā)布評論請先 登錄

相關(guān)推薦

AMBA AHB總線與APB總線資料合集

AMBA總線IP核的設(shè)計(jì)

AMBA總線概述(二)

ARM體系的特點(diǎn)與ARM的技術(shù)的簡介及AMBA總線的分析

基于AMBA總線介紹?

深度解讀AMBA、AHB、APB、AXI總線介紹及對比

介紹AMBA2.0總線

AMBA總線知識之AHB(上)

AMBA總線知識之AHB(下)

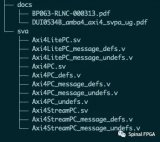

AMBA4 SystemVerilog Asseration驗(yàn)證

驗(yàn)證必備:AMBA4 SystemVerilog Asseration

深度分析AMBA總線工作原理4

深度分析AMBA總線工作原理4

評論