ARM所推出的AMBA4總線相對來講還是應(yīng)用廣泛的。無論是芯片設(shè)計(jì)里還是FPGA設(shè)計(jì)里,時(shí)常能見到AMBA4總線的身影。在驗(yàn)證領(lǐng)域,SystemVerilog Asseration還是一個(gè)很常見的驗(yàn)證手段。在Xilinx Vivado中有提供AMBA總線相關(guān)的Checker VIP,其內(nèi)部也是采用的SystemVerilog Asseration來實(shí)現(xiàn)。今天給大家推薦下ARM自家所推出的BP063 AMBA4 SVA組件。

》使用

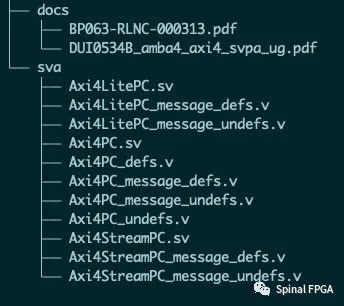

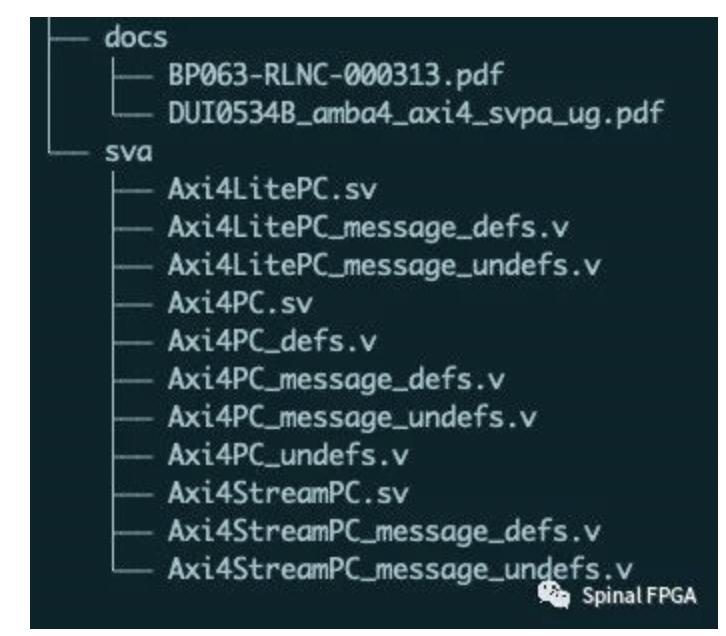

詳細(xì)的使用教程可以參照文件夾里面的BP063-RLNC-000313.pdf,這里就不在照本宣科的給從頭到尾講了,文檔中已詳細(xì)說明了如何使用及各種參數(shù)的配置。

》One More Thing

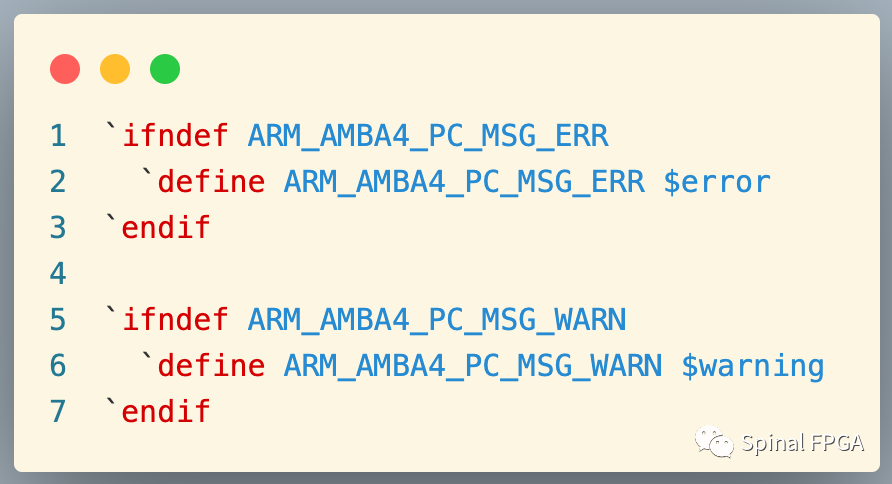

參照文檔基本可以保證能夠正常使用。對于SVA而言,其本質(zhì)無非是通過各種規(guī)則進(jìn)行檢查,若不符合情況則根據(jù)錯(cuò)誤等級進(jìn)行報(bào)錯(cuò)。在ARM AMBA4 SVA里面,出錯(cuò)后的錯(cuò)誤等級分為了$error和$warning兩種:

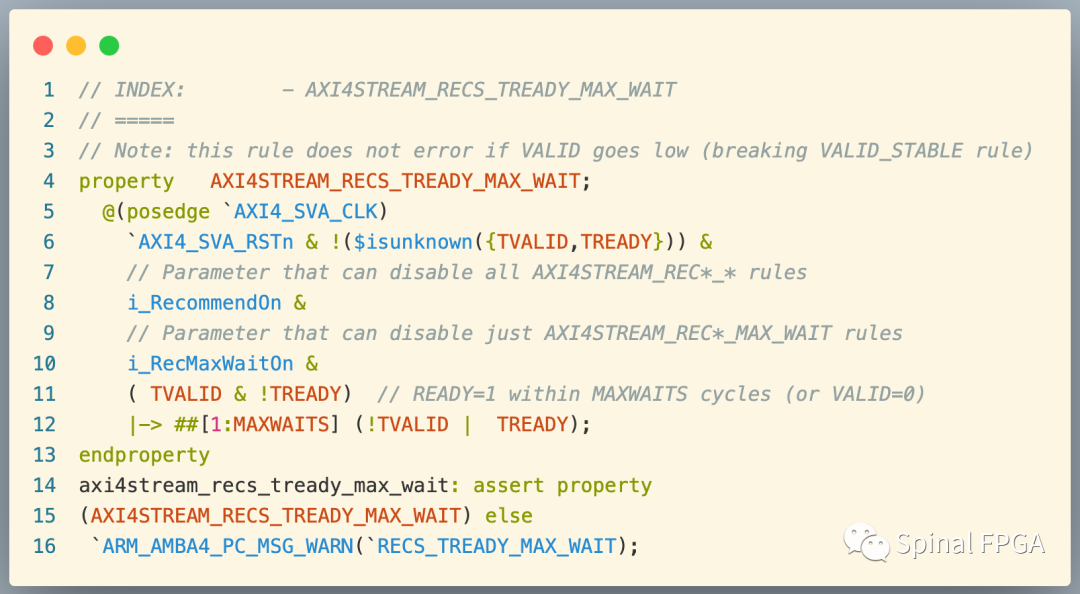

在仿真器執(zhí)行時(shí),對于$warning其只是打印信息,并不會(huì)影響仿真器繼續(xù)向下執(zhí)行。如果對于一些規(guī)則檢測,如果你覺得使用$warning并不符合需要,則可以手動(dòng)對源代碼進(jìn)行修改。例如下面對于ready超時(shí)的檢測:

這里當(dāng)仿真時(shí)不符合設(shè)計(jì)預(yù)期時(shí)會(huì)通過`ARM_AMBA4_PC_MSG_WARN來進(jìn)行$warning報(bào)警,如果需要出錯(cuò)時(shí)仿真立即停下來那么則可以將其替換更改為`ARM_AMBA4_PC_MSG_ERR。

審核編輯:劉清

-

ARM

+關(guān)注

關(guān)注

134文章

9156瀏覽量

368555 -

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26578 -

AMBA總線

+關(guān)注

關(guān)注

0文章

35瀏覽量

9593 -

SVA

+關(guān)注

關(guān)注

1文章

19瀏覽量

10146

原文標(biāo)題:驗(yàn)證必備:AMBA4 SystemVerilog Asseration

文章出處:【微信號:Spinal FPGA,微信公眾號:Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

SystemVerilog 的VMM驗(yàn)證方法學(xué)教程教材

什么是AMBA APB4與AMBA3 AHB-Lite1.0協(xié)議

在Arm AMBA協(xié)議集中AHB-lite可否使用

AMBA 4 ACE和ACE Lite協(xié)議校驗(yàn)器用戶指南

分層驗(yàn)證法在基于AMBA系統(tǒng)中的應(yīng)用

基于SystemVerilog語言的驗(yàn)證方法學(xué)介紹

Cadence驗(yàn)證IP為ARM AMBA 4協(xié)議大幅縮短驗(yàn)證周轉(zhuǎn)時(shí)間

SystemVerilog的正式驗(yàn)證和混合驗(yàn)證

4-AMBA VIP 編程接口

利用Systemverilog+UVM搭建soc驗(yàn)證環(huán)境

IEEE SystemVerilog標(biāo)準(zhǔn):統(tǒng)一的硬件設(shè)計(jì)規(guī)范和驗(yàn)證語言

驗(yàn)證必備:AMBA4 SystemVerilog Asseration

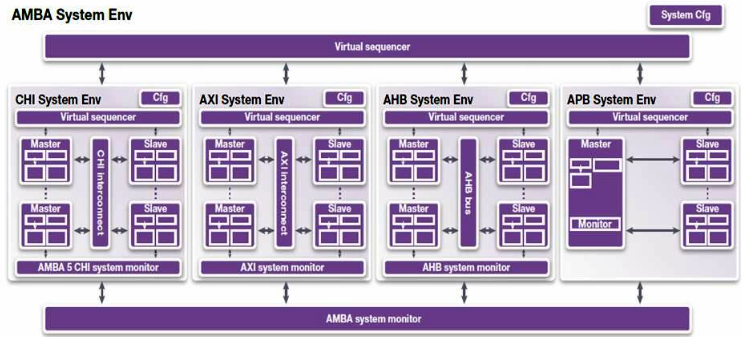

如何驗(yàn)證AMBA系統(tǒng)級環(huán)境

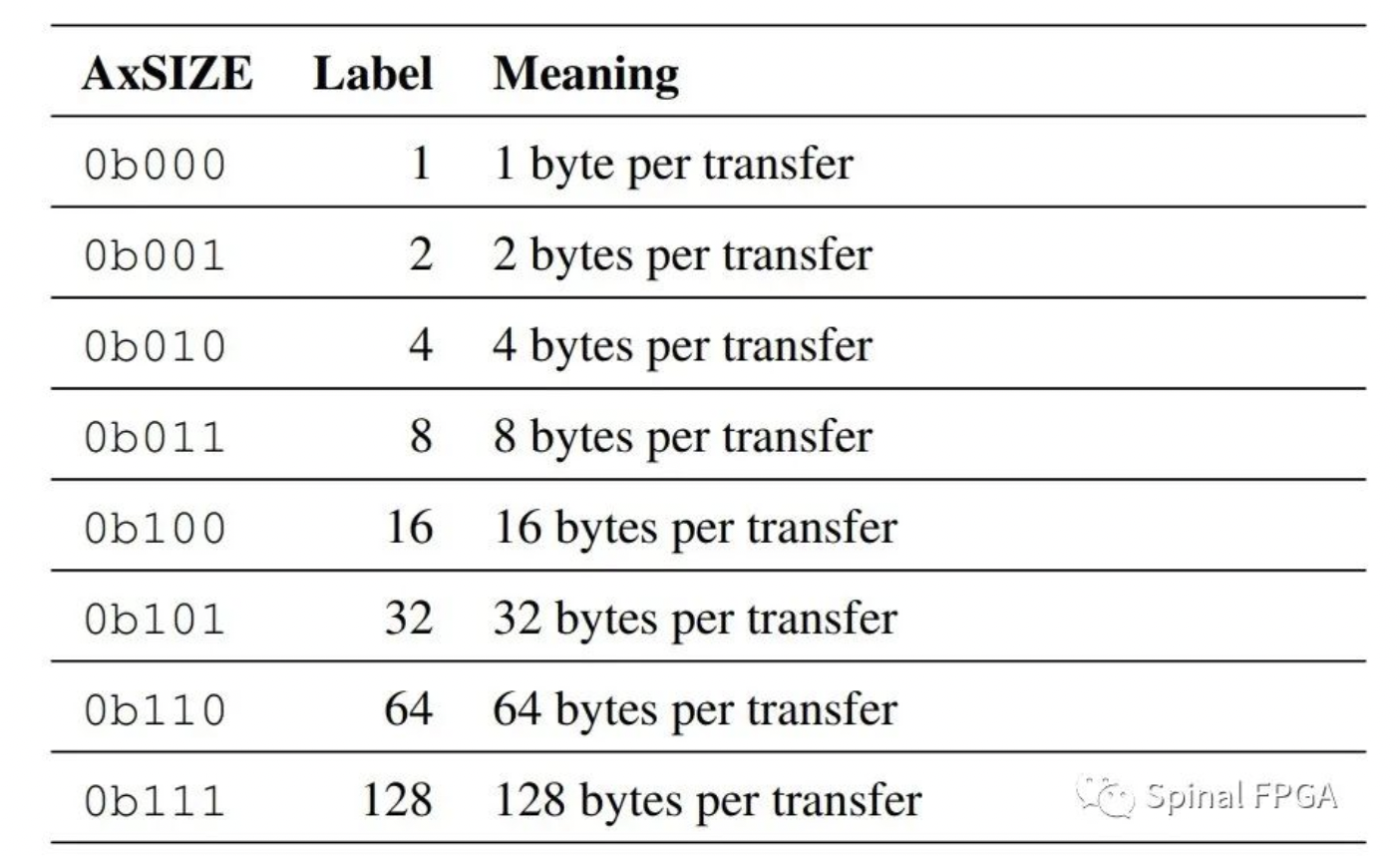

AMBA4—無聊的Narrow transfers介紹

AMBA4—“無聊的”Narrow transfers

AMBA4 SystemVerilog Asseration驗(yàn)證

AMBA4 SystemVerilog Asseration驗(yàn)證

評論