首先文章中提出的第一種方法是開環(huán)的主從控制,控制電流源對(duì)電容充電產(chǎn)生三角波,然后用峰值監(jiān)測(cè)和保持電路來(lái)取得三角波的峰值,然后把峰值除以2得到峰值的一半,然而再與主定時(shí)電容器的三角波進(jìn)行比較,從而得到主路delay 180°的地方發(fā)出去置位輔路。

在開環(huán)的主從控制中僅有主路的ZCD參與了周期刷新,輔路只是靠著周期一半的地方發(fā)出PWM,沒(méi)有ZCD的參與進(jìn)去,這樣做的目的是為了最簡(jiǎn)單的實(shí)現(xiàn)在BCM工作模式中變頻時(shí)保證180°的錯(cuò)相輸出,但是可能會(huì)導(dǎo)致輔路進(jìn)入CCM。

我用仿真軟件簡(jiǎn)單的模擬了這個(gè)idea,在峰值監(jiān)測(cè)和保持中我用的二極管整流對(duì)電容充電的方式來(lái)抓到主路定時(shí)電容上的三角波的峰值,然后在乘以0.5進(jìn)去,得到主路定時(shí)電容三角波的一半,在與主路進(jìn)行比較得到主路delay 180°的時(shí)間信號(hào),去置位輔路的PWM,可見:

輸出:

為了分析開環(huán)主從控制的穩(wěn)定性文章中引入了兩個(gè)擾動(dòng):一個(gè)主路TON的變化另外一個(gè)是輔助GS的開通點(diǎn)擾動(dòng),兩種情況都導(dǎo)致了開環(huán)的主從開始的時(shí)序會(huì)亂掉,會(huì)一直維持錯(cuò)誤狀態(tài),當(dāng)擾動(dòng)結(jié)束后不能修正這種錯(cuò)誤,導(dǎo)致輔路會(huì)進(jìn)入CCM。

雖然說(shuō)交錯(cuò)的BCM可以使用解耦磁集成的方式來(lái)做PFC電感,通過(guò)相同的磁性材料和繞線結(jié)構(gòu)來(lái)保證主從的電感量處于非常接近的水平,但是這樣并不能排除驅(qū)動(dòng)、負(fù)載變化、輸入變化時(shí)產(chǎn)生的擾動(dòng),以至于開環(huán)控制的主從并不能較好的應(yīng)用在實(shí)際的交錯(cuò)BCM系統(tǒng)上。

我們?cè)賮?lái)考慮使用鎖相環(huán)的閉環(huán)控制方法,將主從兩路的的ZCD的之間差控制在180°的時(shí)間,論文中提出使用RS觸發(fā)器來(lái)抓到兩者之間的時(shí)間差的方波,然后用濾波器來(lái)將方波低通成直流量,然后通過(guò)閉環(huán)控制的方法去調(diào)整輔路的定時(shí)器的電壓斜坡的上升速度。

在閉環(huán)調(diào)節(jié)的作用下逐漸達(dá)到相位保持在180°,這種方法我之前在這篇文章中有過(guò)介紹,是ETH的KOLAR團(tuán)隊(duì)進(jìn)行交錯(cuò)TCM的PFC做的實(shí)現(xiàn)方法,這個(gè)問(wèn)題就是閉環(huán)調(diào)節(jié)需要時(shí)間,在負(fù)載動(dòng)態(tài),開關(guān)周期長(zhǎng)度發(fā)生變化時(shí)候,重新回到穩(wěn)態(tài)工作點(diǎn)所需要的時(shí)間較長(zhǎng),對(duì)于PFC這種持續(xù)在變頻的應(yīng)用確實(shí)不是很好的方法。

大多數(shù)BCM的PFC控制器內(nèi)部有設(shè)置最長(zhǎng)周期時(shí)間,它是通過(guò)復(fù)位定時(shí)器來(lái)觸發(fā)PWM信號(hào),如當(dāng)輸出電壓非常接近設(shè)置電壓導(dǎo)致電感兩端沒(méi)有足夠的電壓去為電感電流放電,在當(dāng)前的周期結(jié)束后,ZCD沒(méi)有抓到則系統(tǒng)會(huì)進(jìn)到CCM運(yùn)行,并且系統(tǒng)的工作頻率由內(nèi)部的復(fù)位定時(shí)器的時(shí)間長(zhǎng)度來(lái)決定。

這種靠鎖相環(huán)去調(diào)節(jié)輔路的導(dǎo)通時(shí)間的方法并不能讓系統(tǒng)脫離出CCM模式。另外一個(gè)問(wèn)題是當(dāng)輔路進(jìn)入CCM,并且主從相位差小于180°,則閉環(huán)會(huì)讓輔路的導(dǎo)通時(shí)間增大來(lái)增大相差,由于加大了導(dǎo)通時(shí)間這樣只會(huì)繼續(xù)增加了電感電流,并不能使得系統(tǒng)脫離CCM模式,反而會(huì)繼續(xù)惡化系統(tǒng)的工況導(dǎo)致發(fā)生炸雞的情況。

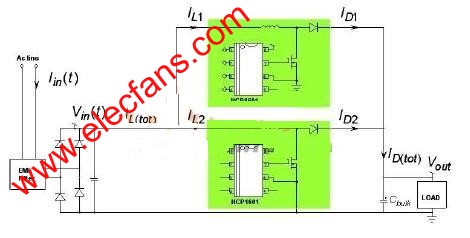

論文提出了一種新的實(shí)現(xiàn)方法,利用的是主從兩路相互影響的方法來(lái)解決BCM因?yàn)閿_動(dòng)進(jìn)入CCM不能自己退出的問(wèn)題。下圖是簡(jiǎn)化的實(shí)現(xiàn)方法,對(duì)于每個(gè)BCM的開關(guān)周期都進(jìn)行測(cè)量,并把它定為主從兩路的GS開啟到ZCD發(fā)生所持續(xù)的時(shí)間,并使用積分器上的電壓斜坡高度來(lái)表示開關(guān)周期的長(zhǎng)度。

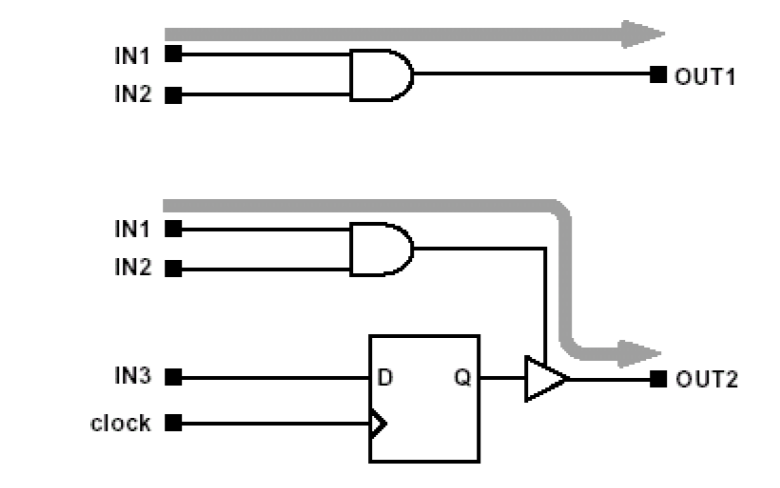

PS信號(hào)是兩個(gè)相位移動(dòng)的標(biāo)志,命名為PS1和PS2,它把主從兩路的開關(guān)周期的長(zhǎng)度的一半的時(shí)間點(diǎn)的標(biāo)志信號(hào)送給其它的通道。比如把主路上個(gè)周期的一半的時(shí)間長(zhǎng)度作為PS2給到輔路的PWM觸發(fā)器的置位輸入,并在邏輯上與輔路的ZCD2進(jìn)行AND操作。另外主路也是接受到輔路的上個(gè)開關(guān)周期一半的時(shí)間信號(hào)PS1與自己的ZCD1。

這里最關(guān)鍵是主從兩路的PWM觸發(fā)器的置位輸入是需要PS和ZCD一起置高才能開啟新的PWM輸出,這里是整個(gè)BCM變頻交錯(cuò)實(shí)現(xiàn)的關(guān)鍵。另外一個(gè)更重要的是這個(gè)控制邏輯中存在的輸入信號(hào)先后邏輯,比如是PS1先發(fā)生ZCD1后發(fā)生則PWM由ZCD1觸發(fā),對(duì)于的PFC通道工作在BCM模式。如果ZCD1先發(fā)生,PS1晚一點(diǎn)產(chǎn)生,在這個(gè)時(shí)間內(nèi)PWM觸發(fā)器的置位為低,主路PWM會(huì)繼續(xù)處于關(guān)閉。并因?yàn)殡姼幸呀?jīng)ZCD,此時(shí)是電感與Coss進(jìn)諧振的DCM狀。

當(dāng)PS1和ZCD1都到位后,再開啟主路PWM。不管是主路還是輔路都需要參考相對(duì)于的上個(gè)周期的長(zhǎng)度來(lái)進(jìn)行PWM開關(guān),當(dāng)ZCD1先發(fā)生而PS1還沒(méi)到位,說(shuō)明輔路在上個(gè)開關(guān)周期的長(zhǎng)度增長(zhǎng)了,為了避免主路因?yàn)殚_關(guān)長(zhǎng)度比輔路短一點(diǎn)可能會(huì)進(jìn)入CCM問(wèn)題,需要主路在DCM等待輔路的上個(gè)周期長(zhǎng)度一半的標(biāo)志信號(hào)PS1,用來(lái)實(shí)現(xiàn)兩路的周期長(zhǎng)度平衡。

可知當(dāng)系統(tǒng)處于完美的180deg交錯(cuò)的穩(wěn)態(tài)運(yùn)行時(shí),PS1和PS2都分別等于上個(gè)開關(guān)周期的一半位置,并且ZCD的發(fā)生位置和PS幾乎同時(shí)出現(xiàn),再發(fā)出PWM,也就是下圖中的(n-1)的位置的運(yùn)行情況。在(n)的位置輔路的導(dǎo)通時(shí)間增加了一點(diǎn)時(shí)長(zhǎng),PS1(n+1)是輔路上個(gè)周期(n)的長(zhǎng)度。

在同時(shí)主路的ZCD1(n+1)發(fā)生,此時(shí)主路的PWM置位所需的兩個(gè)信號(hào)都已經(jīng)到位分別是PS1(n+1)和ZCD1(n+1),主路發(fā)出PWW,并得到主路上個(gè)周期的時(shí)間長(zhǎng)度的一半PS2(n+1),可以看到PS2(n+1)先于ZCD2(n+1)產(chǎn)生。是因?yàn)樵?n)時(shí)刻,輔路的ON TIME增加了,使得電流過(guò)的電流變大所以ZCD發(fā)生所需要的時(shí)間要晚于主路的PS2(n+1),所以這里由ZCD2(n+1)來(lái)刷新PWM周期,輔路以BCM模式工作。

其實(shí)輔路的周期長(zhǎng)度已經(jīng)增加了PS1(n+2)的長(zhǎng)度是變化了,我們可以看到即使主路的ZCD1(n+2)已經(jīng)產(chǎn)生,但是還需要等到輔路的上個(gè)周期長(zhǎng)度PS1(n+2)走到,主路的PWM觸發(fā)的置位不能給出,主路的PWM全部OFF,進(jìn)入DCM狀態(tài)等待PS1(n+2),然后主路發(fā)出PWM開始新的周期,這里主路由于等待了一會(huì)輔路的周期長(zhǎng)度一半的標(biāo)志信號(hào)PS1(n+2),從ZCD到GS開啟的時(shí)間長(zhǎng)度也因?yàn)镈CM等待時(shí)間也變長(zhǎng)了PS2(n+2)這里就變得與輔路的PS1(n+2)一樣長(zhǎng)。

這里輔路也是ZCD2(n+2)先產(chǎn)生,要等待主路的開關(guān)周期長(zhǎng)度一半的標(biāo)志PS2(n+2),也進(jìn)入了DCM等待一下,然后再開啟的PWM。輔路的上個(gè)周期長(zhǎng)度一半的標(biāo)志PS1(n+3)恰好與ZCD1(n+3)同時(shí)發(fā)生,說(shuō)明控制電路把主路和輔路都增加了周期時(shí)長(zhǎng),使系統(tǒng)再次達(dá)到了BCM的穩(wěn)態(tài)。論文中還分析其他擾動(dòng)的工作情況,但是都因?yàn)橹髀泛洼o助相互的影響時(shí)間長(zhǎng)度來(lái)調(diào)整到新的穩(wěn)態(tài),解決了進(jìn)入CCM的問(wèn)題,我就沒(méi)有放出來(lái)。

上圖只是為了方便進(jìn)行原理性的分析,下圖論文給出了具體的邏輯實(shí)現(xiàn)電路:兩個(gè)相同參數(shù)的積分器和相同的峰值檢波除以2功能,目的是得到在電容上的斜坡電壓的一半的持續(xù)高電平波形,它用來(lái)表示主從的上個(gè)開關(guān)周期長(zhǎng)度的一半的時(shí)間長(zhǎng)度并送到PWM觸發(fā)器的S引腳的AND門上。它的分析過(guò)程可以參考上圖中的擾動(dòng)分析方法。

運(yùn)行波形:

測(cè)試實(shí)現(xiàn):

小結(jié):根據(jù)參考文獻(xiàn)的內(nèi)容學(xué)習(xí)了一種BCM交錯(cuò)PFC的時(shí)序邏輯的實(shí)現(xiàn)方法,并分析了其他實(shí)現(xiàn)的優(yōu)缺點(diǎn),對(duì)于理解BCM交錯(cuò)PFC的控制有非常有益的效用。

-

電容器

+關(guān)注

關(guān)注

64文章

6253瀏覽量

100035 -

二極管

+關(guān)注

關(guān)注

147文章

9695瀏覽量

167192 -

PWM

+關(guān)注

關(guān)注

114文章

5196瀏覽量

214523 -

BCM

+關(guān)注

關(guān)注

12文章

121瀏覽量

52968 -

電容充電

+關(guān)注

關(guān)注

0文章

68瀏覽量

8658

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Sequential Logic Design principles--時(shí)序邏輯設(shè)計(jì)原則

基于FPGA技術(shù)的RS 232接口的時(shí)序邏輯設(shè)計(jì)實(shí)現(xiàn)

邏輯設(shè)計(jì)是什么意思

中規(guī)模集成時(shí)序邏輯設(shè)計(jì)

時(shí)序邏輯設(shè)計(jì)原則 (Sequential Logic Des

時(shí)序邏輯設(shè)計(jì)實(shí)踐 (Sequential Logic Des

基于PLD芯片的時(shí)序邏輯設(shè)計(jì)與實(shí)現(xiàn)

交錯(cuò)式PFC的優(yōu)勢(shì)及解決方案

華為靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)

FPGA視頻教程之FPGA設(shè)計(jì)中時(shí)序邏輯設(shè)計(jì)要點(diǎn)的詳細(xì)資料說(shuō)明

華為FPGA硬件的靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)

BCM交錯(cuò)PFC的時(shí)序邏輯設(shè)計(jì)的藝術(shù)

BCM交錯(cuò)PFC的時(shí)序邏輯設(shè)計(jì)的藝術(shù)

評(píng)論