通常,對于具有高輸出電流的隔離式DC-DC電源應(yīng)用,主要使用同步整流器(特別是MOSFET)。高輸出電流還會(huì)在整流器上引入高di/dt。為了提高效率,MOSFET的選擇主要取決于導(dǎo)通電阻和柵極電荷。然而,寄生體二極管反向恢復(fù)電荷(QRR) 和輸出電容 (C開放源碼軟件).這些是影響 MOSFET 漏極上出現(xiàn)電壓尖峰和振鈴的關(guān)鍵參數(shù)。通常,隨著 MOSFET 的擊穿電壓額定值的增加,導(dǎo)通電阻也會(huì)增加。本文提出了一種數(shù)字控制的有源鉗位緩沖器,可以消除同步整流器上的電壓尖峰和振鈴。它還提供設(shè)計(jì)指南,以及隔離式DC-DC轉(zhuǎn)換器(如半橋和全橋拓?fù)洌┑钠渌麕讉€(gè)優(yōu)點(diǎn),同時(shí)提高可靠性并降低故障率。

介紹

始終需要具有高故障間隔時(shí)間 (MTBF) 的高可靠性電源。為了實(shí)現(xiàn)穩(wěn)健的設(shè)計(jì),可以使用開關(guān)的更高擊穿電壓額定值。但是,這會(huì)導(dǎo)致效率損失。因此,高效率和高可靠性在其應(yīng)用中有些對立。作為下一代電源解決方案的一部分,業(yè)界對高效隔離式DC-DC轉(zhuǎn)換器的需求一直穩(wěn)定。這要求在次級側(cè)使用同步整流器。整流器的額定值通常是器件兩端電壓尖峰的 1.2 至 1.5 倍。電壓尖峰是由漏感、寄生走線電感和整流器輸出電容(C開放源碼軟件),其諧振峰值可達(dá)整流器穩(wěn)態(tài)反向電壓的兩倍。被動(dòng)緩沖器可以以RC的形式使用1或剛果民盟2作為解決方案。雖然這些很受歡迎,但它們也是有損的,并導(dǎo)致效率略有下降。生成無損緩沖器的一些技術(shù)使用再生緩沖器,如 LCD3僅關(guān)注初級側(cè)開關(guān)的緩沖器,或僅在電源開關(guān)關(guān)閉期間而不是在接通期間使用 RC 緩沖器。其他技術(shù)4, 5利用泄漏能量驅(qū)動(dòng)小型高效轉(zhuǎn)換器饋入輸出電壓端子。但是,這需要更高的組件數(shù)。其他技術(shù)6已將有源鉗位緩沖器應(yīng)用于全橋相移拓?fù)洌韵?ZVS 軟開關(guān)應(yīng)用中初級側(cè)諧振電感引起的諧振,這在低占空比下具有局限性。

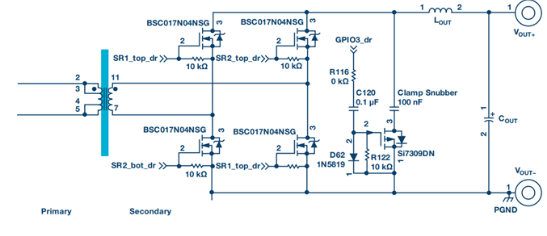

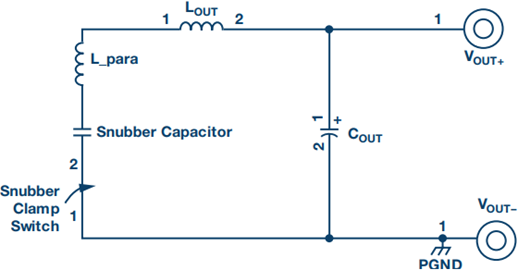

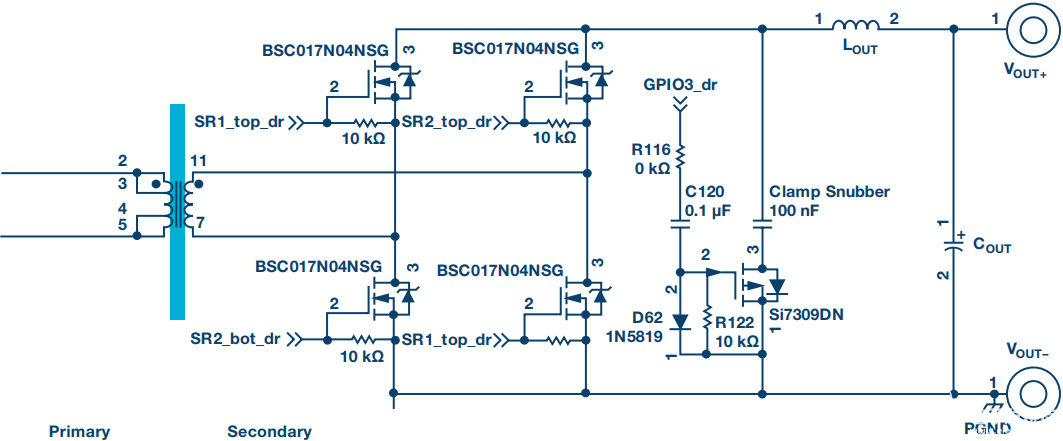

本文將仔細(xì)研究有源箝位緩沖電路及其數(shù)字實(shí)現(xiàn),它可以防止電壓偏移,特別強(qiáng)調(diào)消除MOSFET中寄生二極管的反向恢復(fù)損耗,這提供了其他一些額外的好處。轉(zhuǎn)換器功率級(僅次級側(cè))的原理圖如圖1所示。

圖1.功率轉(zhuǎn)換器的次級側(cè)顯示有源箝位。

圖1所示為隔離式DC-DC轉(zhuǎn)換器的副邊。次級側(cè)由連接到變壓器的H橋形式的同步整流組成。此外,還有輸出濾波電感器(L外)和輸出濾波電容(C外).有源箝位開關(guān)是P溝道MOSFET,用于電平轉(zhuǎn)換柵極信號的柵極驅(qū)動(dòng)由電容和二極管組成。

高頻等效電路

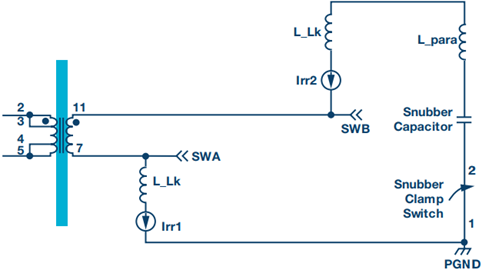

在高頻視圖中,大電感和大電容器分別被認(rèn)為是開路和短路的,而電路分析僅使用寄生和諧振電感和電容。這種方法可以簡化電路以分析交流電流。這在諧振拓?fù)浜蜕婕熬彌_器的情況下特別有用,因?yàn)楦哳l電流會(huì)在緩沖期間選擇阻抗最小的路徑。

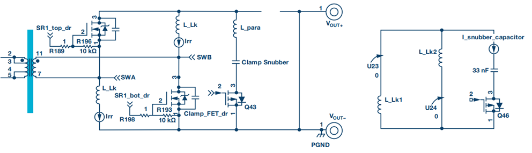

電路的交流圖如圖2所示。輸出濾波電感和輸出濾波電容分別開路和短路。MOSFET的輸出電容和漏感保持電路中不變。重點(diǎn)是轉(zhuǎn)換器的次級側(cè),因?yàn)槌跫夒妷涸炊搪罚瑢Ψ治鰶]有貢獻(xiàn)。

圖2.(左)電源轉(zhuǎn)換器次級側(cè)的交流視圖,顯示有源箝位。(右)簡化的交流視圖。

同步FET的有源箝位電路的工作原理

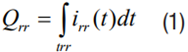

在分析中,假設(shè)緩沖電容器足夠大,以保持其兩端的恒定電壓。在續(xù)流間隔期間(圖 1 中 SR2 和 SR3 均導(dǎo)通),所有四個(gè)次級開關(guān) (MOSFET) 均導(dǎo)通。由于上升和下降時(shí)間有限,以及柵極驅(qū)動(dòng)信號傳播延遲的變化,同步整流器信號之間總是存在很小的死區(qū)時(shí)間。在此死區(qū)時(shí)間內(nèi),MOSFET 的寄生體二極管導(dǎo)通以實(shí)現(xiàn)續(xù)流。在此之后是開關(guān)周期的下半部分,初級MOSFET的另一支路被點(diǎn)火。這會(huì)導(dǎo)致變壓器繞組兩端的極性發(fā)生變化,并關(guān)閉同步整流體二極管。但是,只要反向恢復(fù)電荷(QRR) 未耗盡。方向如圖 2 所示。這個(gè)QRR被視為通過變壓器反射到初級側(cè)的過大電流,作為前沿尖峰。這也會(huì)導(dǎo)致同步 MOSFET 漏極端子上的電壓尖峰。反向恢復(fù)費(fèi)用的大小由下式給出:

圖3.

圖 4a.在TRR間隔期間操作反向恢復(fù)能量捕獲。

圖 4b.負(fù)載中釋放的能量。

由漏電流和走線電感(極性如圖2所示)引起的電壓尖峰被有源箝位緩沖器吸收。主動(dòng)緩沖開關(guān)可在 Z 軸時(shí)打開與寄生二極管導(dǎo)通后。但是,當(dāng)有源箝位緩沖器導(dǎo)通時(shí),緩沖器電容器吸收反向恢復(fù)電流,并將捕獲的能量再循環(huán)到次級電橋和負(fù)載中。由于通過緩沖電容器的凈電流為零,因此只要轉(zhuǎn)換器在穩(wěn)定狀態(tài)下工作,它就會(huì)保持電荷平衡。

設(shè)計(jì)指南

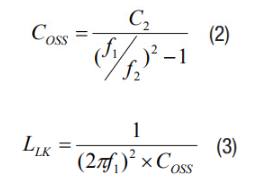

1. 漏感的估算

在沒有緩沖器的情況下操作轉(zhuǎn)換器并測量諧振頻率和周期(f1) 同步 MOSFET 漏極上的振鈴電壓尖峰。此外,測量初級電流波形上的前沿尖峰(應(yīng)等于tRR).要估算漏感,請放置電容器的已知值(C2) 至少比 MOSFET 的漏極源極電容大一個(gè)數(shù)量級。測量振鈴頻率(f2) 并計(jì)算電容 (C開放源碼軟件)和泄漏(L李克)電感使用以下公式計(jì)算:

2. 有源鉗位緩沖電容器的選擇

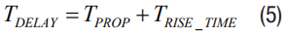

選擇至少是同步 MOSFET 輸出電容 10 至 100 倍的緩沖電容器。這是因?yàn)橛性淳彌_開關(guān)將有一個(gè)低阻抗路徑。但是,緩沖電容器的選擇必須符合:

其中 Ts是切換周期。

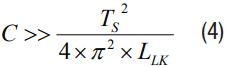

以如下所示的小延遲打開主動(dòng)鉗箍緩沖器:

這兩個(gè)項(xiàng)是驅(qū)動(dòng)器的傳播延遲和初級MOSFET的驅(qū)動(dòng)器信號上升時(shí)間。該時(shí)序至關(guān)重要,因?yàn)楸仨毑东@MOSFET體二極管的整個(gè)反向恢復(fù)。這個(gè)時(shí)間取決于體二極管的反向恢復(fù)特性(QRR, tRR我RR),并可能隨器件中的溫度、負(fù)載電流和反向電壓等因素而變化。定時(shí)延遲和緩沖導(dǎo)通時(shí)間可以針對開關(guān)的不同特性進(jìn)行優(yōu)化,使用上述精細(xì)分辨率設(shè)置。

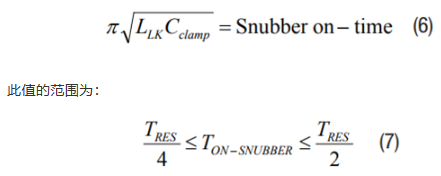

確定箝位電容尺寸的另一種方法是使用以下公式。它基于漏能量傾倒到箝位電容器中的諧振周期。

為避免在第 1 點(diǎn)觀察到過多的振鈴,導(dǎo)通時(shí)間應(yīng)最多為一個(gè)或兩個(gè)共振周期,否則會(huì)出現(xiàn)過度和連續(xù)的振鈴。或者,緩沖器的導(dǎo)通時(shí)間可以近似于上述第 1 點(diǎn)中觀察到的前緣尖峰的導(dǎo)通時(shí)間(例如 tRR).過長的時(shí)間只會(huì)導(dǎo)致能量再諧振幾個(gè)周期,這可以從初級電流波形中看出(圖8和圖9)。

3. 緩沖開關(guān)選擇

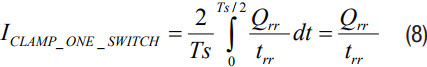

(1)的簡化版本是從MOSFET的數(shù)據(jù)手冊中獲取最壞情況限值。以下公式提供了對電容器中電流的更多了解:

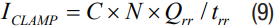

之所以使用因數(shù) 2,是因?yàn)橹豢紤]了半個(gè)開關(guān)周期,對于全橋或半橋拓?fù)洌诉^程會(huì)發(fā)生兩次。同樣在圖1中,由于兩個(gè)開關(guān)關(guān)斷,反向恢復(fù)電荷加倍。因此,總電流由下式給出:

其中 C 為 2 表示全橋配置;C 為 1 表示中心抽頭變壓器;N 是并聯(lián)的 MOSFET 數(shù)量。這是通過有源緩沖開關(guān)的平均電流。

數(shù)字化實(shí)施

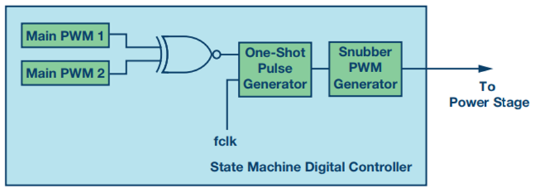

有源鉗位緩沖器的數(shù)字實(shí)現(xiàn)有兩個(gè)控件:控制1是緩沖器延遲(即緩沖器PWM邊沿與觸發(fā)邊沿的可調(diào)延遲)。控制 2 是緩沖 PWM 導(dǎo)通時(shí)間。觸發(fā)點(diǎn)是H橋相對支路(例如OUTC和OUTD)的主PWM上升沿的邏輯OR。緩沖 PWM 不需要像主 PWM 分辨率那樣高的分辨率(例如 125 ps)。因此,觸發(fā)所需的時(shí)鐘速度相對較慢(5 ns分辨率),這也節(jié)省了功耗(40×因子)。該概念還可以應(yīng)用于次級上有一個(gè)中心抽頭的電源轉(zhuǎn)換拓?fù)洹4送猓摳拍钸€可以進(jìn)一步應(yīng)用于各個(gè)開關(guān),其中分立式有源箝位開關(guān)緩沖單元放置在每個(gè)功率晶體管上。在這種情況下,有源箝位FET的驅(qū)動(dòng)信號取自同步整流器的下降沿。

圖5.緩沖PWM的數(shù)字實(shí)現(xiàn)。

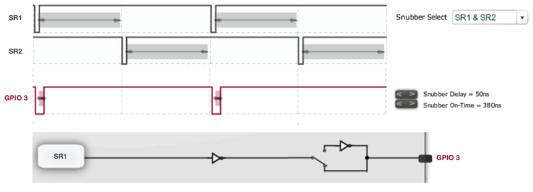

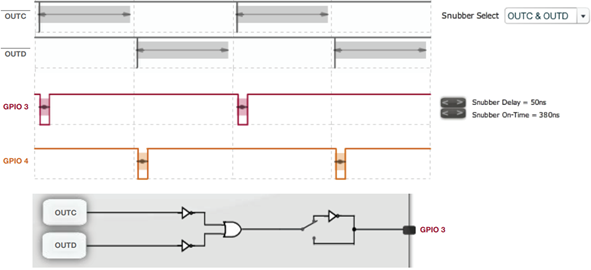

ADP1055數(shù)字控制器提供了一套合適的工具來實(shí)現(xiàn)這一點(diǎn)。通過直觀的GUI,可以在幾分鐘內(nèi)完成主動(dòng)鉗位緩沖器的優(yōu)化。ADP1055提供兩種選擇,用于使用SR1和SR2或OUTC和OUTD信號的邏輯組合來設(shè)置緩沖器PWM。在這兩種情況下,緩沖器PWM都可以配置兩個(gè)選項(xiàng),如圖6和圖7所示。在上述所有場景中,可以使用緩沖器延遲(設(shè)置死區(qū)時(shí)間)和緩沖器開啟時(shí)間特征對優(yōu)化參數(shù)進(jìn)行微調(diào)。兩個(gè)信號的邏輯組合與極性選擇為用戶提供了選擇正確緩沖器的完全自由。

圖6.使用選項(xiàng) 1 — SR1 和 SR2 的緩沖時(shí)序。

圖7.使用選項(xiàng) 2 - OUTC 和 OUTD 緩沖時(shí)序。

全橋拓?fù)鋵?shí)驗(yàn)結(jié)果

為了進(jìn)行實(shí)驗(yàn)驗(yàn)證,選擇了一個(gè)隔離式DC-DC轉(zhuǎn)換器,標(biāo)稱輸入為48 V,額定輸出為12 V、20 A,開關(guān)頻率為125 kHz。拓?fù)涫侨珮蚴降模瑤в懈边叄鐖D1所示。

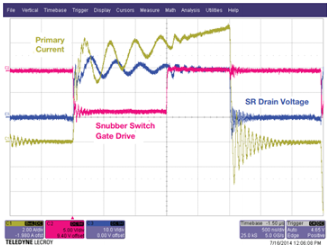

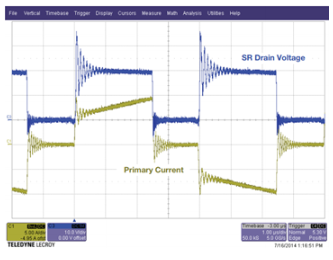

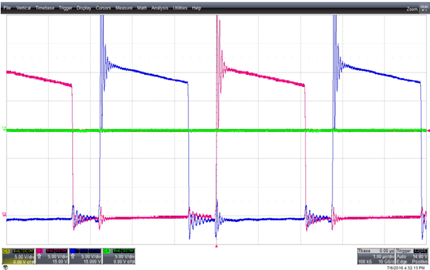

圖8顯示了不正確的導(dǎo)通時(shí)間緩沖器如何產(chǎn)生過多的振鈴和同步MOSFET的振蕩漏極電壓,這也反映在初級電流中。前沿尖峰也很嚴(yán)重,會(huì)導(dǎo)致不必要的EMI。

圖8.緩沖器的時(shí)間過長。

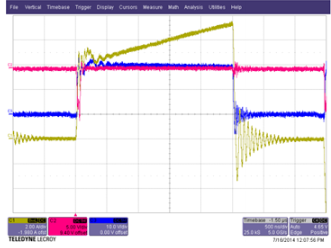

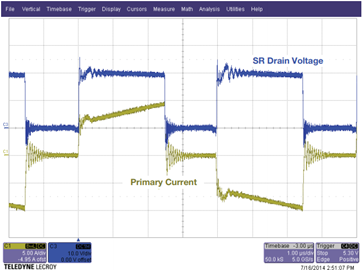

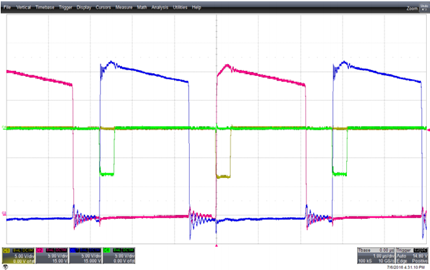

圖9顯示了一個(gè)優(yōu)化的導(dǎo)通緩沖器,其中同步MOSFET的漏極電壓沒有振鈴。此外,前沿尖峰也幾乎被消除。

圖9.優(yōu)化緩沖器的時(shí)序。

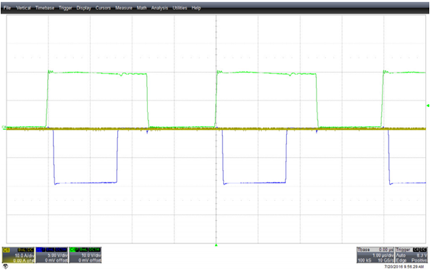

圖10顯示了沒有有源箝位緩沖器的同步MOSFET的漏極電壓。電壓偏移可能高達(dá)穩(wěn)態(tài)電壓的 1.5 倍,MOSFET 有可能進(jìn)入雪崩狀態(tài)。

圖 10.無主動(dòng)鉗式緩沖器。

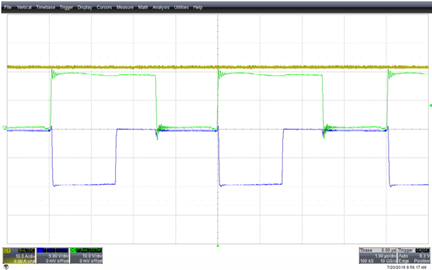

圖11顯示了有源鉗位緩沖器的有效性。前沿尖峰被完全消除,MOSFET的漏極上沒有振鈴效應(yīng)。

圖 11.帶主動(dòng)夾緊緩沖器。

圖 12.0 A 負(fù)載時(shí)的緩沖效果。

綠色跡線:SR 漏極,10 V/格

藍(lán)色跡線:鉗位 FET 柵源電壓,5 V/格 黃色跡線:負(fù)載電流,10 A/格

圖 13.20 A 負(fù)載時(shí)的緩沖效果。

綠色跡線:SR 漏極,10 V/格

藍(lán)色跡線:鉗位 FET 柵源電壓,5 V/格 黃色跡線:負(fù)載電流,10 A/格

半橋拓?fù)鋵?shí)驗(yàn)結(jié)果

在標(biāo)稱輸入為48 V、額定輸出為9 V、200 W、開關(guān)頻率為180 kHz的半橋拓?fù)渖线M(jìn)行了額外的實(shí)驗(yàn)驗(yàn)證。

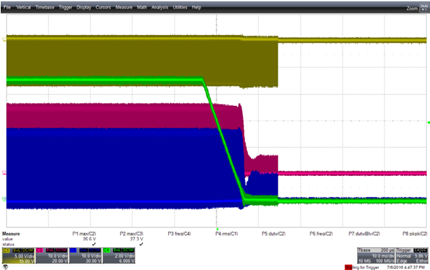

圖 14.主動(dòng)鉗位緩沖器禁用。

紅色跡線:SR1 漏極,5 V/div

藍(lán)色跡線:SR2 漏極;5 V/div

綠色跡線:緩沖器 PWM,5 V/div

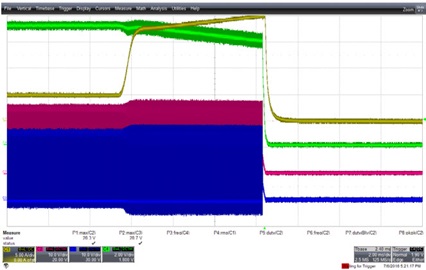

圖 15.主動(dòng)鉗位緩沖器已啟用。

紅色跡線:SR1 漏極,5 V/格

藍(lán)色跡線:SR2 漏極,5 V/格

綠色跡線:緩沖器 PWM,5 V/格

圖 16.軟啟動(dòng)期間的SR漏極波形,帶有源箝位緩沖器。

黃色跡線:緩沖器 FET 柵源電壓,5 V/格

紅色跡線:SR1 漏極,10 V/格

藍(lán)色跡線:SR2 漏極,10 V/格

綠色跡線:輸出電壓,2 V/格

圖 17.軟啟動(dòng)期間的SR漏極波形,帶有源箝位緩沖器。

黃色跡線:緩沖器 FET 柵源電壓,5 V/格

紅色跡線:SR1 漏極,10 V/格

藍(lán)色跡線:SR2 漏極,10 V/格

綠色跡線:輸出電壓,2 V/格

圖 18.短路測試期間的 SR 漏極電壓。

黃色跡線:負(fù)載電流,5 A/格

紅色跡線:SR1 漏極,10 V/格

藍(lán)色跡線:SR2 漏極,10 V/格

綠色跡線:輸出電壓,2 V/格

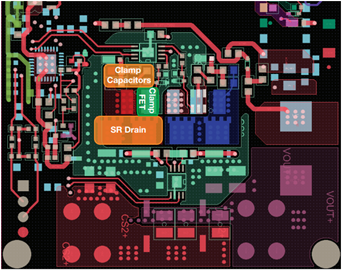

布局注意事項(xiàng)

圖8顯示了上述半橋拓?fù)涞牟季帧jP(guān)鍵要點(diǎn)是通過將環(huán)路縮短或收緊到狹窄區(qū)域來降低箝位環(huán)路的寄生電感。否則會(huì)降低夾具的有效性,導(dǎo)致鉗夾期間的高頻沖洗。

圖 19.主動(dòng)夾緊緩沖器的布局。

結(jié)論

本文展示了有源鉗位緩沖電路的數(shù)字實(shí)現(xiàn),用于隔離式DC-DC轉(zhuǎn)換器中的高輸出電流應(yīng)用。所提出的有源箝位方案具有多種優(yōu)點(diǎn),例如較低的箝位電壓導(dǎo)致較低的MOSFET擊穿電壓額定值,從而提高效率。它還消除了振鈴,從而降低了電磁干擾 (EMI)。它是一種低成本和簡單的電路,具有簡單的驅(qū)動(dòng)方案。與其他涉及額外電感器的有源緩沖器相比,它還節(jié)省了 PCB 板的成本.總體而言,電源的可靠性大大提高。此外,消除了前沿尖峰,從而減少了主開關(guān)上的應(yīng)力。此外,更高的效率意味著更低的熱量產(chǎn)生,這對于難以散熱的受限區(qū)域中的模塊非常有用。

ADP1055數(shù)字控制器提供一套合適的工具,無需使用復(fù)雜的編程或編碼即可完成上述任務(wù)。ADP1055還支持許多其他功能,如黑匣子、軟停止、命令屏蔽和非線性增益。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8741瀏覽量

147708 -

MOSFET

+關(guān)注

關(guān)注

147文章

7221瀏覽量

213922 -

DC-DC

+關(guān)注

關(guān)注

30文章

1957瀏覽量

81892

發(fā)布評論請先 登錄

相關(guān)推薦

高可靠性與超寬環(huán)境溫度的混合集成DC-DC變換器的設(shè)計(jì)

dc模塊電源的控制方法

可實(shí)現(xiàn)高可靠性電源的半導(dǎo)體解決方案

如何實(shí)現(xiàn)高可靠性電源的半導(dǎo)體解決方案

智能電源:模擬和數(shù)字控制回路實(shí)現(xiàn)對比

如何選擇用于電壓轉(zhuǎn)換的DC-DC模塊電源?

GAIA電源DC-DC轉(zhuǎn)換器模塊的正常工作溫度及工業(yè)應(yīng)用

數(shù)字控制可實(shí)現(xiàn)具有有源緩沖功能的高可靠性DC-DC電源轉(zhuǎn)換

茂睿芯高壓DCDC:高效率、高可靠性的DC-DC轉(zhuǎn)換器

為什么需要DC-DC模塊電源?如何選擇高可靠性的DC-DC模塊電源?

如何提升基于DC-DC模塊的電源系統(tǒng)的可靠性?

數(shù)字控制實(shí)現(xiàn)帶有源緩沖高可靠性DC-DC功率轉(zhuǎn)換

開關(guān)電源DC-DC電源應(yīng)用設(shè)計(jì)原理

設(shè)計(jì)基于TMS320F280x的數(shù)字控制DC-DC開關(guān)電源

DC-DC電源管理芯片效率測試,確保高效能與可靠性的關(guān)鍵步驟

數(shù)字控制可實(shí)現(xiàn)具有有源緩沖功能的高可靠性DC-DC電源轉(zhuǎn)換

數(shù)字控制可實(shí)現(xiàn)具有有源緩沖功能的高可靠性DC-DC電源轉(zhuǎn)換

評論