在這篇文章中,我們討論了verilog中最常用的兩個結(jié)構(gòu)-if語句和case語句。

我們在上一篇文章中已經(jīng)看到了如何使用程序塊(例如 always 塊來編寫按順序執(zhí)行的 verilog 代碼。 我們還可以在程序塊中使用許多語句來控制在我們的verilog設計中信號賦值的方式。

這些語句統(tǒng)稱為順序語句。case 語句和 if 語句都是 verilog 中順序語句的示例。在這篇文章的其余部分,我們將討論如何在verilog中使用這兩個語句。

然后,我們考慮這兩個結(jié)構(gòu)的簡短示例,以說明我們?nèi)绾卧趯嵺`中使用它們。

Verilog If 語句

if 語句是一個條件語句,它使用布爾條件來確定要執(zhí)行哪些verilog代碼塊。只要條件的計算結(jié)果為 true,就會執(zhí)行與該條件關聯(lián)的代碼分支。此語句類似于其他編程語言(如 C)中使用的 if 語句。

下面的 verilog 代碼片段顯示了 if 語句的基本語法。

如果我們不需要 else 和 else 分支,我們可以從語句中刪除它們。事實上,我們已經(jīng)在關于always塊的帖子中看到了這一點,我們在其中使用 posedge 宏來檢測時鐘信號的上升沿。如果需要,我們可以包含盡可能多的其他分支,以正確建模底層電路。

if 語句使用布爾條件來確定要執(zhí)行的代碼行。

在上面的代碼段中,這些表達式由 和 給出。這些表達式按順序計算,如果表達式的計算結(jié)果為 true,則執(zhí)行與表達式關聯(lián)的代碼。 if 語句只有一個分支將執(zhí)行。這通常是計算結(jié)果為 true 的第一個表達式。唯一的例外情況是,當所有表達式都不為 true 時。在這種情況下,將執(zhí)行 else 分支中的代碼。當我們在 if 語句代碼中省略 else 分支時,在這種情況下不會執(zhí)行任何分支。

與每個分支關聯(lián)的代碼可以包含任何有效的 verilog 代碼,包括進一步的 if 語句。此方法稱為嵌套 if 語句。 在 verilog 中使用這種類型的代碼時,我們應該注意限制嵌套語句的數(shù)量,因為它可能會導致滿足時間的困難。

If 語句示例

我們已經(jīng)看到了 if 語句的實際示例,當在 verilog always塊的帖子中對觸發(fā)器進行建模時。為了更徹底地演示此結(jié)構(gòu),讓我們考慮一個時鐘多路復用器的示例。

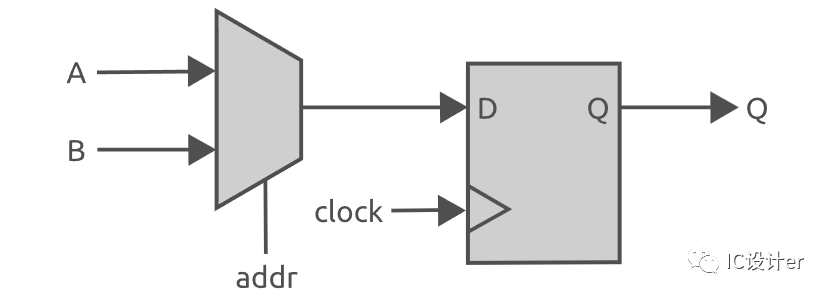

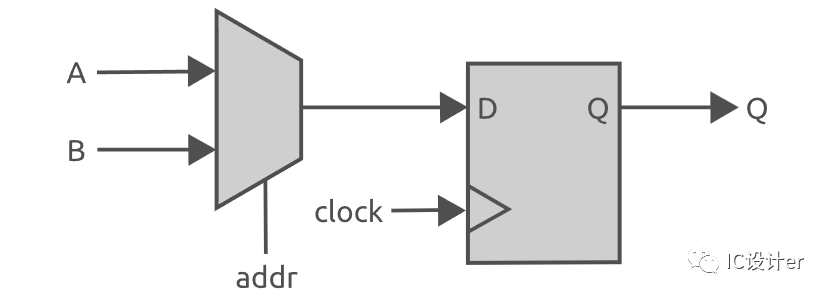

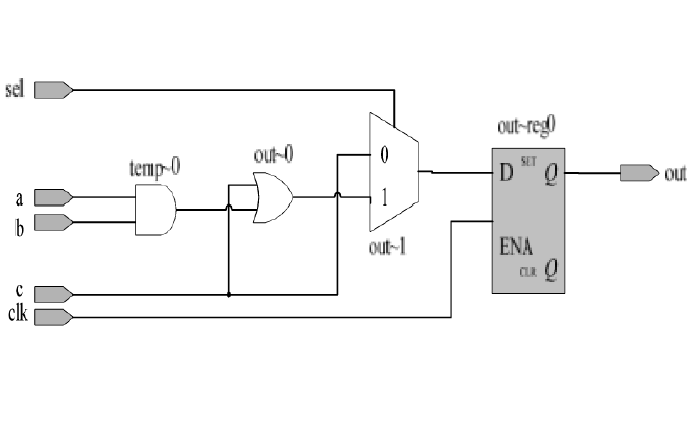

在本例中,我們將使用異步復位的 D 類型觸發(fā)器來保存多路復用器的輸出。下面的電路圖顯示了我們將在本例中使用的電路。

下面的代碼片段顯示了我們?nèi)绾问褂脝蝹€ always 塊和 if 語句來實現(xiàn)這一點。

|

1 |

always@(posedgeclock,posedgereset)begin |

在此示例中,我們使用第一個if語句在復位時觸發(fā),輸出0。當復位無效時,always塊已由時鐘的上升沿觸發(fā)。我們使用第一個 if 語句的 else 分支來被觸發(fā),我們使用第二個if語句來模擬多路復用電路的行為。這是 verilog 中嵌套 if 語句的示例。

當 addr 信號為 0b時,我們使用嵌套 if 語句的第一個分支被觸發(fā),將輸入a賦值給輸出。然后,我們使用嵌套 if 語句的 else 分支來捕獲 addr信號為1b 時的情況。 我們也可以在這里使用 else-if 類型語句,但 else 語句更簡潔。這兩種情況下的行為是相同的,因為信號在實際電路中只能是0b或1b。

Verilog case語句

我們使用 verilog case 語句根據(jù)設計中給定信號的值選擇要執(zhí)行的代碼塊。當我們在verilog中編寫語句時,我們指定了一個要監(jiān)視和評估的輸入信號。然后將該信號的值與case語句的每個分支中指定的值進行比較。找到輸入信號值的匹配項后,將執(zhí)行與該值關聯(lián)的分支。 verilog case語句執(zhí)行的功能 C語言中的switch語句相同。下面的代碼片段顯示了 verilog 中case語句的一般語法。

|

3 |

// This branch executes when = |

|

6 |

// This branch executes when = |

|

9 |

// This branch executes in all other cases |

可以刪除語句的默認分支,盡管這是不可取的。如果刪除默認分支,則<變量>的所有有效值都必須具有自己的分支。與 if 語句一樣,與每個分支關聯(lián)的代碼可以包含任何有效的 verilog 代碼。這包括進一步嵌套順序語句,例如if或case語句。同樣,我們應該嘗試限制嵌套語句的數(shù)量,因為它可以更輕松地滿足我們的計時要求。

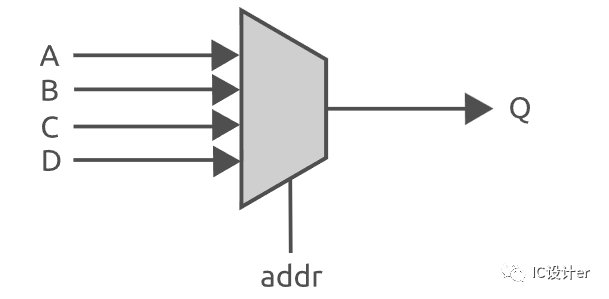

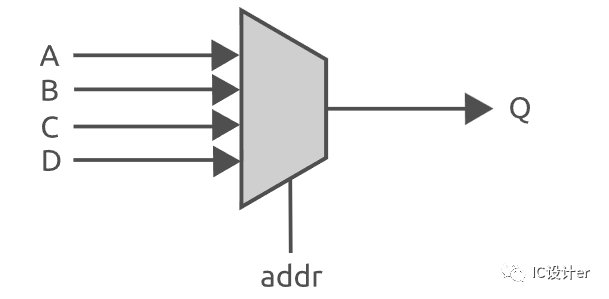

case語句示例 為了更好地演示erilog中使用case語句的使用方式,讓我們考慮一個基本示例。在本例中,我們將介紹一個簡單的四比一多路復用電路。 我們經(jīng)常使用 case 語句在 verilog 中對大型多路復用器進行建模,因為它生成的代碼比基于連續(xù)賦值的實現(xiàn)更具可讀性。下面的電路圖顯示了我們將在本例中使用的電路。

下面的代碼片段顯示了我們將如何使用 case 語句實現(xiàn)此電路。

此示例顯示了使用 verilog中的case語句對多路復用器進行建模是多么簡單。事實上,case語句提供了在 verilog 中對多路復用器進行建模的最直觀方法。 雖然這個例子很簡單,但有幾個要點我們應該更詳細地考慮。在這個例子中首先要注意的是,我們使用阻塞賦值。這樣做的原因是我們正在對組合邏輯進行建模,而非阻塞分配通常會導致在我們的設計中放置觸發(fā)器。

這里要注意的另一件事是,我們可以從此示例中刪除默認關鍵字。然后,我們將顯式列出輸出d 值所需的 addr 值。但是,我們在此示例中包含了默認關鍵字,以演示應如何使用它。

審核編輯:劉清

如何在verilog中使用If語句和case語句?

如何在verilog中使用If語句和case語句?

評論