編 者 按

避不開的場景 如果熟悉SpinalHDL設計,那么都應該清楚在SpinalHDL設計里,如果輸出端口沒有給明確賦值的話,那么在生成RTL代碼時會報錯提示我們沒有為端口賦值。想想如果你在設計一個AXI4的測試邏輯,但你并不需要使用里面的全部信號(要知道AXI4總線配置里面的哪個信號使用哪個不使用可使一大堆參數),如果想要做的模塊在任何場景下都能直接連接使用的話,最早對于我沒有使用的信號我是這么來處理的:

if(axi4Port.useRegion)axi4Port.clearAll() if(axi4Port.useLock) axi4Port.lock.clear() ……是不是寫起來很啰嗦?~ 還有一個場景就是在FPGA里面在制作PR版本時對于動態區和靜態區之間的接口信號為了方便后續Impl版本的時序收斂,對于沒有使用到的信號以及賦常值的信號都建議添加約束:

對于輸入沒有使用到的信號,內部定義一個寄存器來鎖存信號,并把這個寄存器的屬性設置為nopurne

對于暑促好信號,則建議將輸出信號必須為reg類型,并將該輸出信號配置為preserve屬性。

對于這種使用不到的信號,一個個的follow這些原則不免有點兒太過于“體力活”~ 而在SpinalHDL里,我們可以通過DataAnalyzer來快速地實現這些沒有使用到的端口信號。 》DataAnalyzer

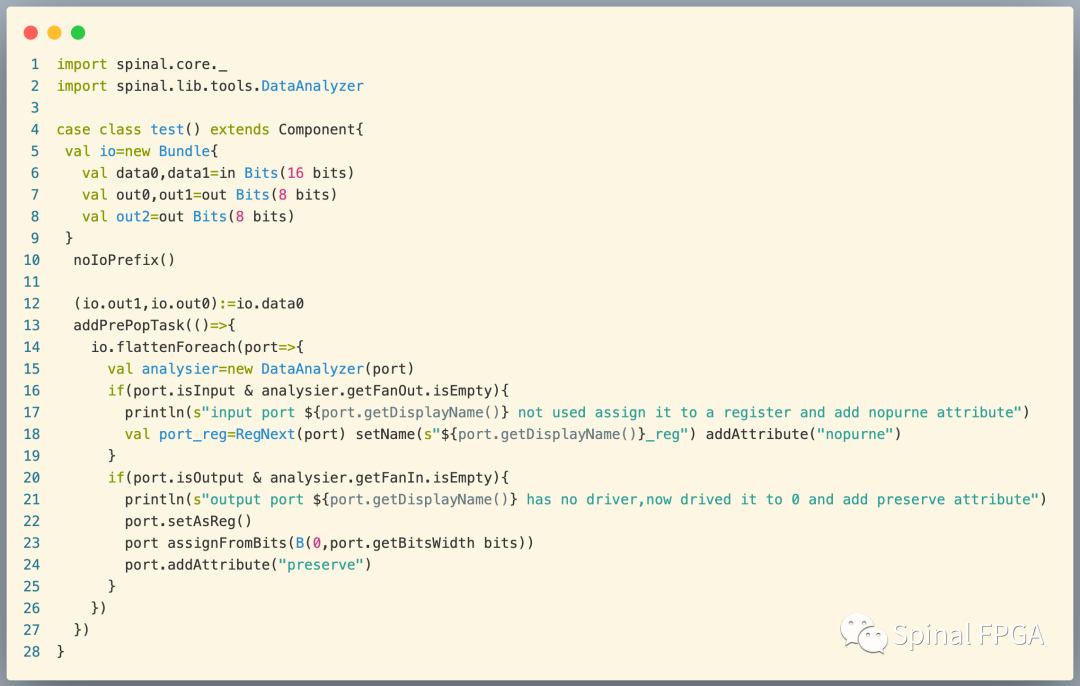

考慮下面這個簡單的模塊:

在這個模塊里,對于輸入的data1接口我們并沒有用,而對于輸出out2端口,我們也并沒有輸出賦值。

現在,如果我們想要實現針對PR那種場景的需求,我們可以通過DataAnalyzer來寫一個通用的處理代碼:

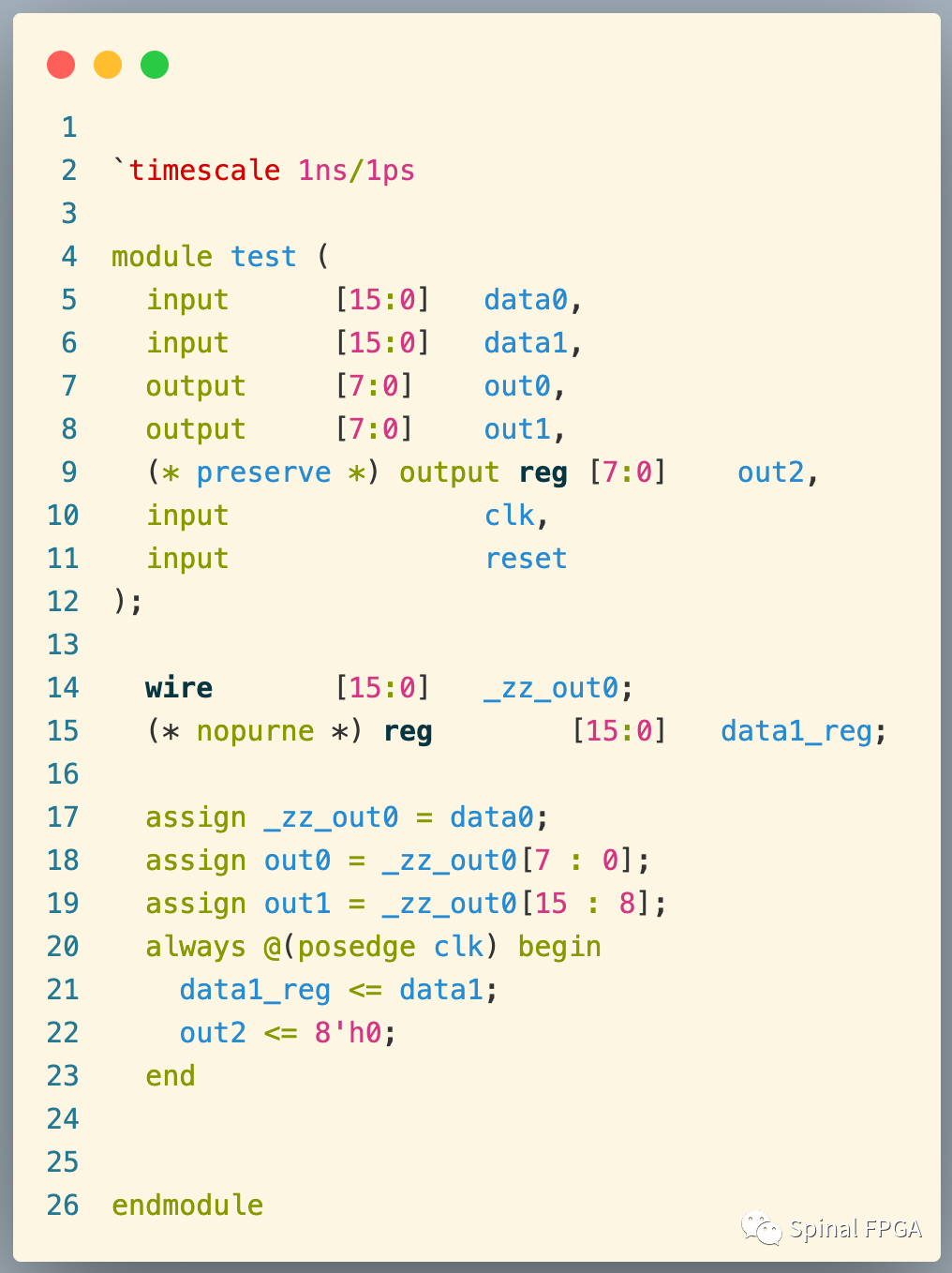

這里我們為模塊添加一個PrePopTask。對于io里面的每個信號,都例化一個DataAnalyzer,對于接口為輸入信號(port.isInput),并且其沒有任何扇出信號(analysier.getFanOut.isEmpty),則將其賦值給一個寄存器,并對該寄存器添加“nopurne”屬性。而如果接口信號為輸出信號(port.isOutput),并且沒有任何的信號給他賦值(analysier.getFanIn.isEmpty),則將其設置為寄存器,賦值為0并添加“preserve”屬性。最終生成的代碼:

完全符合我們的需求~

結語

能省功夫就省功夫,在Boss的許可下,選擇盡可能高效的工具,這周工作里修改一個Verilog代碼,在SpinalHDL里面五分鐘能實現的需求Verilog里改了小半天,極大打擊工作熱情~

-

FPGA

+關注

關注

1630文章

21786瀏覽量

605060 -

寄存器

+關注

關注

31文章

5363瀏覽量

120913 -

信號

+關注

關注

11文章

2804瀏覽量

76992 -

總線

+關注

關注

10文章

2899瀏覽量

88273 -

端口

+關注

關注

4文章

988瀏覽量

32141

原文標題:三分鐘教你快速處理沒有使用的端口信號

文章出處:【微信號:Spinal FPGA,微信公眾號:Spinal FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

免費三分鐘

職場啟示: 三分鐘碎片化

讓程序運行三分鐘,停一分鐘,循環下去,直到設置停止循環的位置

Inout雙向端口信號處理方法

三分鐘能做什么?三分鐘能讓我的iPhone6s重啟N次!

小米掃地機器人臺灣開售 三分鐘售罄

三分鐘來快速回顧!11月無人機大事件

三分鐘概述8類常用元器件資料下載

Node-RED初學者教程-三分鐘學習

三分鐘教你快速處理沒有使用的端口信號

三分鐘教你快速處理沒有使用的端口信號

評論