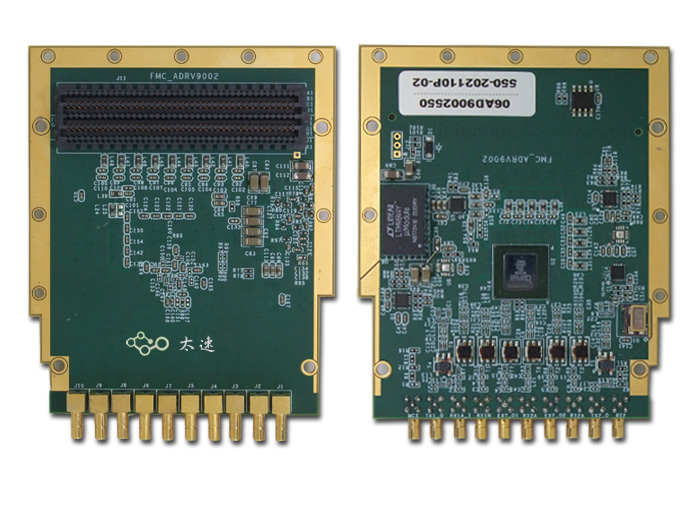

FMC550-基于ADRV9002雙窄帶寬帶射頻收發器FMC子卡

一、產品概述

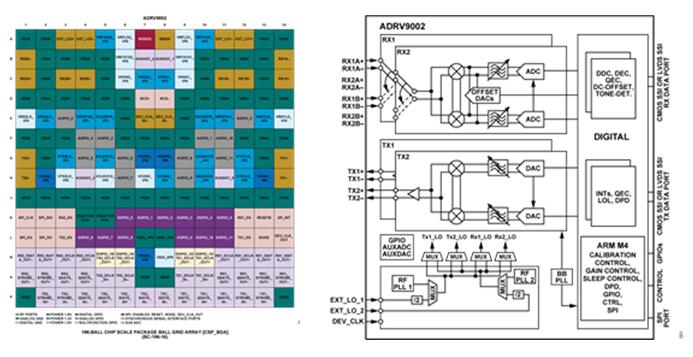

ADRV9002是一款高性能、高線性度、高動態范圍收發器,旨在針對性能與功耗系統進行優化。該設備是可配置的,非常適合要求苛刻、低功耗、便攜式和電池供電的設備。ADRV9002的工作頻率為30MHz至6000MHz,涵蓋UHF、VHF、工業、科學和醫療(ISM)頻段、窄帶(kHz)的蜂窩頻段以及高達40MHz的寬帶操作。ADRV9002能夠同時進行TDD和FDD操作。

收發器包括直接轉換信號路徑,具有先進的噪聲指數和線性度。每個完整的接收器和變送器子系統都包括直流失調矯正、正交誤差校正(QEC)以及可編程數字濾波器,因此數字基帶中不再需要這些功能。另外,它集成了輔助模數轉換器(ADC)、輔助數模轉換器(DAC)以及通用輸入/輸出(GPIO)等若干輔助功能,因而可提供額外的監測和控制能力。

完全集成的鎖相環(PLL)為變送器、接收器和時鐘部分提供高性能、低功耗小數N頻率合成。精心選用的設計和布局技術提供了高性能個人射頻應用所需要的隔離。

其中集成了全部壓控振蕩器(VCO)和環路濾波器元件,從而盡可能減少外部元件數量。本地振蕩器(LO)具有靈活的配置選項,并包括快速鎖定模式。

該收發器具有低功耗睡眠和監控模式,可在監控通信的同時,節省功耗并延長便攜式設備的電池壽命。

完全集成的低功耗數字預失真(DPD)針對窄帶和寬帶信號進行了優化,并實現了高效功率放大器的線性化。

ADRV9002的內核可以直接由1.0V、1.3V和1.8V穩壓器供電,并通過標準4線串行端口進行控制。其他電源用來提供正確的數字接口電平,并優化接收器、變送器和輔助轉換器性能。

使用可配置的CMOS或低電壓差分信號(LVDS)串行同步接口(SSI)選項,可支持高數據速率和低數據速率接口。

二、優勢和特點

?2×2高度集成的收發器

?頻率范圍為30MHz至6000MHz

?變送器和接收器帶寬為12kHz至40MHz

?兩個完全集成的小數N射頻頻率合成器

?LVDS和CMOS同步串行數據接口選項

?低功耗監控器和休眠模式

?多芯片同步功能

?快速跳頻

?動態配置文件切換,可實現動態數據速率和采樣率

?完全集成的DPD,適用于窄帶和寬帶波形

?可通過4線SPI完全編程

?12mm×12mm、196球CSP_BGA

?通過FMC連接器連接FPGA母板(ZC706和ZCU102)

?采用單個FMC連接器供電

?包括原理圖、布局、BOM、HDL、驅動程序和應用軟件

三、產品應用

?關鍵任務通信

?甚高頻(VHF)、超高頻(UHF),以及蜂窩到6GHz

?時分雙工(TDD)和頻分雙工(FDD)應用

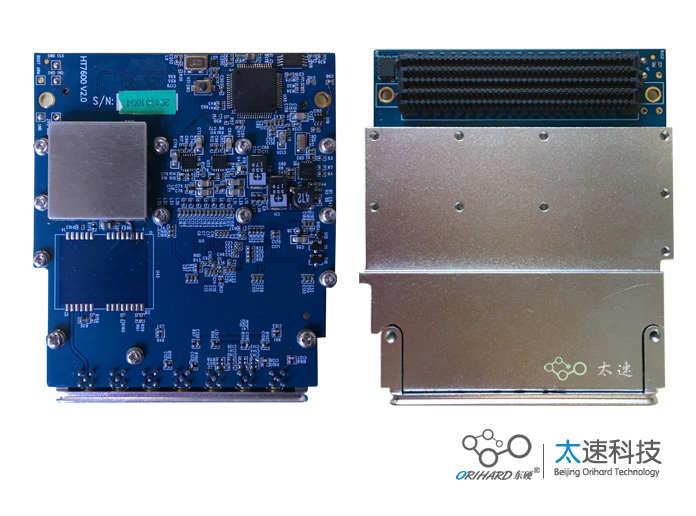

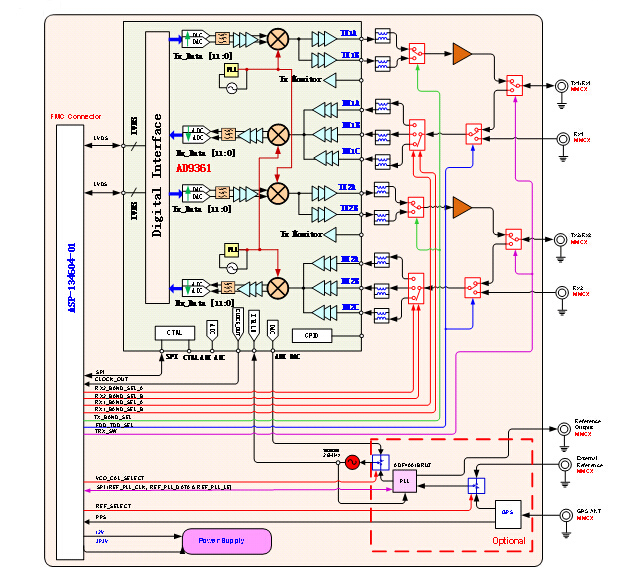

FMC177-基于AD9361的雙收雙發射頻FMC子卡

一、板卡介紹

FMC177射頻模塊分別包含兩個接收通道與發射通道,其頻率可覆蓋達到70MHz~6GHz,AD9361芯片提供具有成本效益的實驗平臺,具有達到56MHz的瞬時帶寬,更高的靈敏度,靈活的動態范圍,廣泛適合于SDR(無線電軟件),移動基站,WiFi,無線局域網,專用或通用無線電設備等應用。設計者通過使用FMC177,可以有效簡單的使用AD9361芯片。

二、主要指標

1.射頻頻率:70MHz~6GHz;

2.ADC/DAC采集:12位;

3.兩路TX,兩路RX,工作實現方式雙工與半雙工;

5.瞬時帶寬:56MHz;

6.支持直流供電+12V;

7.支持GPS;

8.規格:標準FMC子卡。

三、板子接口特性

| No. | Items | Specifications | Remark | |

| Tx | 1 | Frequency | 70~6000MHz | |

| 2 | Bandwidth | Upto56MHz | real-timebandwidth,tunable | |

| 3 | Transmission | >5dBm | CW | |

| 4 | EVM | <1.5% | Typical:5dBm@20MHzbandwidth | |

| 5 | GainControlRange | >80dB | ||

| 6 | GainStep | 0.25dB | ||

| 7 | ACLR | @0dBmLTEoutput | ||

| 8 | Spurious | TBD | ||

| 9 | SSBSuppression | 35dBc | ||

| 10 | LOSuppression | 50dBc | ||

| 11 | DACSampleRate(max) | 61.44MS/s | ||

| 12 | DACResolution | 12bits | ||

| Rx | 1 | Frequency | 70~6000MHz | |

| 2 | Bandwidth | Upto56MHz | real-timebandwidth,tunable | |

| 3 | Sensitivity: | -90dBm@20MHz | NoiseFigure | |

| 4 | EVM | <1.5% | @-30dBminput | |

| 5 | GainControlRange | >60dB | ||

| 6 | GainStep | 1dB | ||

| 7 | Blocking | TBD | ||

| 8 | NoiseFigure | <8db | MaximumRXgain | |

| 9 | IIP3(@typNF) | -25dBm | ||

| 10 | ADCSampleRate(max) | 61.44MS/s | ||

| 11 | ADCResolution | 12bits | ||

| 12 | ADCWidebandSFDR | 78dBc | ||

| 1 | Voltage | 3.3V | ||

| 2 | ON/OFFTIME | <6us | ForTDDmodel | |

| 3 | DuplexingModel | TDDorFDD | ||

| 4 | W/GPSDOReference | 0.01ppb |

四、應用范圍:

SDR(無線電軟件);移動基站,例如Femto‐cells,Pico‐cells,Small‐cells,Micro‐cell等等;WiFi;無線局域網;專用或通用無線電設備。

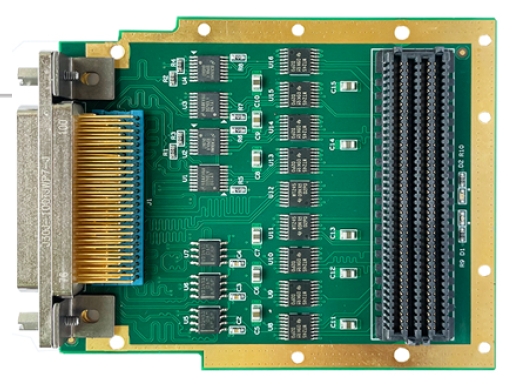

五、與FPGA處理卡搭建系統

本板卡是將FMC177_AD9361射頻收發模塊與本公司基于FMC接口K7板卡通過標準的FMC接口相連接。

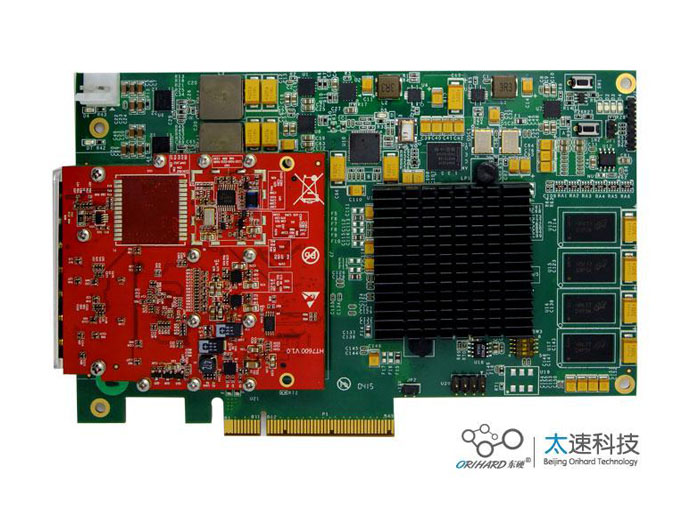

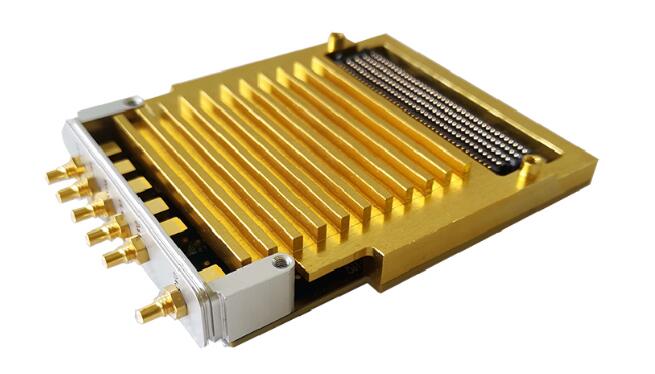

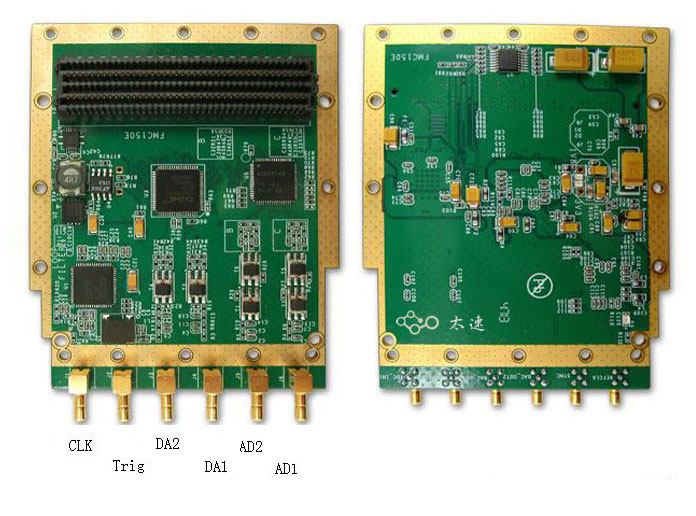

FMCJ465-2路 16bit 12.6GSPS FMC DA子卡

一、板卡概述:

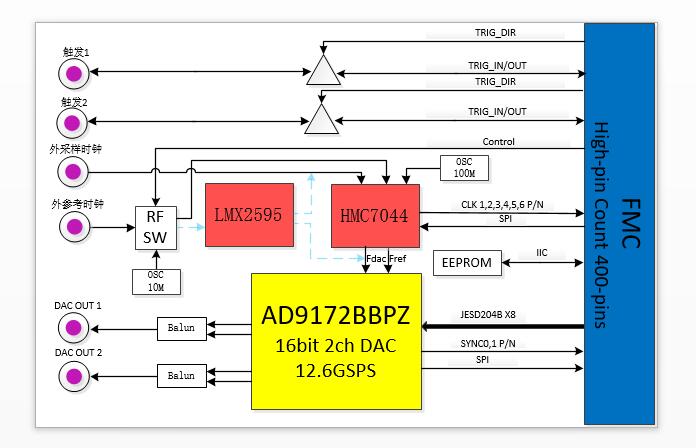

FMCJ465是一款轉換速率最高為12.6GSPS 的DAC 回放板,DAC位數16bit;板卡基于ADI的AD9172系列DAC設計;板卡支持2路可配置的觸發輸出/觸發輸入;DAC的時鐘支持內部參考時鐘、外部參考時鐘、外部采樣時鐘三種方式;并可提供一個接口同時支持外部采樣和外部參考時鐘的版本。

原理框圖

二、主要規格:

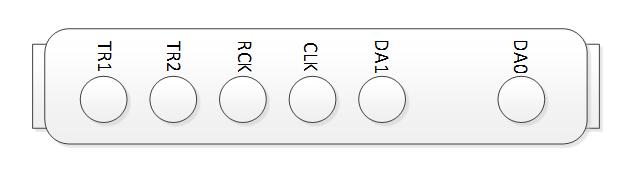

●6個SSMC的連接器,其中2個為模擬信號輸出1(DA 0)和2(DA 1);一個為外部采樣時鐘輸入(CLK);一個為外部參考時鐘輸入(RCK),2個為可由載板配置成輸入或者輸出的同步觸發信號(TR1和TR2)

●外部CLK也可同時兼容外采樣和外參考時鐘(需事先提出需求)

●適應范圍:完全符合Vita57.1規范,包括結構件,子卡尺寸,面板連接器,正反面器件的限高等,大大提供了子卡的通用性和適配性

●多種散熱方式:風冷或導冷

●AC耦合輸入

●內外部時鐘可靈活選擇

●HPC高引腳數連接器

●工作溫度:商業級0℃~+70℃,工業級-40℃~+85℃

三、板卡性能:

模擬輸出

●輸出耦合方式:交流耦合;

●輸出路數:2路;

●輸出頻率:10MHz ~ 6000MHz;

●滿量程輸出電流:16~26mA(RSET=5KΩ),可編程;

●輸出阻抗:50 Ohm;

●連接器:SSMC;

數模轉換器DAC

●單芯片方案;

●分辨率:16bit;

●最大更新率:12.6GS/s

●DAC輸入兼容JESD204B子類1

時鐘

●支持內參考或外部參考:10MHz,功率0~6dBm

●支持外部采樣時鐘最高:12.6GHz; 功率0~6dBm

●輸入阻抗:50 Ohm;

●耦合方式:交流耦合;

觸發

●外部觸發輸入:3.3V LVCMOS或LVTTL;

●觸發輸出:3.3V LVCMOS或LVTTL;

●最大頻率:200MHz;

●連接器:SSMC;

FMC 接口

HPC:ASP-134488-01;

●DP_C2M(0-7),LVDS 1.0V

●LA(00-33),LVDS或者LVCMOS或者LVTTL

●CLK(GBTCLK0,1;CLK0),LVDS 1.8V或2.5V

功耗

●+12V: <0.6?A;

●+3.3V: <0.1A;

●Vadj:<0.2A;

四、其他支持:

●提供Verilog bit文件

●JESD204B Core

五、前面板

|

前面板描述 序 信號 描述 1 DA 0 模擬信號輸出1 2 DA 1 模擬信號輸出 2 3 CLK 外部采樣時鐘(亦可作為外部采樣和參考時鐘,需事先提出需求) 4 RCK 外部參考時鐘 5 TR 1 觸發信號1,可配置成IN或OUT 6 TR 2 觸發信號2,可配置成IN或OUT 六、應用(QT7227): ●軟件無線電 ●寬帶MIMO應用 ●數字波束成形 ●(雷達/聲納)電子戰 ●物理實驗 ●信號智能檢測 ●航空航天和測試儀器 |

| FMCJ450-基于ADRV9009的雙收雙發射頻FMC子卡 |

一、板卡概述

ADRV9009是一款高集成度射頻(RF)、捷變收發器,提供雙通道發射器和接收器、集成式頻率合成器以及數字信號處理功能。這款IC具備多樣化的高性能和低功耗組合,FMC子卡為2路輸入,2路輸出的射頻收發卡,配合FPGA工作滿足3G、4G和5G宏蜂窩時分雙工(TDD)基站應用要求。

二、技術指標

? 雙發射器

? 雙接收器

? 雙輸入共享觀察接收器

? 最大接收器帶寬:200MHz

? 最大可調諧發射器合成帶寬:450MHz

? 最大觀察接收器帶寬:450MHz

? 全集成的小數N射頻合成器

? 全集成的時鐘合成器

? 適用于射頻LO和基帶時鐘的多芯片相位同步

? JESD204B數據路徑接口

? 調諧范圍:75MHz至6000MHz

| No. | Items | Specifications | Remark | |

| Tx | 1 | Frequency | 100~6000MHz | |

| 2 | Bandwidth | Upto450MHz | Txreal-timebandwidth,tunable | |

| 3 | TransmissionPower | 17dBm | 100~6000MHz,CW | |

| 4 | EVM | <0.7%? | ||

| 5 | GainControlRange | 32dB | ||

| 6 | GainStep | 0.05dB | ||

| 7 | ACLR | @0dBmoutput | ||

| 8 | Spurious | 60dBc | ||

| 9 | SSBSuppression | 65dBc | ||

| 10 | LOSuppression | 70dBc | ||

| 11 | DACSampleRate(max) | 122.88MS/s | ||

| 12 | DACResolution | 14bits | ||

| Rx | 1 | Frequency | 100~6000MHz | |

| 2 | Bandwidth | 8to200MHz | real-timebandwidth,tunable | |

| 3 | Sensitivity: | -93dBm@20MHz | NoiseFigure<3db | |

| 4 | EVM | <1.5%? | @-30dBminput | |

| 5 | GainControlRange | |||

| 6 | GainStep | 0.5dB | ||

| 7 | RxAliasBandRejection | 80dB | Duetodigitalfilters | |

| 8 | NoiseFigure | <3db | MaximumRXgain | |

| 9 | IIP3(@typNF) | -25dBm | ||

| 10 | ADCResolution | 16bits | ||

| 11 | ADCWidebandSFDR | 78dBc | ||

| 1 | Voltage | 3.3V&12V | ||

| 2 | ON/OFFTIME | <6us? | TDDmodel | |

| 3 | DuplexingModel | TDD | ||

| 4 | PowerConsumptions | <6w |

三、產品應用

3G/4G/5GTDD宏蜂窩基站;TDD有源天線系統;大規模MIMO;電子戰;便攜測試設備

四、軟件系統

提供支持ZYNQ的FMC接口測試程序源代碼

五、物理特性:

板卡遵循FMC規范,HPC,大小76.5X69mm。

六、供電要求:

FMC接口+12V供電

七、ADRV9009應用軟件

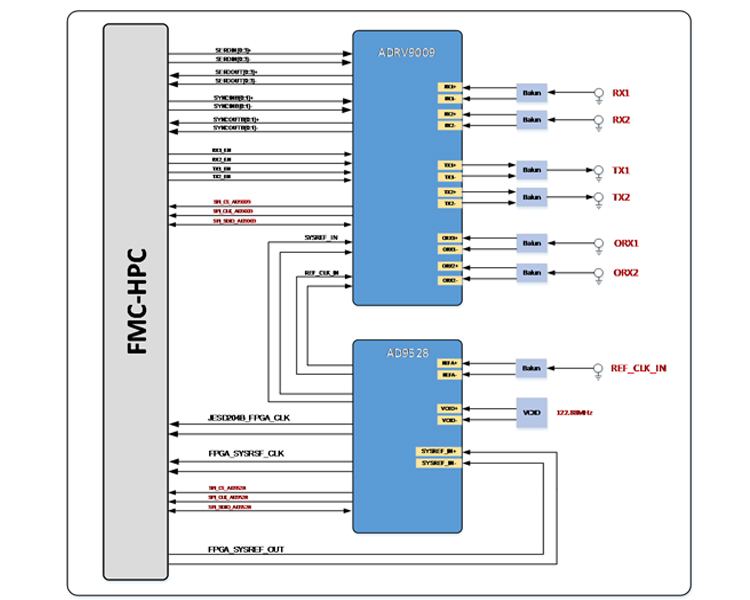

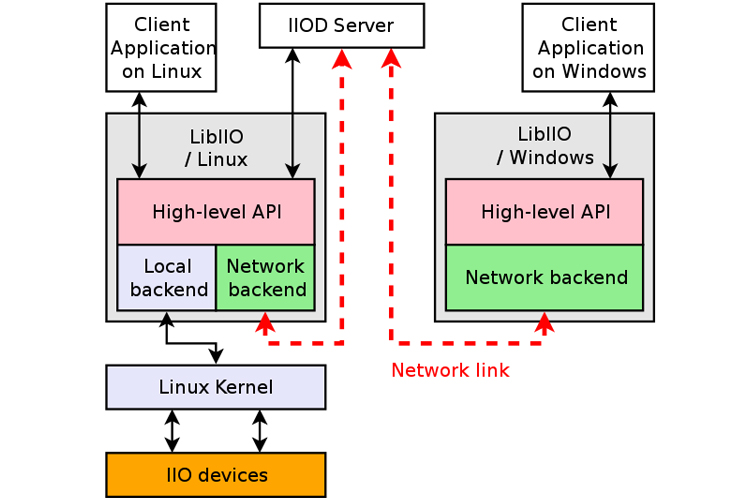

軟件架構:

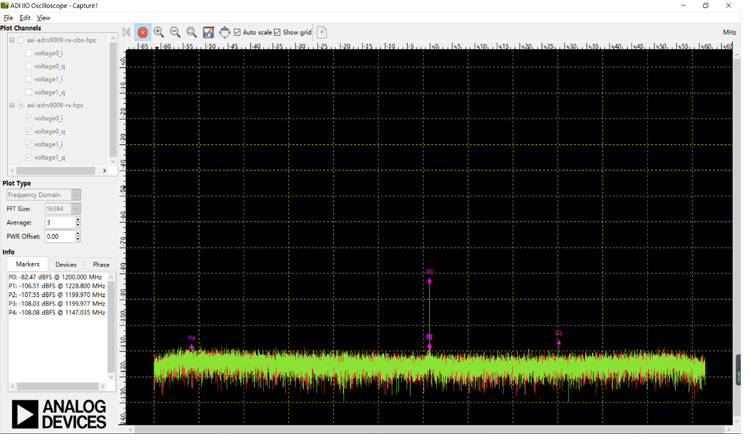

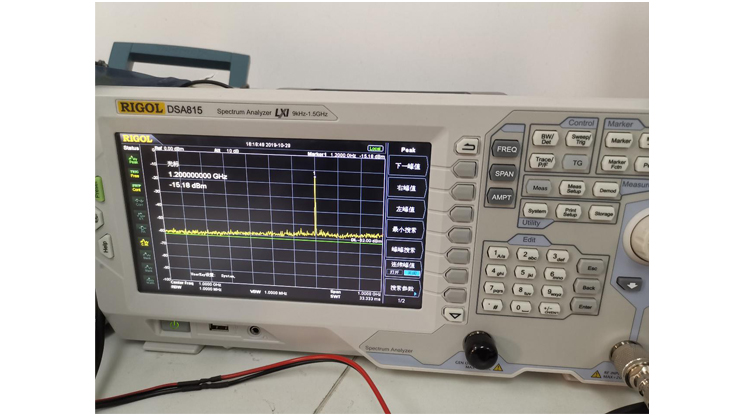

AD采集1.2G波形:

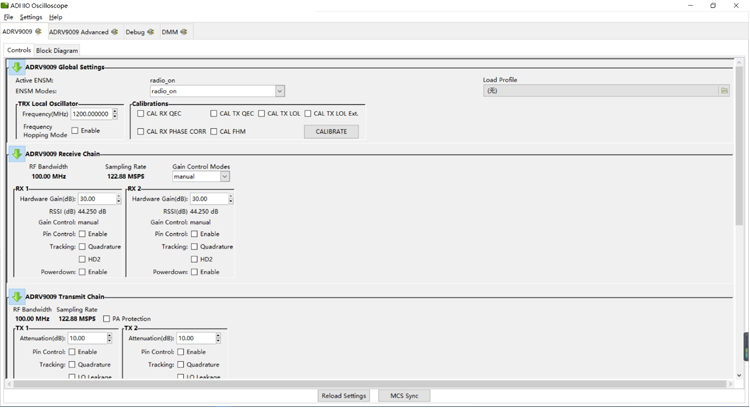

DA輸出設置1.2G及波形:

審核編輯黃宇

-

芯片

+關注

關注

456文章

51117瀏覽量

426005 -

收發器

+關注

關注

10文章

3449瀏覽量

106157 -

射頻

+關注

關注

104文章

5615瀏覽量

168048 -

FMC

+關注

關注

0文章

97瀏覽量

19736

發布評論請先 登錄

相關推薦

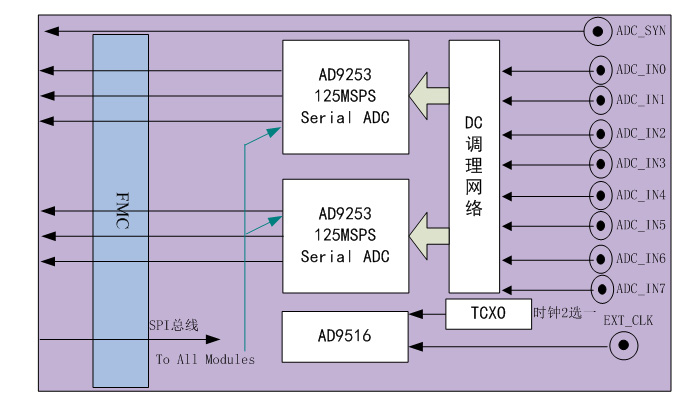

FMC子卡設計原理圖:FMC209-基于FMC的4路125MAD輸入、2路1GDA輸出子卡 中低頻信號采集

FMC子卡原理圖設計:四通道1.25G/14bit數據采集

FMC子卡原理圖設計: 4路 16bit 250M ADC+4路 16bit 2.8G DAC

射頻收發器就是基帶嗎

射頻收發器屬于什么類別

GD32 MCU 入門教程】GD32 MCU 常見外設介紹(12)FMC 模塊介紹

圖形圖像硬件加速器卡設計原理圖:270-VC709E 基于FMC接口的Virtex7 XC7VX690T PCIeX8 接口卡

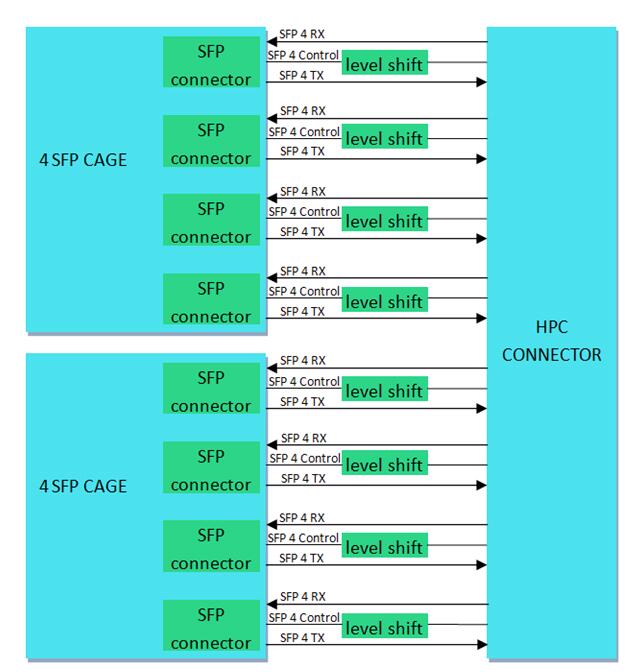

FMC擴展子卡 6 路422,8 組LVDS,8 路GPIO

基于ADRV9002雙窄帶寬帶射頻收發器的FMC子卡FMC550介紹

基于ADRV9002雙窄帶寬帶射頻收發器的FMC子卡FMC550介紹

評論