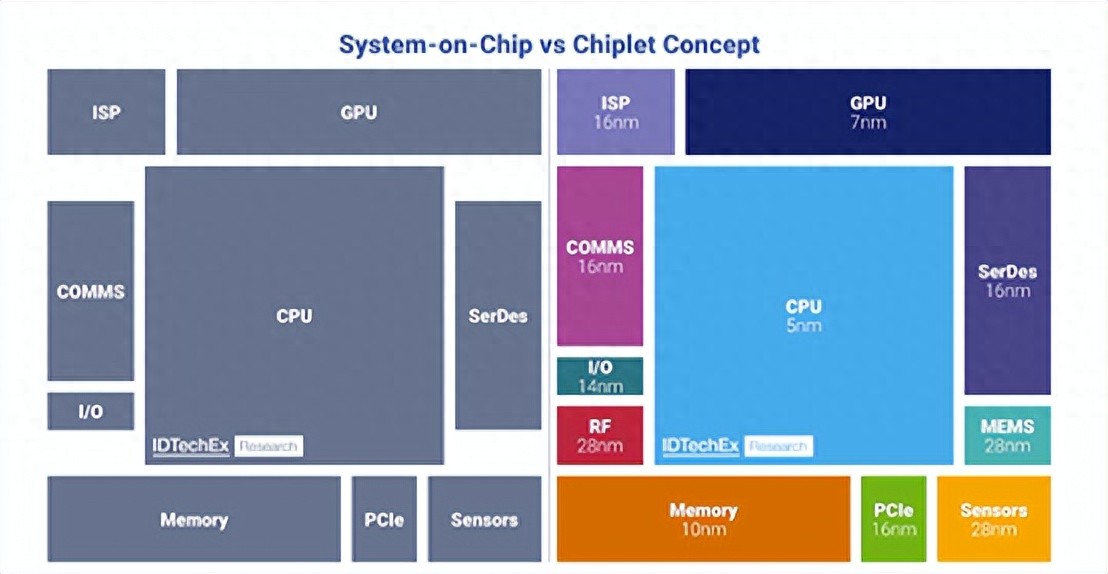

事實證明,將多個 die 或 Chiplet 集成到同一個封裝里跟將它們集成到同一個 die 上有很大不同,在同一個 die上,所有模塊都是在同一個節點上使用相同的工藝開發的。

隨著設計變得更加異構和細分化,Chiplet 需要在系統環境中進行建模、適當的平面規劃、驗證和調試,而非僅作為單獨的組件。這通常始于高層次抽象的系統的完整規范。然后再將規范分成塊并分配給各個設計人員,同時優化他們的設計。最后,將所有子系統作為一個整體重新組合、驗證和測試。

在最簡單的設計中,只有很少的 Chiplet 和相對簡單的互連,設計過程類似于具有幾個大塊的 SoC。“不同的團隊就形狀和面積、引腳位置及其連接等問題達成一致,” Siemens Digital Industries Software的 DRC 應用和 Calibre 設計解決方案營銷總監 John Ferguson 說。“至少對于數字設計而言,這種方法擴展了現有的布局布線技術。但隨著每個額外的 Chiplet 或互連的添加,它會變得更加復雜。”

最初,向異構架構的轉變是由系統公司推動的,這些系統公司希望提高其特定數據類型的性能,同時盡可能節省能源。現在,隨著芯片制造商尋求將這種級別的功率和性能優化擴展到更多市場,他們正在尋找方法來標準化和簡化這種優化,并使其更具成本效益。

Synopsys 營銷高級總監 Shekhar Kapoor 說:“正在發生的根本性宏觀變化是硅的顛覆。“直到最近,生活還是美好的,你可以指望轉移到下一個節點來實現性能和功能優勢。但是現在這些好處正在減少并且成本高得令人望而卻步,因此你真的必須考慮分解,并從成本的角度看待異構集成。分解本質上是將單個芯片拆分為多個芯片,這是推動多芯片設計的主要變化。這與整個 IP 重用概念相結合。chiplet 采取了一種曾經是主要芯片內部的塊的形式。現在,如果你將一個芯片分成多個裸片,其中一個塊或裸片就是一個 Chiplet ,你基本上可以在下一個設計中重復使用它。

不過,這需要一種不同的芯片設計思維方式。“一旦你從業界正在做的單一單片芯片轉向多 Chiplet 設計,你首先需要將系統級聚合工具的概念引入流程,”產品負責人 John Park 說。Cadence 定制 IC 和 PCB 集團管理集團總監。“你不是在設計一件事。你正在設計多個事物、多個 Chiplet 及其封裝排列的組合。”

優化 Chiplet到 Chiplet 的連接至關重要。但它也需要在其他芯片和 IP 以及潛在的其他系統的背景下看待。

“你需要在系統級別——而不是芯片級別——驗證 Chiplet A 通過封裝正確連接到 Chiplet B,”Park 說。“這就是我所理解的系統級設計的轉變。這是遠離單芯片的第一步。這是你必須做的第一件事 —— 安裝一個允許你組裝系統并對其進行優化的工具。它將成為你驅動系統 LVS(布局與原理圖)的黃金網表,這一點至關重要。系統 LVS 人員經常在他們的流程進行到一半時說,“我要如何驗證這個?” 如果他們沒有以正確的方式開始設計,他們就會發現自己遇到很多麻煩。”

最大的挑戰和限制涉及設計的功率、熱、應力和 EM-IR 元素。

“只有兩個維度,這些問題更容易解決,”Ferguson。“但是連接 Chiplet 的堆疊或復雜方式越多,這些挑戰就越困難。我希望我們會達到這樣一個地步,其中每一個都有限制,有一些合理的保護帶來防止出現問題。但是,由于連接這些東西的方式有這么多不同的可能組合,因此需要確定更多的約束條件,因此它變得更加復雜,并且涉及到每個堆疊/連接的項目。”

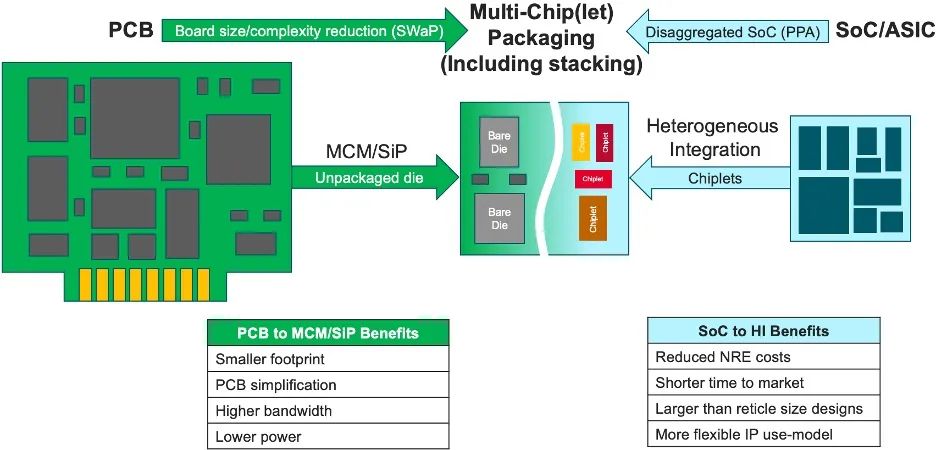

另一個考慮因素是,多模塊并不總是意味著 Chiplet。“有時是裸片,有時是 Chiplet,”Park 說。“直到大約三年前,它還是multi-chip modules (MCM)。現在我們說的是multi-die modules。它是關于將芯片從他們的封裝組件中取出并將裸芯片安裝在層壓基板上,這就是系統級封裝 (SiP)/MCM 模塊。這并不會因為我們進入 Chiplet的世界而消失。”

圖 1:SiP/MCM與基于chiplet的(異質集成)架構的對比。資料來源:Cadence

智能手機多年來一直采用 SiP,尤其是 RF 和模擬組件。“這當然是異構整合,”Park 說。“但我們不關心它們是在什么節點上構建的,它們是基于什么技術構建的。過去,我們只是不使用異構集成這個詞。”

Chiplet 是這種方法的下一個增長階段。“我們希望嘗試圍繞 Chiplet空間創建一些標準化,因為它真的很新,而且看起來很重要 - 不僅在數字領域,而且在堆棧內存方面也是如此,”應用程序開發大師 Matthew Ozalas 觀察到是德科技的工程師和科學家。“當我們展望無線 6G 系統時,Chiplet 可能是實現這一目標的唯一途徑。通常在進化中發生的事情是它從較低的層次或數字開始,因為芯片已經可以用功能塊構建。最后一個前沿領域始終是高頻 RF 微波,看起來 Chiplet 也會如此。”

原因是這種高頻射頻不是標準化的設計流程。“如果你看看數字芯片,這些芯片中有數十億個晶體管,沒有人可以在那里進行晶體管級別的設計,”Ozalas 說。“所以人們構建了這些功能塊,并將它們很好地集成在一起。例如,他們將在他們的數字芯片中構建一個加法器塊并將這些塊粘在一起。他們已經在進行這種塊功能/塊級設計。如果你是一名數字設計師,那么你并不是真正在使用晶體管。你真正遇到晶體管的唯一一次是當你遇到可靠性問題時,或者當其中一個晶體管出現問題時它吸收了太多電流或變得太熱,或者導致你的各種閂鎖問題出現問題。模擬緊隨其后,并且還有一組功能塊。然后,當我們談到射頻和微波時,幾乎全是晶體管。那里的設計人員正在研究晶體管。這是非常一觸即發的。盡管我們希望系統中有一個低噪聲放大器,但這些組件是高頻的。它們確實是功能塊,但不是那么標準。如果晶體管拓撲技術發生變化,這些東西不會隨之縮小。所以一切都需要改變。” 如果晶體管拓撲技術發生變化,這些東西不會隨之縮小。所以一切都需要改變。” 如果晶體管拓撲技術發生變化,這些東西不會隨之縮小。所以一切都需要改變。”

他說,這就是高頻塊最終成為最后邊界的原因。“它無處不在,Chiplet 也是如此。如果你要構建 Chiplet,則可以構建具有高頻電路的功能塊。但將它們放在一起,讓它們完美地工作更難。”

成本也是 Chiplet 越來越多的考慮因素。“人們正在為摩爾定律的終結而設計,”Cadence‘s Park 說。“他們正在從單片、巨大的 SoC 和 ASIC 轉向分解或模塊化的方法,在這種方法中,這些大芯片上的 IP 已被分解為 Chiplet。在這里,每個 Chiplet也可以根據最有意義的技術進行設計。”

這在某些方面簡化了事情,因為 PCIe 或 SerDes 等傳統 I/O 仍然可以與前沿邏輯結合使用。“這可能不會改變你在電路板上使用的東西與你在裸片上使用的東西之間的 I/O 連接,”Cadence IP 組產品營銷組總監 Wendy Wu 說。“但對于 Chiplet方法,設計團隊會使用更多新興的 die-to-die I/O,它的功耗非常低,五年前可能還不存在。”

Chiplet通常并排集成,但它們也可以使用中介層或 3D-IC 堆疊在 2.5D 封裝中。Park 預計硅中介層封裝不會繼續下去,并相信有機中介層和互連橋會得到推動。

多個模塊的額外問題

Multiple-die 系統的一個重要考慮因素是協同設計。“當工程團隊開始將這些系統組裝成組件時,他們無法知道限制是什么,直到他們定義了該組裝系統將是什么,”Siemens Digital 的 Calibre 接口和 mPower 產品管理高級總監 Joseph Davis 說行業軟件。“人們現在最想做的事情之一就是將來自不同制造商的 Chiplet組合在一起。這變成了一個系統問題,所有的模型和限制現在都來自不同的代工廠并流向第三方。從 IP 的角度來看,這是非常具有挑戰性的。如果你真的想從集成的角度突破你能做的事情的界限。

鑒于當今的復雜程度,每個堆棧都是獨一無二的。“你不能只說適用于 2.5D 的內容也適用于 3D,”Davis 指出。“當你開始構建這些東西時,你會遇到直接的技術兼容性問題。即使在一個代工廠內,每次客戶說,’嘿,我想做這個堆棧,‘他們必須定義,’我想把這個芯片和這個芯片放在一起,然后把這個芯片和這個中介層放在一起。然后,該代工廠必須與所涉及的 EDA 供應商合作,以提供所有相關的抵押品。你不能只是拿標準的 PDK 并在它們周圍放一些打包線。”

Synopsys 的 Kapoor 認為第一個挑戰是為心目中的產品定義規范。“例如,這可能是你的下一個移動設計或下一個數據服務器設計。所以現在你必須打破它。你怎么打破它?從系統功能的角度來看,硬件負責哪些部分?哪些部分由軟件處理?對于某些客戶來說,這很容易。這只是記憶凌駕于邏輯之上,或者說邏輯凌駕于記憶之上。但是當你拆分邏輯時,它會使事情變得非常復雜。它分為許多部分。關鍵部件是什么?GPU、CPU 和 I/O。如何將它們放入理想的包裝中?將使用哪種互連結構來幫助滿足某些限制和規范?這些決定過去非常簡單,只需在 PowerPoint 或 Excel 或 Visio 中完成。”

現在,更復雜的工具是探索目的所必需的。“這些工具必須更加復雜才能預先進行一些分析,”Kapoor 說。“Thermal 是典型的例子。除非設計團隊在進行 PCB 封裝設計或系統設計,否則他們從來不會考慮熱問題。現在這些問題很早就出現了,所以他們在進行早期架構設計時必須開始將熱力作為一個約束來考慮。一旦你決定了如何拆分設計,那么從封裝和連接的角度來看,最佳和最具成本效益的配置是什么?你還會滿足你的 PPA 嗎?PPA 總是會存在,現在你被分割開來了。這怎么會出現在畫面中?

啟用Chiplet

在過去五年左右的時間里,衍生設計變得更具挑戰性。Siemens的 Davis說:“如果你采用了一項核心技術,就會開始一種更長的跨越式發展。” “然后是下一項新技術,再次將其翻倍。所以業界開始說,‘等等,那是不是說Chiplet,可以讓我做2個、4個甚至8個模塊,把它放在substrate上,而無需進行新的流片?‘ 這一切都在組裝層面,而非硅,這非常有吸引力。”

這的確很有吸引力,但也并不簡單。對于初創公司甚至中型公司而言,這種方法的復雜性可能令人望而生畏。“對于一個單一裸片,有一大堆不同的集成商可以處理這種封裝模型和集成,并與代工廠合作。而現在你需要做一個自定義集合。能做到這一點的人要少得多。你現在是否將它帶到內部來執行此操作并驗證你的功能,因為現在在系統驗證方面需要做更多的工作?從系統的角度來看,可靠性驗證變得更加困難,自制還是外購決策也變得更加復雜。你的“做出”決定可能意味著雇用五個人而不是一個人。順便說一下,這個國家以前只有5個人有過這方面經驗。這在很大程度上是一種引導性的努力。’嗨,我們需要找一些有 5 年以上 SiP 和 3D stacking 經驗的人。嗯??等等,這個技術好像剛開始不到3年。”

在芯片的預計使用壽命內確保可靠性變得更具挑戰性。Kapoor 說:“因為你拆分了die,你現在有更多的互連,更多的接口,其中任何一個都可能失敗,任何一個都可能成為安全問題的切入點。” “關于KGD(known good die)有很多說法,但如何引入它的監控部分,以及如何確保它在整個流程中都是可觀察的、可優化的和可測試的?這些都是已經出現的新挑戰。”

除此之外,工程團隊要如何有效地完成以上這些工作?如果說單芯片設計很難,那么多芯片系統則需要新模型和標準化。

“ Chiplet的傳統工作方式是基于一些驅動和接收信號、處理 SD 和測試等的微緩沖器的 die-to-die 通信包裝器,”Cadence 的 Park 說。“我們在更大的芯片上看到了同樣的事情。但現在它們更小了,因為我們沒有一直延伸到電路板的大電容負載。這意味著你離開了諸如時序分析之類的世界,即觸發器到觸發器的時序,你在其中通過混合鍵在兩個不同的設備之間移動。在multiple-die設計中,需要驗證合規性,這可能基于 AIB、UCIe、BoW 或其他。有許多新興的 Chiplet標準,你現在需要驗證這些標準的信號完整性。你實質上是通過一些具有正確信號行為的互連通道來驗證收發器到接收器,并且該接口上沒有太多抖動或噪聲。這使得信號完整性成為一個系統級問題,業界已經這樣做了 40 多年。”

問題是芯片設計者不一定知道如何做到這一點。“數字方面的芯片設計人員只關心觸發器到觸發器的時序,這與理解信號完整性類型挑戰的重要性截然不同。出于所有這些原因,你需要把 multiple-die 設計和3D 異構集成當做一個系統來設計,而不是一個單片芯片。”

審核編輯 :李倩

-

芯片

+關注

關注

456文章

50938瀏覽量

424685 -

晶體管

+關注

關注

77文章

9705瀏覽量

138468 -

chiplet

+關注

關注

6文章

434瀏覽量

12606 -

奇異摩爾

+關注

關注

0文章

49瀏覽量

3444 -

先進封裝

+關注

關注

2文章

417瀏覽量

262 -

芯粒

+關注

關注

0文章

59瀏覽量

143

原文標題:進入 Chiplet 時代,設計將發生哪些轉變?

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

解鎖Chiplet潛力:封裝技術是關鍵

ESG報告進入“強信披”時代,企業面臨新挑戰

Chiplet在先進封裝中的重要性

Chiplet技術有哪些優勢

Chiplet將徹底改變半導體設計和制造

2035年Chiplet市場規模將超4110億美元

IMEC組建汽車Chiplet聯盟

Primemas選擇Achronix eFPGA技術用于Chiplet平臺

剖析 Chiplet 時代的布局規劃演進

Chiplet是否也走上了集成競賽的道路?

什么是Chiplet技術?

Chiplet技術對英特爾和臺積電有哪些影響呢?

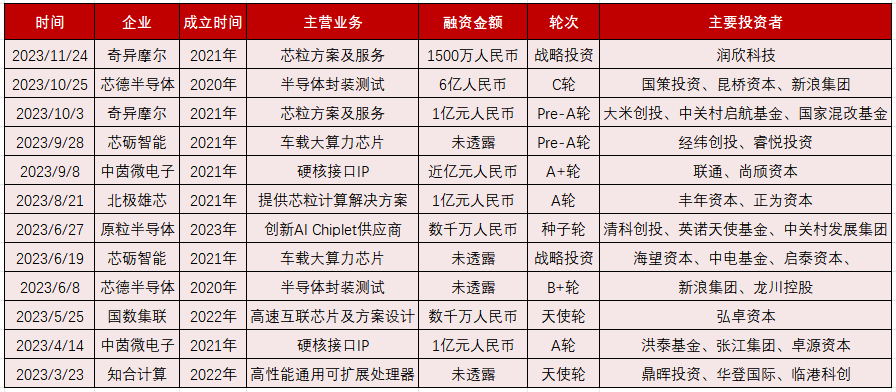

2023年Chiplet發展進入新階段,半導體封測、IP企業多次融資

進入Chiplet時代,設計將發生哪些轉變?

進入Chiplet時代,設計將發生哪些轉變?

評論