如今,算力極限挑戰(zhàn)正推動(dòng)著芯片設(shè)計(jì)的技術(shù)邊界。Chiplet的誕生不僅僅是技術(shù)的迭代,更是對(duì)未來(lái)芯片架構(gòu)的革命性改變。然而,要真正解鎖Chiplet技術(shù)的無(wú)限潛力,先進(jìn)封裝技術(shù)成為了不可或缺的關(guān)鍵鑰匙。

Chiplet:

超大規(guī)模芯片突破的關(guān)鍵策略

面對(duì)全球范圍內(nèi)計(jì)算需求的爆炸性增長(zhǎng),高性能芯片市場(chǎng)正以前所未有的速度持續(xù)擴(kuò)張。在這一背景下,Chiplet技術(shù)以其獨(dú)到的設(shè)計(jì)理念與先進(jìn)的封裝工藝,成為了突破傳統(tǒng)單芯片設(shè)計(jì)局限性的關(guān)鍵鑰匙。通過(guò)將多個(gè)高性能芯粒(Chiplet)巧妙集成,Chiplet技術(shù)不僅重塑了芯片設(shè)計(jì)的版圖,更為整個(gè)芯片產(chǎn)業(yè)開(kāi)辟了一條全新的發(fā)展路徑。

作為推動(dòng)算力躍升的前沿技術(shù),Chiplet展現(xiàn)出了多方面的顯著優(yōu)勢(shì)。

Chiplet技術(shù)可以克服算力墻、存儲(chǔ)墻、光罩墻、功耗墻四方面的限制,是突破先進(jìn)制程瓶頸的有效手段。

Chiplet基于硅片級(jí)IP重構(gòu)和復(fù)用的新架構(gòu),給縮短產(chǎn)品研發(fā)周期、提升良品率、降低成本等方面帶來(lái)巨大優(yōu)勢(shì)。

Chiplet的異質(zhì)異構(gòu)、跨尺度封裝特點(diǎn),集成芯片在尺寸、功能密度、總/局部功率密度、IO數(shù)量/密度/速率、互連帶寬/密度、熱流密度、時(shí)延、單位bit功耗等關(guān)鍵指標(biāo)具有顯著提升空間,可有效滿足各類應(yīng)用場(chǎng)景。

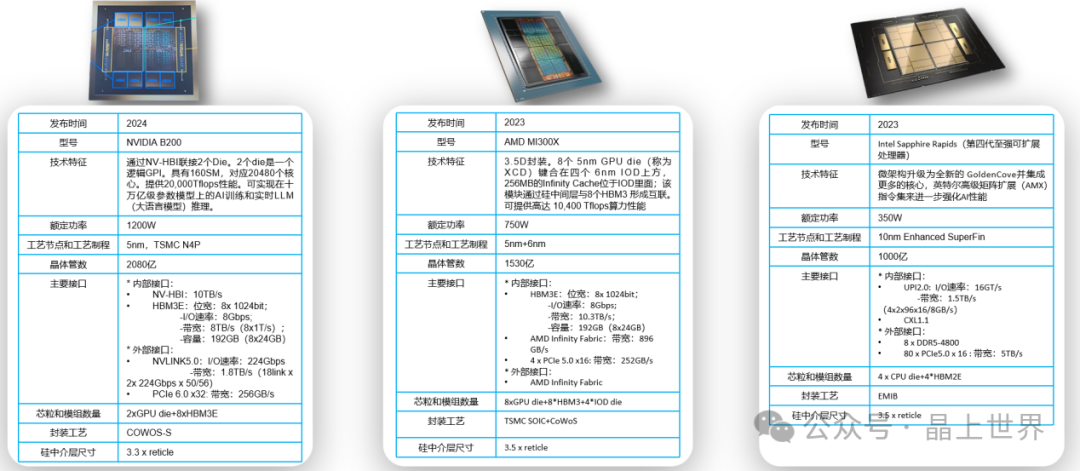

近兩年,隨著國(guó)際大廠紛紛將Chiplet技術(shù)應(yīng)用于其最新產(chǎn)品之中,超大規(guī)模芯片采用Chiplet設(shè)計(jì)已蔚然成風(fēng)。

Chiplet實(shí)現(xiàn)的關(guān)鍵

——先進(jìn)封裝

Chiplet技術(shù)的核心理念,在于通過(guò)先進(jìn)封裝技術(shù)的精妙運(yùn)用,實(shí)現(xiàn)大芯片的“化零為整”。因此,先進(jìn)封裝對(duì)于Chiplet而言,不僅是技術(shù)實(shí)現(xiàn)的基礎(chǔ),更是決定其未來(lái)發(fā)展空間與深度的關(guān)鍵技術(shù)。

Chiplet封裝應(yīng)用形式分為同構(gòu)和異構(gòu)。

同構(gòu)目前主要封裝形式為2D方案,即MCM,核心為D2D模塊,是通過(guò)將多個(gè)獨(dú)立的芯片(Chiplet)直接并排或堆疊在同一封裝基板上,利用引線鍵合(Wire Bonding)、倒裝芯片(Flip-Chip)或其他互連技術(shù)實(shí)現(xiàn)芯片間的電氣連接。

代表性封裝技術(shù):

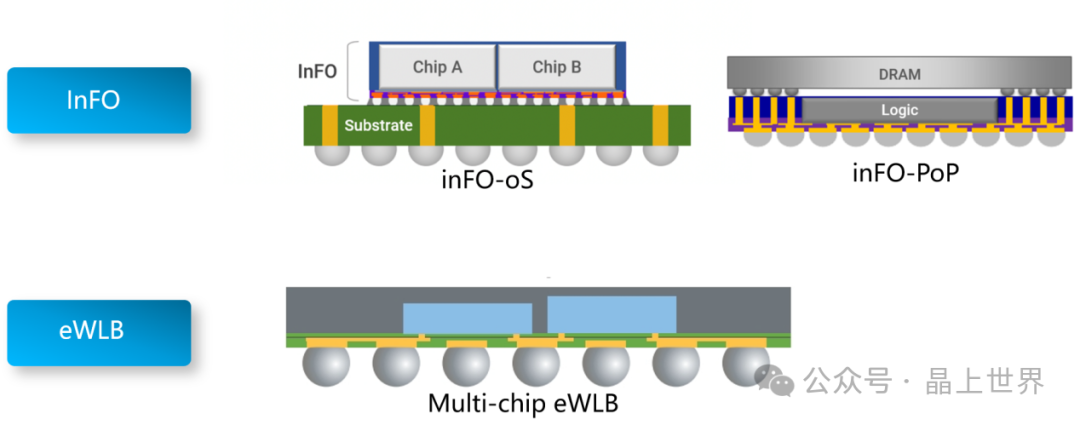

TSMC InFO:InFO是TSMC開(kāi)發(fā)的一種扇出型晶圓級(jí)封裝技術(shù)。該技術(shù)通過(guò)去除傳統(tǒng)的封裝基板,直接在晶圓上進(jìn)行封裝,從而實(shí)現(xiàn)更薄、更輕、成本更低的封裝解決方案。

日月光 eWLB:eWLB封裝技術(shù)是一種創(chuàng)新的晶圓級(jí)封裝技術(shù),由日月光半導(dǎo)體等公司開(kāi)發(fā)并推廣。該技術(shù)將晶圓直接嵌入到封裝基板中,并通過(guò)重新布線層(RDL)實(shí)現(xiàn)芯片間的互連。eWLB封裝技術(shù)結(jié)合了晶圓級(jí)封裝的高密度和低成本優(yōu)勢(shì)。

異構(gòu)目前主要封裝形式為2.5D,以HBM應(yīng)用為主,核心為控制模塊和HBM顆粒。代表性封裝方案主要分為三類:

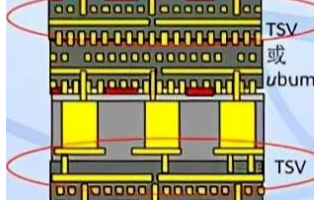

2.5D硅中介層

2.5D硅中介層封裝技術(shù)是通過(guò)在兩個(gè)或多個(gè)芯片之間插入一個(gè)硅材質(zhì)的中間層(即硅中介層),來(lái)實(shí)現(xiàn)芯片間的互連。這種技術(shù)可以有效縮短芯片間的互連距離,提高數(shù)據(jù)傳輸速度和帶寬,同時(shí)降低功耗和延遲。硅中介層上集成了大量的微凸點(diǎn)(microbumps)或TSV(Through Silicon Via,硅通孔)來(lái)實(shí)現(xiàn)芯片與中介層之間的電氣連接。

代表性封裝技術(shù):

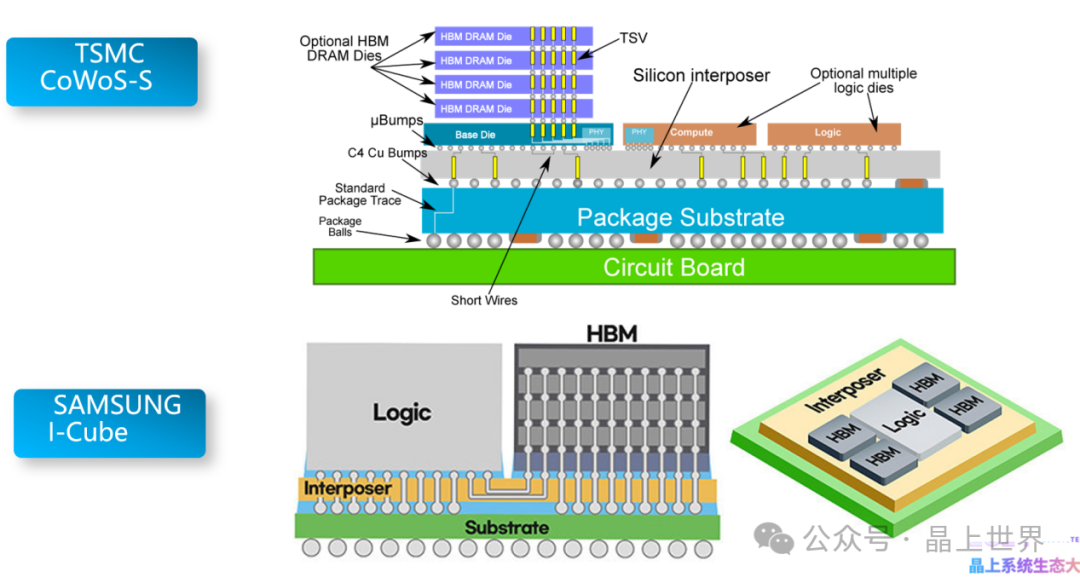

TSMCCoWoS-S:這是臺(tái)積電(TSMC)推出的一種基于硅中介層的Chiplet封裝技術(shù),其中“CoWoS”代表Chip-on-Wafer-on-Substrate,即芯片-晶圓-基板封裝。該技術(shù)利用硅中介層來(lái)連接多個(gè)高性能芯片,并通過(guò)微凸點(diǎn)或TSV實(shí)現(xiàn)高密度互連。

Samsung I-Cube:三星(Samsung)的Cube技術(shù)也是基于硅中介層的Chiplet封裝方案,它采用了先進(jìn)的堆疊和互連技術(shù),將多個(gè)芯片封裝在一個(gè)緊湊的立方體中,以實(shí)現(xiàn)高性能和低功耗。

2.5D硅橋

2.5D硅橋封裝技術(shù)通過(guò)直接在芯片之間構(gòu)建硅橋來(lái)實(shí)現(xiàn)互連,而不需要額外的硅中介層。這種技術(shù)可以減少封裝尺寸和成本,同時(shí)保持較高的數(shù)據(jù)傳輸速率和帶寬。硅橋通常通過(guò)TSV技術(shù)實(shí)現(xiàn),確保芯片間的高效電氣連接。

代表性封裝技術(shù):

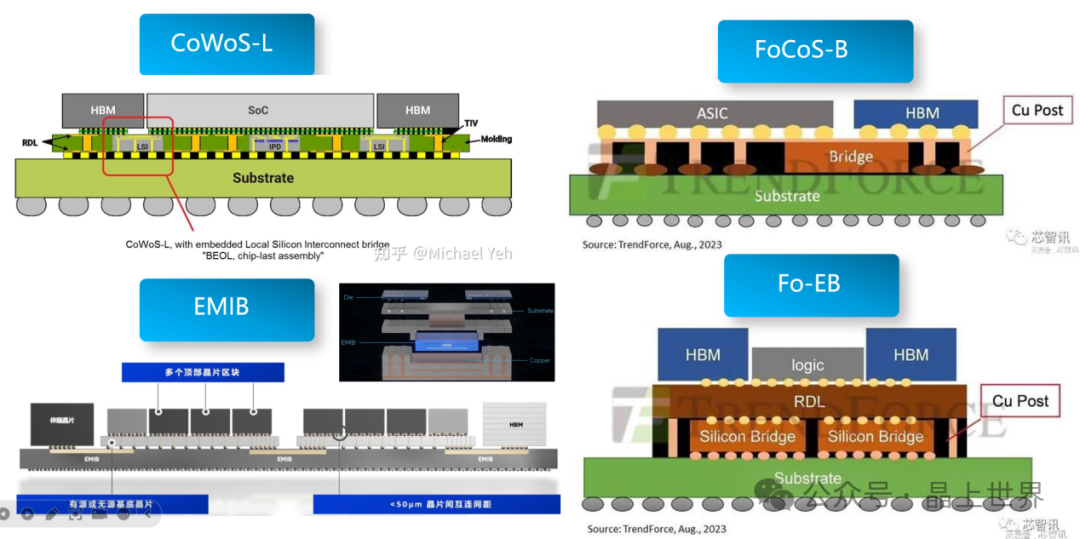

TSMCCoWoS-L:這是TSMC CoWoS系列中的一種變體,特別優(yōu)化了硅橋技術(shù),以實(shí)現(xiàn)更緊密的芯片間連接。該技術(shù)適用于需要高帶寬和低延遲的應(yīng)用場(chǎng)景,如高速網(wǎng)絡(luò)接口、高性能存儲(chǔ)等。

Intel EMIB:Intel推出的EMIB技術(shù)是一種創(chuàng)新的硅橋封裝方案,它允許將多個(gè)芯片直接嵌入到封裝基板上,并通過(guò)嵌入式硅橋?qū)崿F(xiàn)高速互連。該技術(shù)提高了系統(tǒng)的集成度和性能,降低了功耗和延遲。

FoCoS-B和Fo-EB:日月光集團(tuán)推出的FoCoS-B和Fo-EB也是基于硅橋技術(shù)的Chiplet封裝方案,盡管它們可能不如上述技術(shù)廣為人知,但在特定領(lǐng)域或應(yīng)用中仍具有優(yōu)勢(shì)。

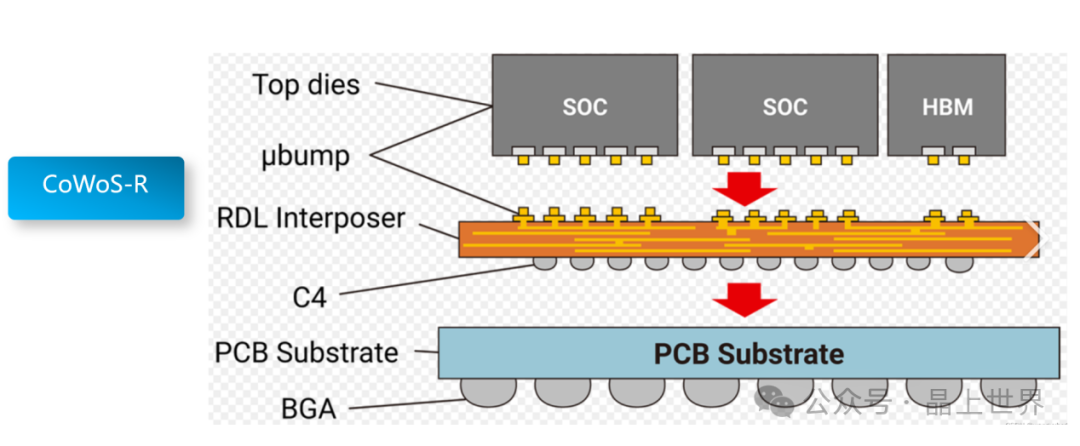

2.5D RDL中介層

2.5D RDL中介層封裝技術(shù)利用RDL在硅中介層上構(gòu)建復(fù)雜的互連網(wǎng)絡(luò)。RDL層可以包含多層金屬布線,用于實(shí)現(xiàn)芯片間的高密度、高性能互連。這種技術(shù)結(jié)合了硅中介層的優(yōu)勢(shì),同時(shí)提供了更靈活的布線能力和更高的集成度。

代表性封裝技術(shù):

CoWoS-R:作為TSMC CoWoS系列的一部分,CoWoS-R特別強(qiáng)調(diào)了RDL中介層的應(yīng)用。該技術(shù)通過(guò)精細(xì)的RDL布線,實(shí)現(xiàn)了芯片間的高效互連,適用于對(duì)性能、功耗和尺寸有嚴(yán)格要求的高端應(yīng)用。

Chiplet可以通過(guò)多種先進(jìn)封裝技術(shù)實(shí)現(xiàn),其中2.5D封裝技術(shù)尤為突出。隨著Chiplet的發(fā)展和封裝技術(shù)的迭代,Chiplet+先進(jìn)封裝技術(shù)組合將在滿足多樣化應(yīng)用需求方面帶來(lái)更多的創(chuàng)新和變革。

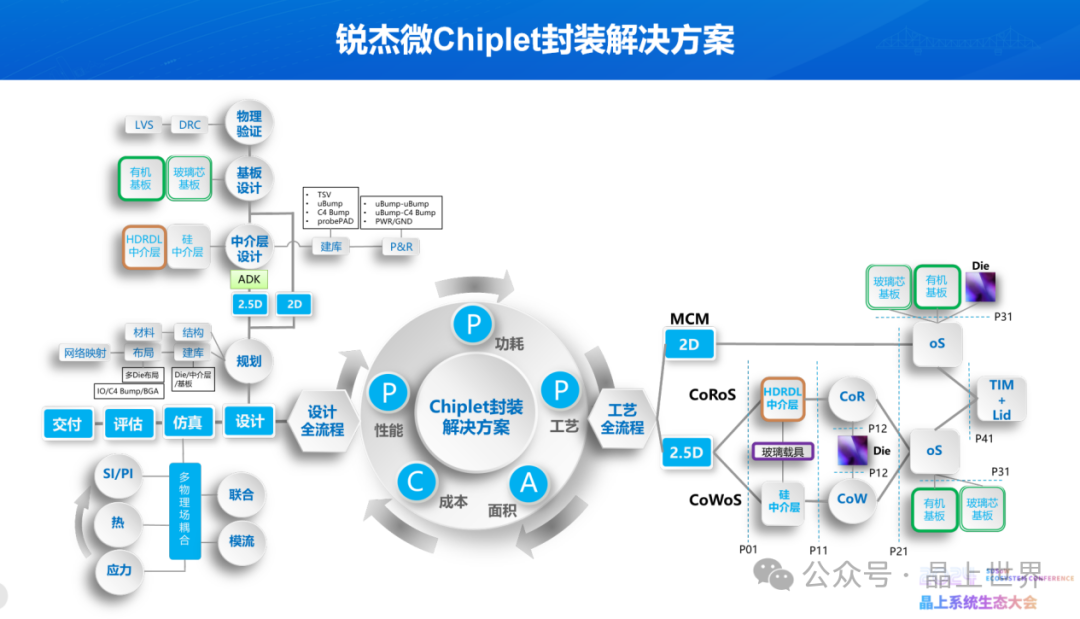

銳杰微 Chiplet封裝技術(shù)的創(chuàng)新先鋒

銳杰微科技專注于高端芯片設(shè)計(jì)和工藝全流程的封測(cè)制造,特別是在Chiplet封裝技術(shù)領(lǐng)域默默耕耘,積累了寶貴經(jīng)驗(yàn),掌握著包括2.5D硅中介層、硅橋及RDL中介層等在內(nèi)的多項(xiàng)核心技術(shù)。而且作為中國(guó)第三代封裝技術(shù)Chiplet標(biāo)準(zhǔn)的參與方,銳杰微在推動(dòng)行業(yè)標(biāo)準(zhǔn)制定方面也發(fā)揮了積極作用。

現(xiàn)階段,銳杰微主要瞄準(zhǔn)臺(tái)積電CoWoS-S封裝技術(shù)的替代工藝展開(kāi)開(kāi)發(fā),針對(duì)晶圓級(jí)系統(tǒng)的3D封裝方案也在布局當(dāng)中。

圍繞基于國(guó)內(nèi)的先進(jìn)工藝制程推出全國(guó)產(chǎn)化先進(jìn)封裝方案這一核心發(fā)展理念,銳杰微已構(gòu)建了一套涵蓋Chiplet產(chǎn)品設(shè)計(jì)仿真與工藝生產(chǎn)全流程的封測(cè)解決方案。

截至目前,銳杰微已完成采用不同封裝方案的多個(gè)Chiplet產(chǎn)品開(kāi)發(fā)和項(xiàng)目交付。下面進(jìn)行部分展示:

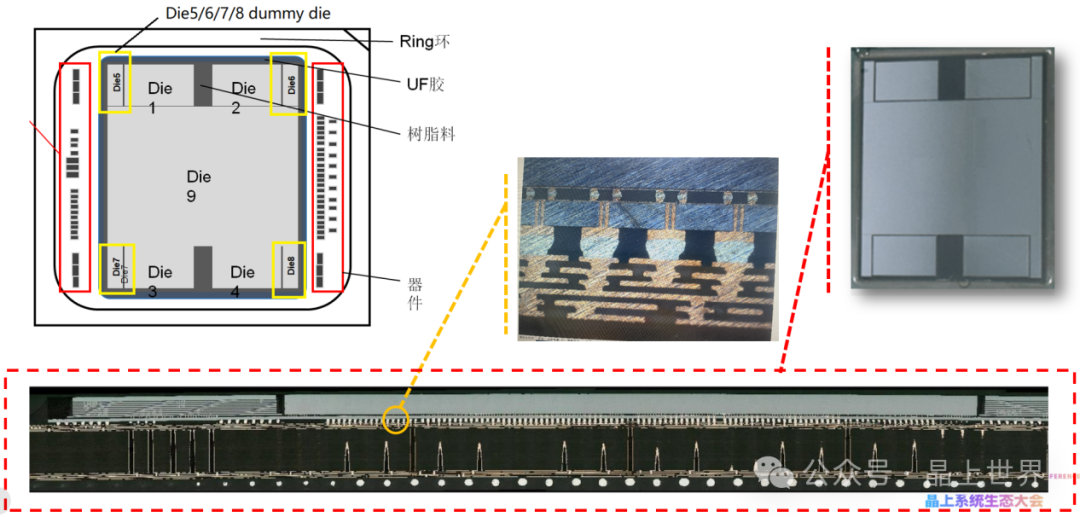

2.5D CoW組裝工藝驗(yàn)證

產(chǎn)品集成了4個(gè)HBM芯片,4個(gè)HBM dummy芯片,并利用4個(gè)結(jié)構(gòu)dummy堆疊仿真設(shè)計(jì)有效的控制了2.5D模組翹曲。CoW組裝C2 pillar直徑/節(jié)距為20um/40um,C4 bump為80um SAC焊球;并采用65nm雙大馬士革工藝節(jié)點(diǎn)的TSV中介層和18層ABF基板封裝。該項(xiàng)目驗(yàn)證了CoW組裝工藝技術(shù)路線可行性。

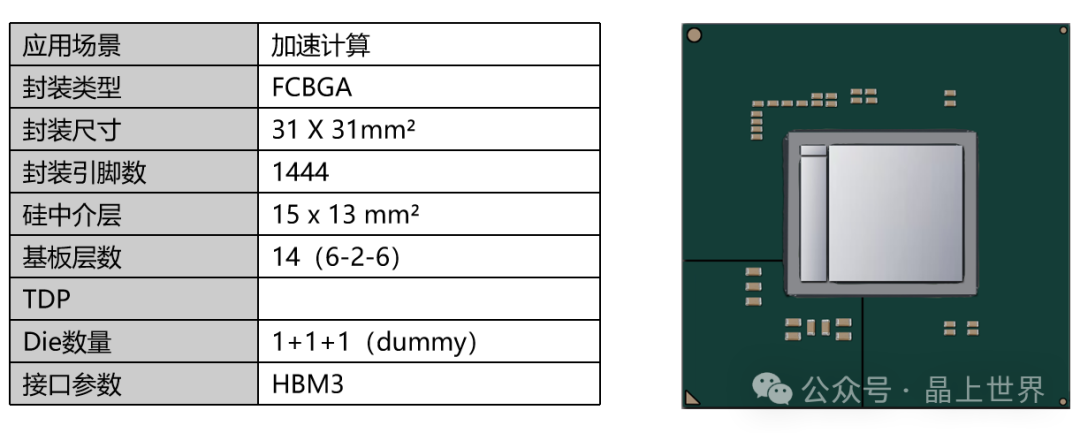

國(guó)產(chǎn)HBM方案

方案采用1+1結(jié)構(gòu),Logic Die+第四代HBM模組,通過(guò)硅中介層實(shí)現(xiàn)高速互聯(lián)。Logic Die采用了國(guó)內(nèi)先進(jìn)的工藝制程,Micro Bump直徑25um,Pitch為40um的工藝參數(shù);硅中介層采用了目前國(guó)內(nèi)領(lǐng)先帶DTC結(jié)構(gòu)的TSV工藝,有效降低PDN高頻段噪聲,改善AC IR-DROP指標(biāo),大幅提升大功率場(chǎng)景的電源網(wǎng)絡(luò)的完整性。

該項(xiàng)目從硅載板電路設(shè)計(jì)、基板電路設(shè)計(jì)到模型參數(shù)抽取、SI/PI完整性仿真、熱仿真分析、結(jié)構(gòu)應(yīng)力多物理場(chǎng)耦合仿真以及組裝工藝,銳杰微全程參與并提供了重要技術(shù)支撐。驗(yàn)證了國(guó)產(chǎn)2.5D+HBM的設(shè)計(jì)、Wafer工藝路線及封裝加工工藝路線。

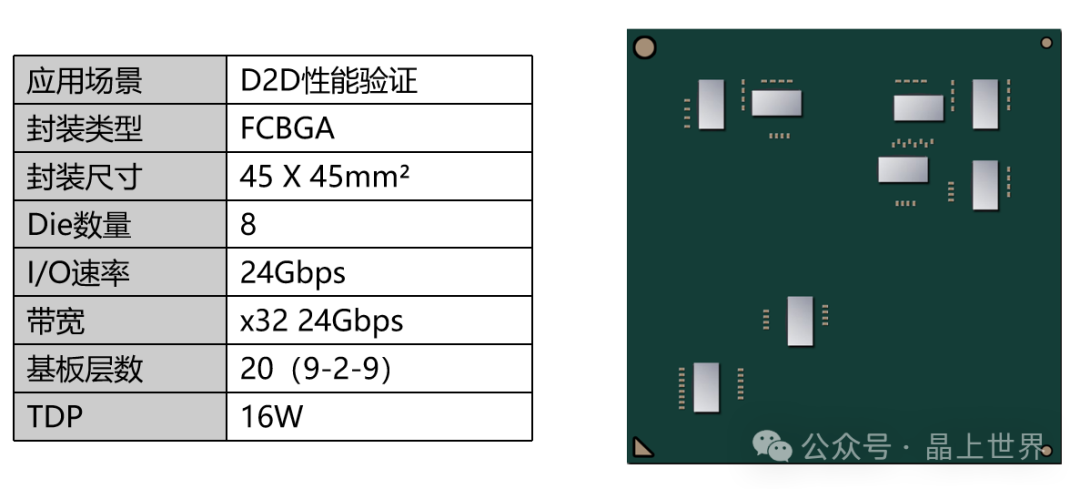

2D MCM —

UCIe1.0標(biāo)準(zhǔn) x32 24Gbps D2D

按照UCIe1.0標(biāo)準(zhǔn)給出的參考建議,要達(dá)到x32 24Gbps的I/O速率和帶寬,需要采用2.5D工藝才能滿足性能要求。考慮到成本因素,經(jīng)銳杰微和合作伙伴論證,通過(guò)設(shè)計(jì)+仿真反復(fù)迭代,在無(wú)中介層、搭載ABF基板條件下,達(dá)到了D2D最長(zhǎng)距離25mm和x32 24Gbps的性能指標(biāo)要求,探索出了一條高性能、低成本的Chiplet解決之路。該產(chǎn)品也是目前國(guó)內(nèi)性價(jià)比最好的產(chǎn)品。

作為Chiplet封裝技術(shù)的探索者,銳杰微正以扎實(shí)的技術(shù)基礎(chǔ)和行業(yè)參與,穩(wěn)步推動(dòng)技術(shù)革新。期待未來(lái)銳杰微繼續(xù)深耕國(guó)產(chǎn)化封裝解決方案,打造國(guó)內(nèi)高端核心芯片國(guó)產(chǎn)化封測(cè)服務(wù)最優(yōu)平臺(tái)。

-

封裝

+關(guān)注

關(guān)注

126文章

7935瀏覽量

143073 -

chiplet

+關(guān)注

關(guān)注

6文章

434瀏覽量

12604

原文標(biāo)題:解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

支持Chiplet的底層封裝技術(shù)

半導(dǎo)體芯片先進(jìn)封裝——CHIPLET

什么是Chiplet技術(shù)?chiplet芯片封裝為啥突然熱起來(lái)

北極雄芯開(kāi)發(fā)的首款基于Chiplet異構(gòu)集成的智能處理芯片“啟明930”

SiP與Chiplet成先進(jìn)封裝技術(shù)發(fā)展熱點(diǎn)

支持Chiplet的底層封裝技術(shù)

先進(jìn)封裝Chiplet全球格局分析

Chiplet技術(shù)給EDA帶來(lái)了哪些挑戰(zhàn)?

先進(jìn)封裝Chiplet的優(yōu)缺點(diǎn)與應(yīng)用場(chǎng)景

先進(jìn)封裝技術(shù)是Chiplet的關(guān)鍵?

探討Chiplet封裝的優(yōu)勢(shì)和挑戰(zhàn)

Chiplet關(guān)鍵技術(shù)與挑戰(zhàn)

Chiplet主流封裝技術(shù)都有哪些?

先進(jìn)封裝 Chiplet 技術(shù)與 AI 芯片發(fā)展

什么是Chiplet技術(shù)?

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

評(píng)論