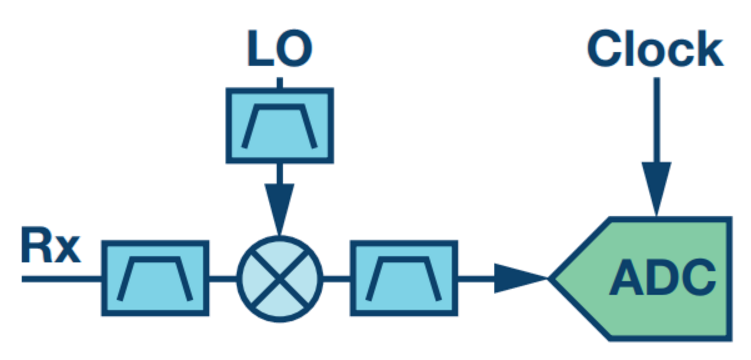

模數轉換器(ADC)在相當長的一段時間內一直是通信接收器設計的主要內容。隨著通信技術的不斷發展,消費者要求更快的數據速率和更便宜的服務。啟用這項技術的回程服務提供商面臨著二分法的情況。更快的數據速率意味著更多的帶寬,這意味著更快的數據轉換器可以將模擬無線電波轉換為數字處理。然而,更快的數據轉換器(GSPS或每秒千兆采樣轉換器)——被廣泛稱為RF采樣ADC——也會產生大量數據,必須在這些DSP芯片中以更高的速度進行處理。這不可避免地增加了無線電接收器的操作成本。

解決方案在于對構成RF采樣ADC的硅進行巧妙設計。利用硅處理的進步(謝謝摩爾定律),RF采樣ADC混合在定制數字處理模塊中,與現有FPGA相比,功耗和面積效率更高。使用這些數字信號處理模塊還會導致較低的數據速率,從而可以使用成本更低的FPGA。這對運營商來說是一個雙贏的局面,因為他們可以使用這些GSPS ADC進行高頻采樣,使用內部數字下變頻器(DDC)快速處理數據,并以可管理(低)數據速率將其發送到更便宜的FPGA(或現有一代ASIC)進行進一步的基帶處理。

將RF采樣ADC與DDC配合使用的另一個優點是,這為實現雙頻段無線電系統提供了一種更靈活、更緊湊、更具成本效益的方法。雙頻無線電系統已經存在多年了。傳統上,基站系統設計人員通過使用兩條獨立的無線電路徑(每個頻段一條)來實現雙頻無線電系統。本文討論一種利用多頻段無線電接收器的方法,該方法使用AD9680等RF采樣ADC對兩個廣泛使用的獨立頻段進行數字化和處理。本文的第一部分介紹了框圖級實現,并討論了將GSPS ADC用于雙頻段無線電系統的優勢。本文的第二部分將討論TDD LTE頻段34和39(分別稱為頻段A和頻段F)的實現和數據分析,并通過數據分析顯示轉換器性能。

傳統雙頻無線電接收器

為了滿足客戶對雙頻無線電的需求并滿足整體系統級性能,基站設計人員采用了他們最了解的方法:復制無線電的設計兩次,并為每個頻段調諧一次。這意味著設計人員必須將兩個獨立的無線電硬件設計調諧到客戶選擇的兩個頻段。

例如,如果需要構建一個可以支持TDD LTE頻段34(頻段A:2010 MHz至2025 MHz)和頻段39(頻段F:1880 MHz至1920 MHz)的無線電接收器1,設計師將打包兩個無線電接收器設計。TDD LTE頻段的頻率規劃如圖1所示。

圖1.顯示 TDD LTE 頻段 34 和 39 的頻率計劃。

設計雙頻無線電接收器以適應這些頻段的傳統方法是實現兩個獨立的接收器鏈,每個頻段一個。雙頻無線電接收器的框圖示意圖如下圖2所示。2

圖2.雙頻無線電接收器設計的傳統方法。

圖2顯示了雙頻無線電的傳統實現。這種實現的成本相當高,因為它實際上是一個系統中的兩個無線電接收器。每個處理元素都是重復的,以適應相應的波段。這也適用于 FPGA 資源。每個處理元件都是重復的,以適應相應的頻段,從而導致FPGA資源的重復,增加系統成本和復雜性,以及額外的功耗。在FPGA接口方面,FPGA資源必須加倍才能容納兩個ADC數據流。圖 3 顯示了 FPGA I/O 資源需求或雙頻無線電接收機系統設計的框圖。它顯示了LVDS和JESD204B ADC接口。LVDS數據速率較低,但FPGA需要更高的I/O數量。JESD204B接口需要的FPGAI/O資源數量較少,但通道速率可能更高,這可能需要更昂貴的FPGA。

圖3.雙頻無線電接收機傳統方法的FPGA接口要求。

采用RF采樣(GSPS)ADC的雙頻無線電接收器

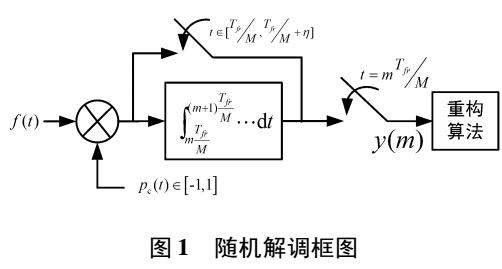

RF采樣或GSPS ADC可以提供系統設計的靈活性。通過利用深亞微米工藝技術,GSPS ADC可以封裝數字處理模塊,與FPGA相比,這些模塊能夠以更低的功耗快速處理數據。RF采樣ADC的核心是一個高帶寬模擬采樣內核,該內核以GHz速度采樣。在模擬內核之后是大量的數字信號處理元件。這些數字下變頻器可用于提取相應的頻段。雙頻段接收器的RF采樣ADC設置內部框圖如圖4所示。DDC除了處理信號外,還會降低JESD204B通道上數據的通道速率。

圖4.RF采樣ADC的框圖表示,顯示內部DDC。

通過增加數字信號處理模塊,GSPS ADC現在可以單手容納兩個頻段進行處理。這對運營商來說是一個雙贏的局面,因為他們可以使用這些RF采樣ADC進行高頻采樣,使用內部數字下變頻器(DDC)快速處理數據,并以可管理(低)數據速率將其發送到更便宜的FPGA(或現有一代ASIC)以進行進一步的基帶處理。這些ADC提供的高帶寬前端使系統設計人員能夠捕獲寬頻率(例如兩個無線電頻段)并將其數字化以進行信號處理。下面的圖5顯示了一個雙頻段接收器系統,該系統使用RF采樣ADC和內部DDC來提取頻段。與圖2中的實現方案相比,使用RF采樣ADC的雙頻接收器在實現過程中要簡單得多。在此實現中,RF被混頻到數百MHz寬的高IF,而傳統的雙頻段方法則為數十MHz寬。BPF 和 VGA 階段是可選的,取決于預期的系統性能級別。

圖5.使用RF采樣ADC和內部DDC提取頻段的雙頻段無線電接收器。

下面介紹了將RF采樣ADC用于雙頻段無線電系統的一些優點:

更簡單的前端設計

采用RF采樣ADC的雙頻段無線電系統設計大大簡化了前端網絡。對于初學者來說,只需要一個前端設計,而不是兩個(每個頻段一個)。這大大減少了系統主板的物料清單。然后是AAF(抗混疊濾波器)要求,即兩個IF轉換器情況下的帶通濾波器(BPF)與GSPS ADC情況下的低通濾波器(LPF)相比。這是因為GSPS ADC對輸入信號進行了過采樣。3,4現在數據被過采樣,數字下變頻器可以完成抽取和濾波工作。如果頻率規劃使得二次和三次諧波落出帶外,則降低了對AAF的要求。

更低的系統功耗,更小的外形尺寸

與圖2所示的兩個LNA、兩個混頻器和兩個中頻ADC不同,在RF采樣情況下只需要一個前端(圖5)。從系統級功耗考慮來看,這可節省大量功耗。較低的系統功耗與對更簡單前端設計的需求相結合,允許系統以更小的外形尺寸制造。

更高效的 FPGA 利用率

當使用RF采樣ADC實現雙頻段無線電系統時,DDC用于提取各個頻段。由于DDC抽取數據,輸出采樣速率降低。這使得JESD204B接口具有許多靈活的配置。例如,如果雙通道ADC以1 GSPS采樣并處于全帶寬模式,則在四個通道上以10 Gbps/通道計算線速。ADI公司JESD204B轉換器的線速計算如下:

哪里

M = 轉換器數量(在本例中為 2)

N' = 每個樣本的轉換器位數(在本例中為 16)

10/8 = 8B10B 開銷

F外= 輸出采樣率(Fsample/Decimation_Ratio;在本例中,全帶寬為 Decimation_Ratio = 1)

L = JESD204B通道數(在本例中為4)

例如,如果同一雙通道ADC在分進制乘8的配置中總共使用四個DDC,則根據通道數,ADC將支持許多配置。輸出采樣速率變為125 MSPS(1 GSPS ÷ 8)。表 1 列出了不同的配置:

表1

| DDC 配置 | M | L |

線速(千兆字節/通道) |

|

真正 |

4 | 1 | 10 |

| 真正 | 4 | 2 | 5 |

| 復雜 | 8 | 2 | 10 |

| 復雜 | 8 | 4 | 5 |

這些靈活的配置使系統設計人員可以自由地使用具有更高線速但更好的I/O通道密度的昂貴FPGA,或者使用具有線速限制的現有FPGA/ASIC。

結論

GSPS ADC在深亞微米硅工藝中的出現,開創了無線電架構討論和設計的新時代。GSPS ADC具有高帶寬采樣內核和數字下變頻器選項,為重新思考和重新定義無線電架構提供了靈活的途徑,以滿足消費者不斷增長的需求。這些GSPS ADC提供的功耗和空間的減少將降低這些無線電盒的擁有成本。采用JESD204B接口的當前一代ADC提供的靈活輸出選項不會使系統設計人員受限于使用昂貴的高線速FPGA或數字邏輯。

審核編輯:郭婷

-

接收器

+關注

關注

14文章

2478瀏覽量

72082 -

接收機

+關注

關注

8文章

1184瀏覽量

53567 -

adc

+關注

關注

99文章

6531瀏覽量

545407

發布評論請先 登錄

相關推薦

基于射頻采樣的短波偵察接收機設計

中頻采樣多模式數字接收機的設計與實現

衛星導航軟件接收機多采樣率信號處理技術

寬帶數字信道化接收機的FPGA實現

高性能、雙通道IF采樣接收機

利用多頻段無線電接收機——使用RF采樣ADC

用千兆放大器跨越新的多波段接收機前沿

壓縮采樣接收機抗ADC非線性影響

CN0140 高性能、雙通道IF采樣接收機

利用千兆采樣ADC跨越多頻段接收機的新前沿

利用千兆采樣ADC跨越多頻段接收機的新前沿

評論