本篇博文旨在演示如何通過 NoC 從 Versal 應(yīng)用處理單元 (APU) 訪問 AXI BRAM。

設(shè)計示例是使用 Vivado 2020.2 版本創(chuàng)建的,評估板使用的是 VCK190 評估板。

Versal

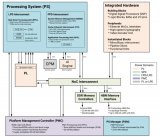

Versal 架構(gòu)將“Scalar Engine”(標量引擎)、“Adaptable Engine”(自適應(yīng)引擎)和“Intelligent Engine”(智能引擎)這三種不同類型的引擎與豐富的連接和通信功能以及片上網(wǎng)絡(luò) (NoC) 有機結(jié)合,從而支持實現(xiàn)覆蓋整個器件的無縫式存儲器映射訪問。

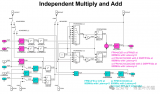

智能引擎包括:

SIMD VLIW AI 引擎,適用于自適應(yīng)推斷和高級信號處理計算

DSP 引擎,適用于定點運算、浮點運算和復雜的 MAC 運算。

自適應(yīng)引擎將可編程邏輯塊與存儲器有機結(jié)合,它具備專為應(yīng)對高計算密度需求而設(shè)計的架構(gòu)。

標量引擎包括 Arm Cortex-A72 和 Cortex-R5 處理器,支持計算密集型任務(wù)。

片上網(wǎng)絡(luò) (NoC)

片上網(wǎng)絡(luò) (NoC) 是一個 AXI 互連網(wǎng)絡(luò),用于在可編程邏輯 (PL)、處理器系統(tǒng) (PS) 和其它硬核塊中的 IP 端點之間共享數(shù)據(jù)。

此基礎(chǔ)架構(gòu)覆蓋整個器件,基于專有的切換開關(guān)形成高速集成的數(shù)據(jù)路徑。

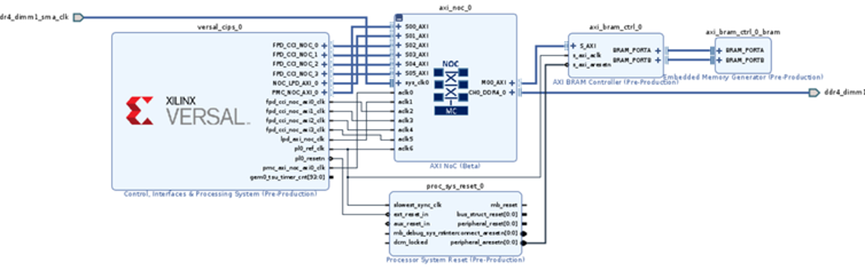

模塊框圖

Vivado 步驟

步驟 1:

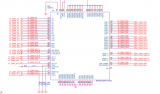

以 VCK190 評估板為目標創(chuàng)建工程,并在 IP integrator 內(nèi)創(chuàng)建塊設(shè)計。

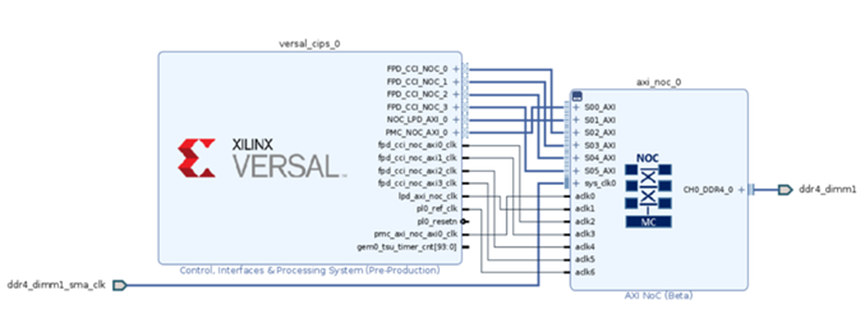

步驟 2:

添加 versal_cips IP (Control, Interfaces and Processing System),并運行塊自動化設(shè)置。在設(shè)置中配置 NoC 的存儲器控制器 (DDR4),并將 PL 時鐘和 PL 復位的數(shù)量配置為 1。

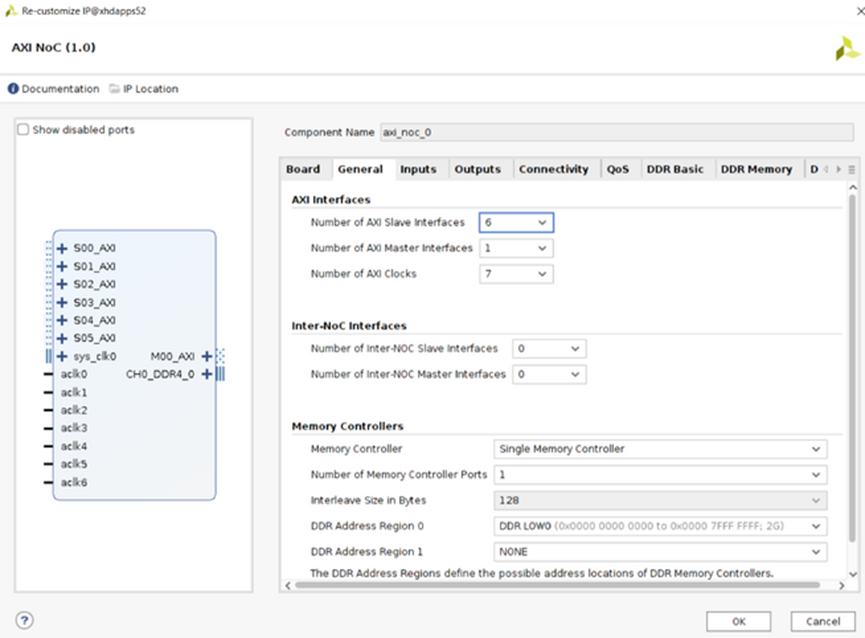

步驟 3:

雙擊打開 NoC IP,在“General”(常規(guī))選項卡中進行以下設(shè)置:

Number of AXI Master Interfaces(AXI 主接口數(shù))= 1

Number of AXI Clocks(AXI 時鐘數(shù))= 7

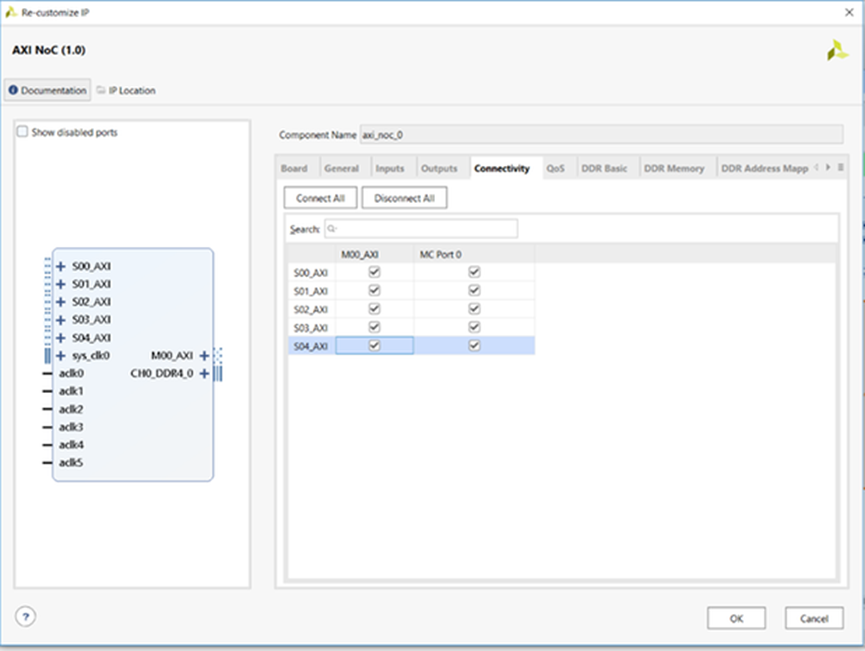

步驟 4:

轉(zhuǎn)至“Connectivity”(連接)選項卡,檢查 S0xAXI 與 M00_AXI 之間的連接,然后單擊“OK”(確定)。

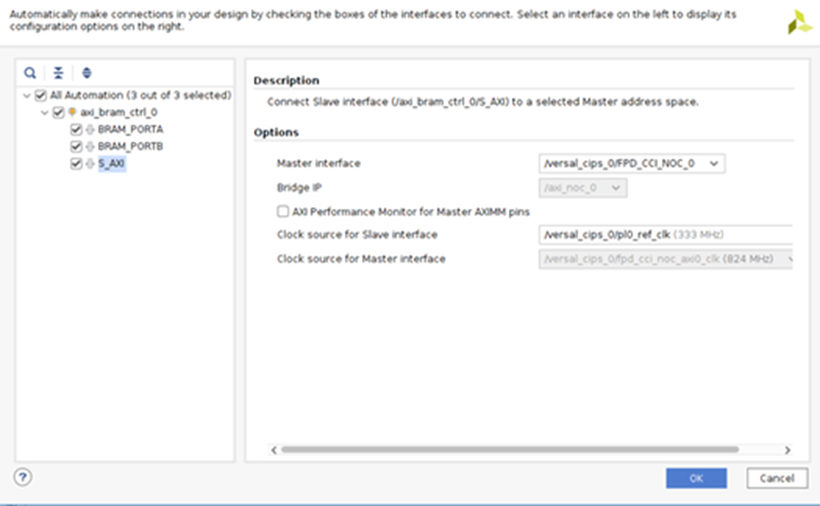

步驟 5:

將 AXI BRAM 添加到塊設(shè)計中,單擊“Run Connection Automation”(運行自動連接),然后選中 pl_clk0 作為從接口的時鐘源。

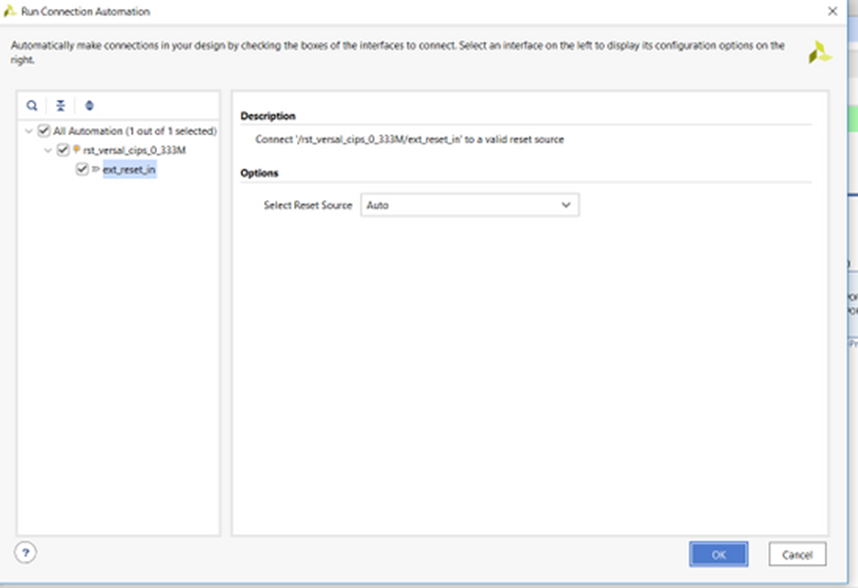

步驟 6:

再次運行“Run Connection Automation”,配置 ext_reset_in接口。

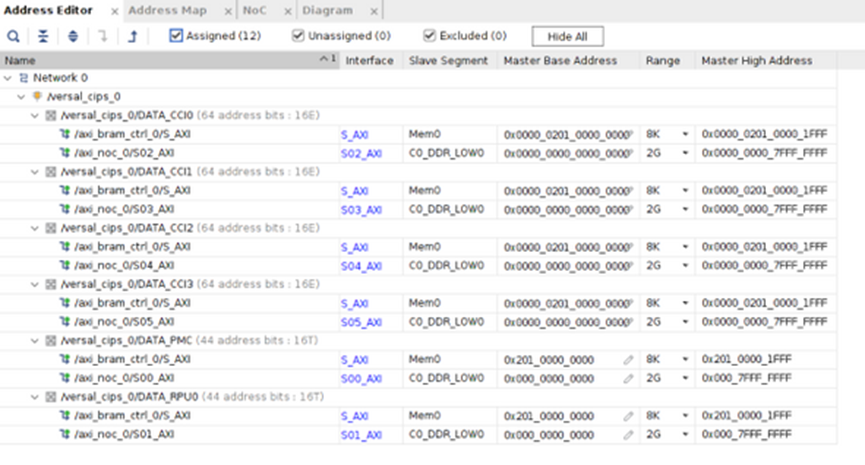

步驟 7:

運行“validation”(確認)步驟,確認成功后,檢查“Address Editor”(地址編輯器)選項卡。

步驟 8:

為 BD 創(chuàng)建頂層文件,運行綜合與實現(xiàn),然后生成器件鏡像。

步驟 9:

導出硬件設(shè)計以獲取 XSA 文件。

Vitis 步驟

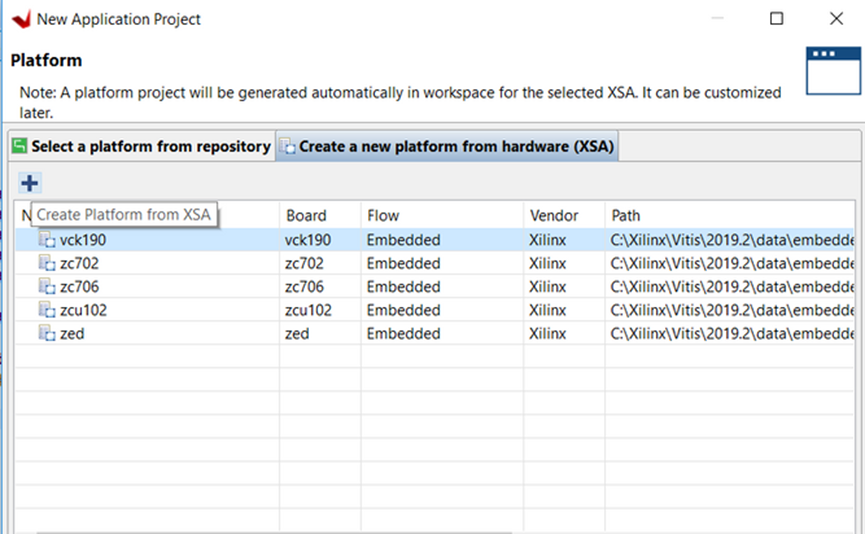

步驟 1:

在 Vitis 中創(chuàng)建新的應(yīng)用工程,然后切換至“Create a new platform from hardware”(基于硬件創(chuàng)建新平臺)選項卡。

單擊“+”,選擇從 Vivado 導出的 XSA 文件。

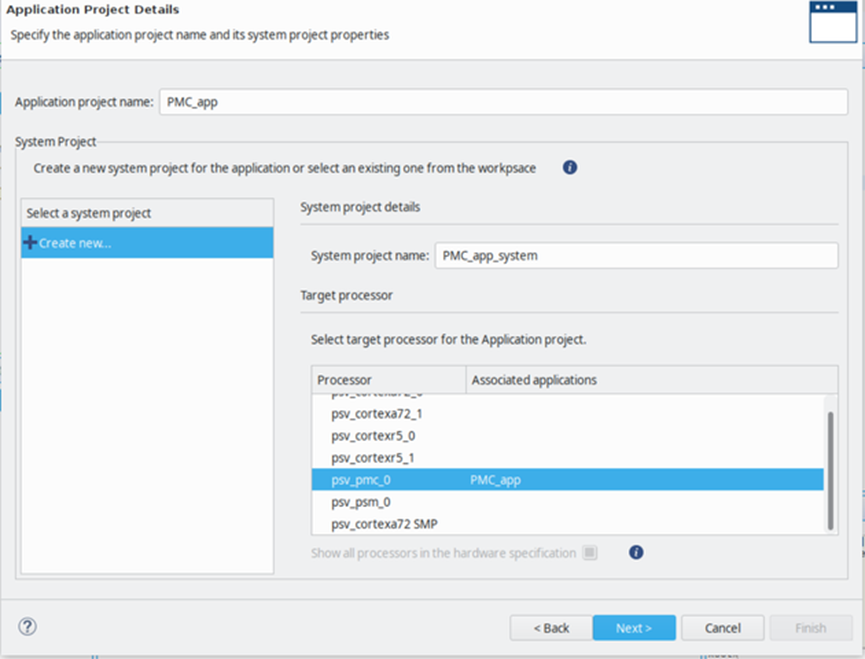

步驟 2:

提供工程名稱,并選擇處理器。

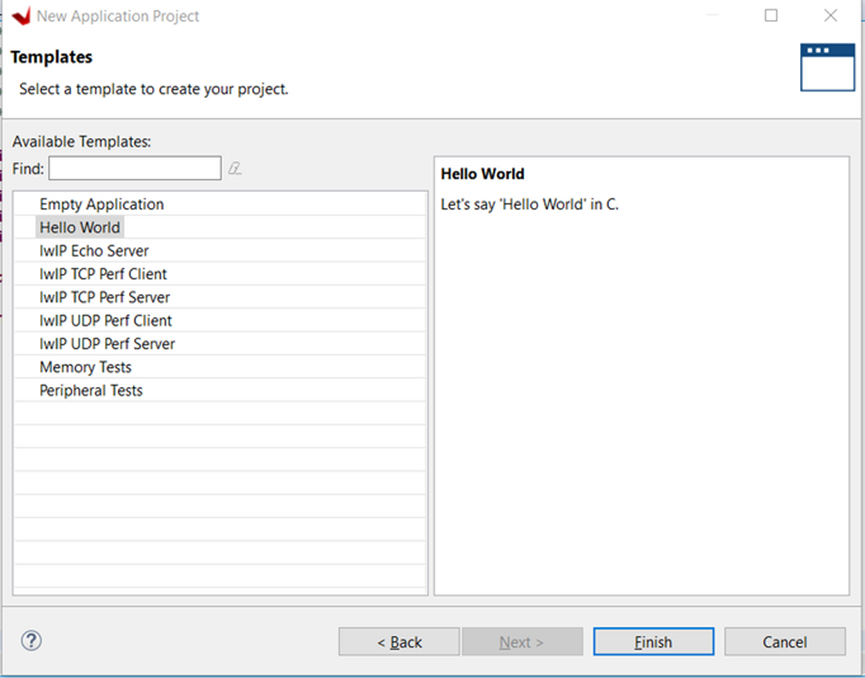

步驟 3:

選擇 Hello World 模板,然后單擊“Finish”(完成)。

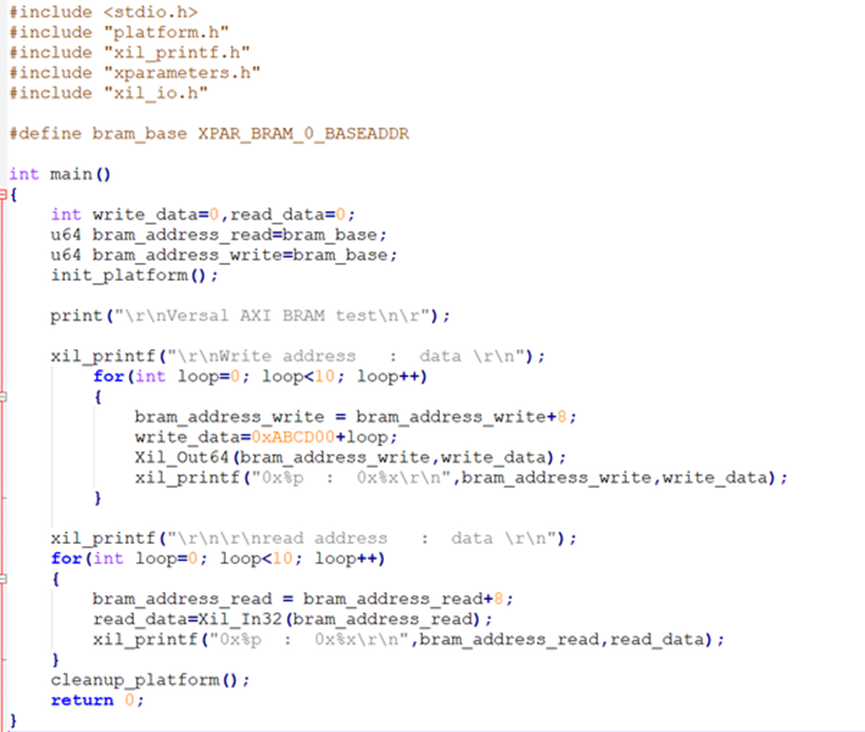

代碼修改

創(chuàng)建完應(yīng)用工程后,在 main.c 中修改代碼對 AXI BRAM進行讀寫。

Xil_Out64 函數(shù)用于將數(shù)據(jù)寫入 64 位地址,而Xil_In32 函數(shù)則用于地址中讀取 32 位數(shù)據(jù)。

示例:

寫入數(shù)據(jù) API

Xil_Out64(bram_address_write,write_data);

讀取數(shù)據(jù) API

read_data=Xil_In32(bram_address_read);

代碼快照:

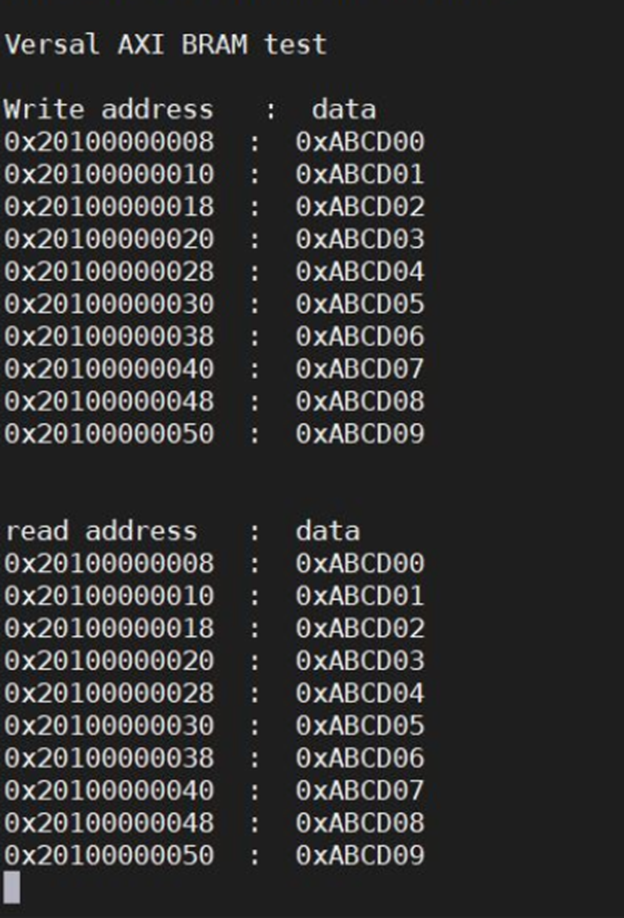

運行設(shè)計

連接到VCK190 評估板,并設(shè)置啟動模式為 JTAG 啟動模式,然后運行應(yīng)用。

控制臺輸出示例:

審核編輯:郭婷

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

349760 -

引擎

+關(guān)注

關(guān)注

1文章

361瀏覽量

22609

發(fā)布評論請先 登錄

相關(guān)推薦

ZYNQ基礎(chǔ)---AXI DMA使用

如何通過PMC_GPIO喚醒AMD Versal? Adaptive SoC Linux系統(tǒng)

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

SoC設(shè)計中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

基于FPGA設(shè)計的BRAM內(nèi)部結(jié)構(gòu)

FPGA通過AXI總線讀寫DDR3實現(xiàn)方式

用于高級應(yīng)用處理器的電源管理單元LP3971數(shù)據(jù)表

用于高級應(yīng)用處理器的電源管理單元LP3972數(shù)據(jù)表

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計算加速平臺之 Versal 介紹(2)

AMD Versal AI Edge自適應(yīng)計算加速平臺之Versal介紹(2)

Versal FPGA中的浮點計算單元DSPFP32介紹

如何通過NoC 從 Versal應(yīng)用處理單元訪問AXI BRAM

如何通過NoC 從 Versal應(yīng)用處理單元訪問AXI BRAM

評論