數(shù)字硬件建模SystemVerilog-決策語(yǔ)句-if-else語(yǔ)句

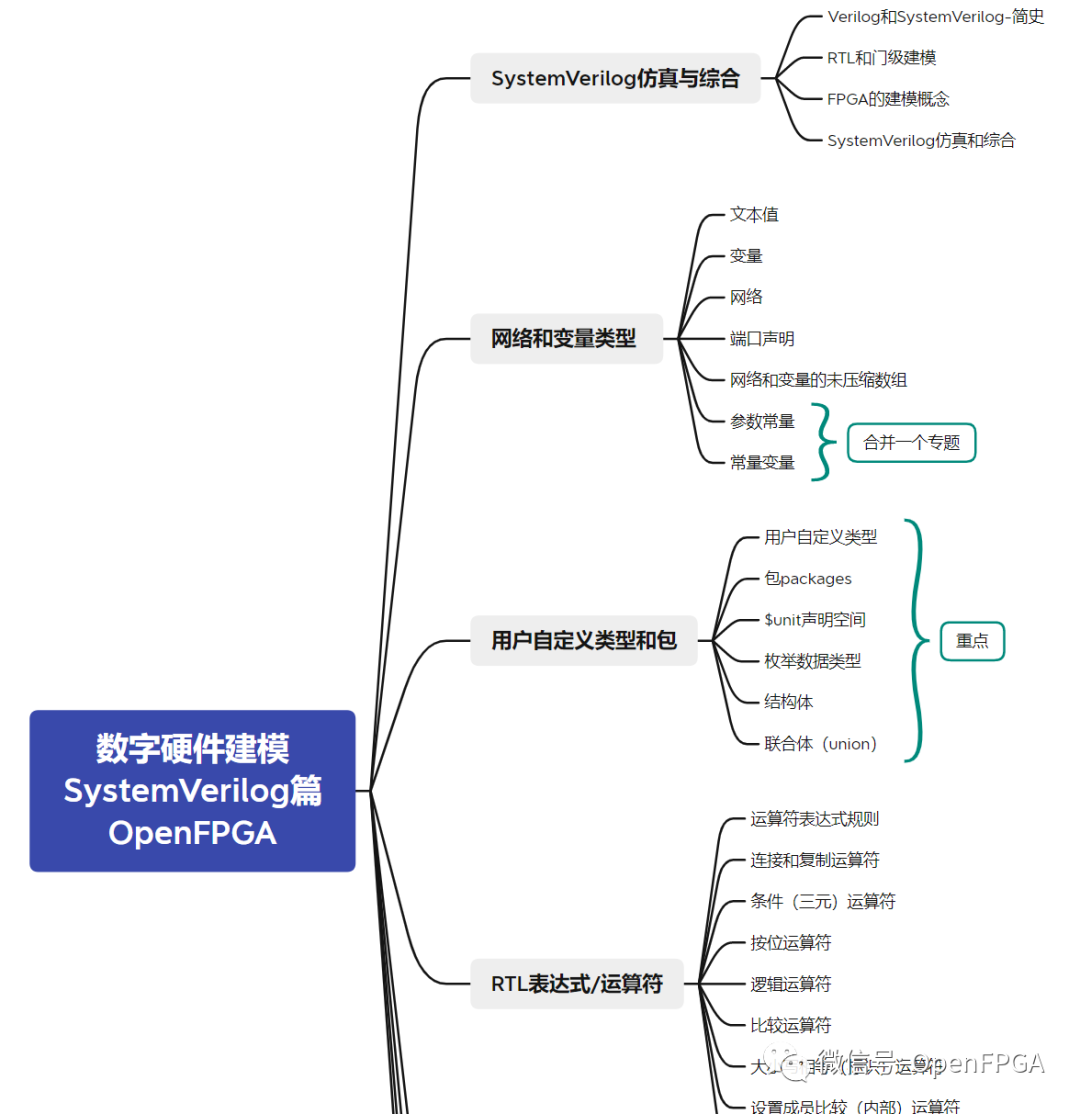

經(jīng)過(guò)幾周的更新,SV核心部分用戶(hù)自定義類(lèi)型和包內(nèi)容已更新完畢,接下來(lái)就是RTL表達(dá)式和運(yùn)算符。

馬上HDLBits-SystemVerilog版本也開(kāi)始準(zhǔn)備了,基本這一部分完成后就開(kāi)始更新~

決策語(yǔ)句(Decision statements)允許程序塊的執(zhí)行流程根據(jù)設(shè)計(jì)中信號(hào)的當(dāng)前值分支到特定語(yǔ)句。SystemVerilog有兩個(gè)主要的決策語(yǔ)句:if…else語(yǔ)句和case語(yǔ)句,使用關(guān)鍵字case、case…inside,casex和casez。

介紹

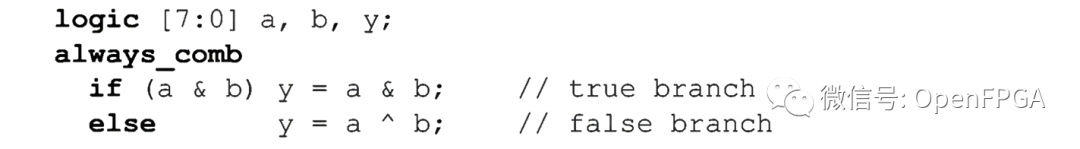

if-else語(yǔ)句對(duì)表達(dá)式求值并執(zhí)行兩個(gè)可能的分支之一,即true分支或false分支。

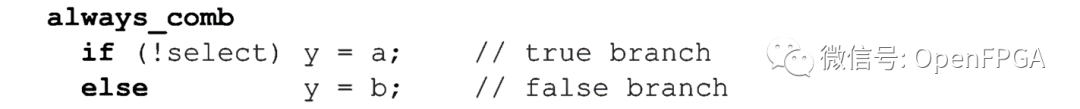

if-else表達(dá)式可以是任何向量大小的網(wǎng)絡(luò)或變量,也可以是運(yùn)算的返回值,如果表達(dá)式的一個(gè)或多個(gè)位設(shè)置為l,則向量表達(dá)式的計(jì)算結(jié)果為true。如果表達(dá)式的所有位均為0,則表達(dá)式的計(jì)算結(jié)果為false。例如:

a和b的按位AND運(yùn)算的結(jié)果是8位向量(因?yàn)閍和b都是8位向量)。如果AND操作導(dǎo)致任何位置1,那么將執(zhí)行true分支。如果邏輯AND的結(jié)果為零,則將執(zhí)行false分支,

| 最佳實(shí)踐指南6-1 |

|---|

| 對(duì)于if-else條件表達(dá)式,盡量只使用1位值或返回true/false操作。不要將向量用作if-else表達(dá)式。 |

之前的文章也詳細(xì)介紹了返回true/false結(jié)果的運(yùn)算符。

不要對(duì)向量進(jìn)行true/false測(cè)試。評(píng)估向量為true/false可能會(huì)導(dǎo)致設(shè)計(jì)錯(cuò)誤。在前面的示例中,編寫(xiě)代碼的工程師打算測(cè)試(a & b)的true/false,但是它是8位向量值,它并不是true/false邏輯運(yùn)算的1位結(jié)果。對(duì)于a和b的某些值,if-else決策執(zhí)行的哪個(gè)分支可能不同,通過(guò)遵循僅使用標(biāo)量(1位)值或返回具有true/false結(jié)果的操作的指南,可以避免這種模糊性和可能的編碼錯(cuò)誤。

對(duì)于4狀態(tài)值,表達(dá)式可能既不是真的也不是假的,如值8’b0000000z。一個(gè)既不正確也不錯(cuò)誤的表達(dá)被認(rèn)為是未知的。當(dāng)if-else決策的表達(dá)式計(jì)算為未知時(shí),將執(zhí)行false分支。這可能會(huì)導(dǎo)致RTL模型的仿真方式以及綜合后門(mén)級(jí)模型的實(shí)際行為不匹配。后面我們會(huì)討論關(guān)于SystemVerilog模型中的X-optimism 和 X-pessimism對(duì)這種情況進(jìn)行了討論。

if-else決策的每個(gè)分支可以是一條語(yǔ)句,也可以是一組包含在begin和end之間的語(yǔ)句,如下面的代碼段所示,

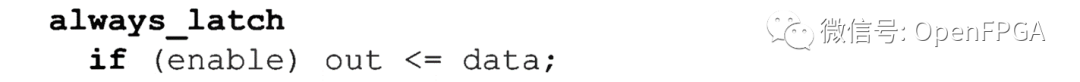

沒(méi)有else分支的if語(yǔ)句。if-else決策的else(false)分支是可選的。如果沒(méi)有else分支,且表達(dá)式的計(jì)算結(jié)果為false(或unknown),則不執(zhí)行任何語(yǔ)句。在下面的代碼段中,如果enable為0,則out不會(huì)更改。由于out是一個(gè)變量,它保留了以前的值,仿真時(shí)會(huì)產(chǎn)生鎖存器行為。

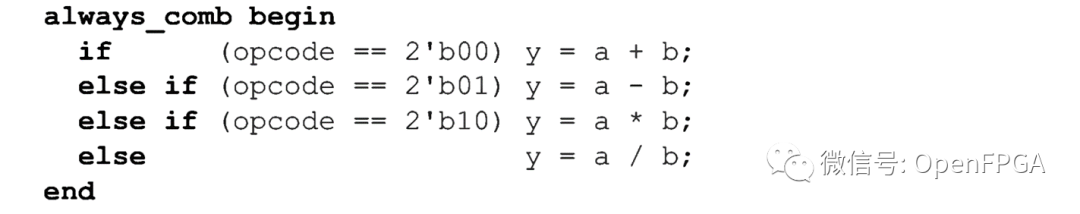

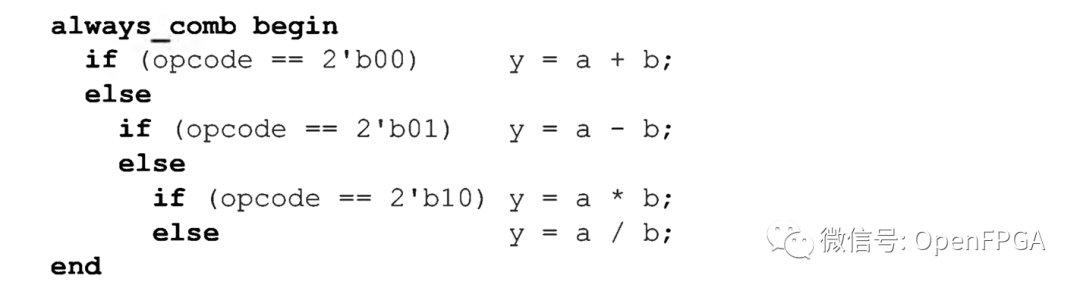

If-else-if。多個(gè)判斷語(yǔ)句可以由一系列if-else語(yǔ)句組成,如下面的代碼片段所示。

請(qǐng)注意,SystemVerilog不像某些編程語(yǔ)言那樣具有elsif關(guān)鍵字。決策鏈由包含嵌套if-else語(yǔ)句的每個(gè)else分支組成。當(dāng)上面的代碼段使用不同的縮進(jìn)編碼時(shí),這種嵌套更為明顯,如下所示。

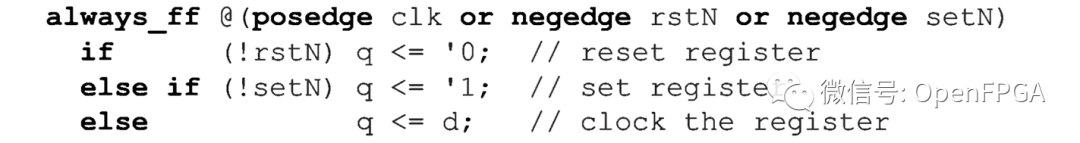

一系列if-else-if決策按照語(yǔ)句的列出時(shí)序進(jìn)行評(píng)估。這將優(yōu)先考慮首先列出的判斷條件。下面的示例演示了一個(gè)可以set和reset的觸發(fā)器。如果set和reset同時(shí)激活,reset具有優(yōu)先級(jí),因?yàn)樗窃谝幌盗袥Q策中首先進(jìn)行判斷的。本例中的set和reset為低電平有效信號(hào)。

(該set和reset觸發(fā)器示例存在潛在的仿真故障,后面我們?cè)賹?duì)此進(jìn)行討論。)

綜合if-else語(yǔ)句。綜合編譯器實(shí)現(xiàn)if-else語(yǔ)句的方式取決于決策語(yǔ)句的上下文以及目標(biāo)ASIC或FPGA中可用的組件類(lèi)型。一般規(guī)則是:

組合邏輯中的if-else語(yǔ)句表現(xiàn)為多路復(fù)用器,通常在門(mén)級(jí)實(shí)現(xiàn)中實(shí)現(xiàn)為多路復(fù)用器。

如果沒(méi)有其他語(yǔ)句分配給同一個(gè)變量,則組合邏輯中沒(méi)有else的if將充當(dāng)鎖存器,這是因?yàn)榉峙涞淖兞勘A羝湎惹暗闹怠>C合器通常將這種存儲(chǔ)效果作為鎖存器來(lái)實(shí)現(xiàn),

組合邏輯中的if-else-if語(yǔ)句系列使用優(yōu)先級(jí)編碼行為進(jìn)行仿真,其中每個(gè)if語(yǔ)句優(yōu)先于該系列中的任何后續(xù)if語(yǔ)句。如果所有決策表達(dá)式都是互斥的(兩個(gè)或多個(gè)表達(dá)式不可能同時(shí)為真),則綜合編譯器將刪除優(yōu)先級(jí)編碼。

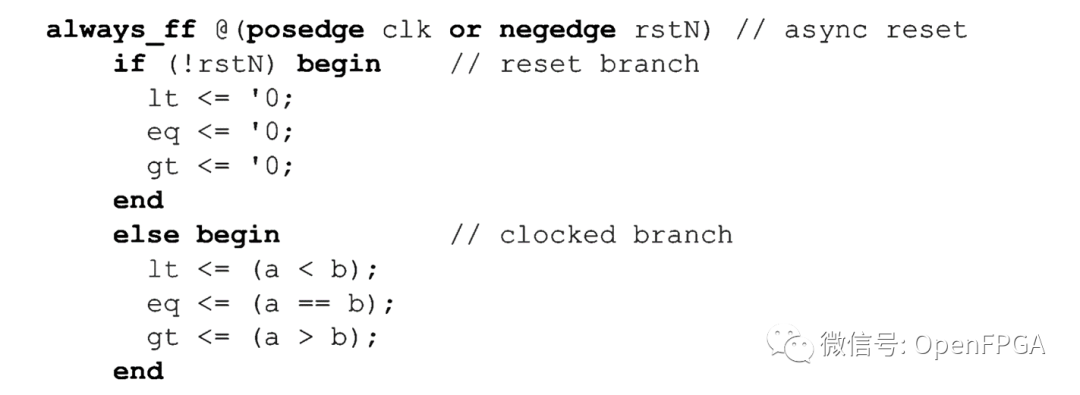

在時(shí)鐘邊沿評(píng)估的if-else語(yǔ)句表現(xiàn)為觸發(fā)器,并將在門(mén)級(jí)實(shí)現(xiàn)中綜合為某種類(lèi)型的寄存器。

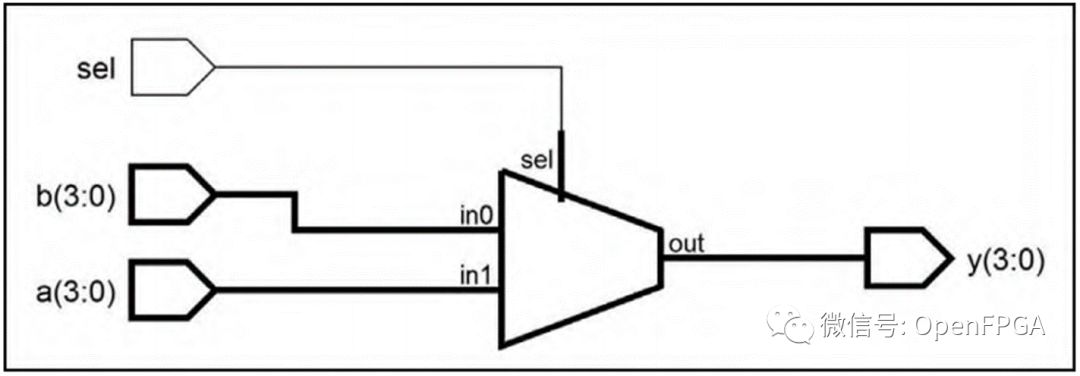

使用if-else作為多路復(fù)用器。圖6-1中的示例6-1及其附帶的綜合結(jié)果顯示了,綜合器會(huì)在多路復(fù)用器的上下文中判斷是否使用了else。

示例6-1:使用if-else對(duì)多路復(fù)用器功能進(jìn)行建模

`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulemux2to1 #(parameterN=4)//bussize (inputlogicsel,//1-bitinput inputlogic[N-1:0]a,b,//scalableinputsize outputlogic[N-1:0]y//scalableoutputsize ); timeunit1ns;timeprecision1ns; always_combbegin if(sel)y=a; elsey=b; end endmodule:mux2to1 `end_keywords

圖6-1:示例6-1的綜合結(jié)果:作為MUX的if-else

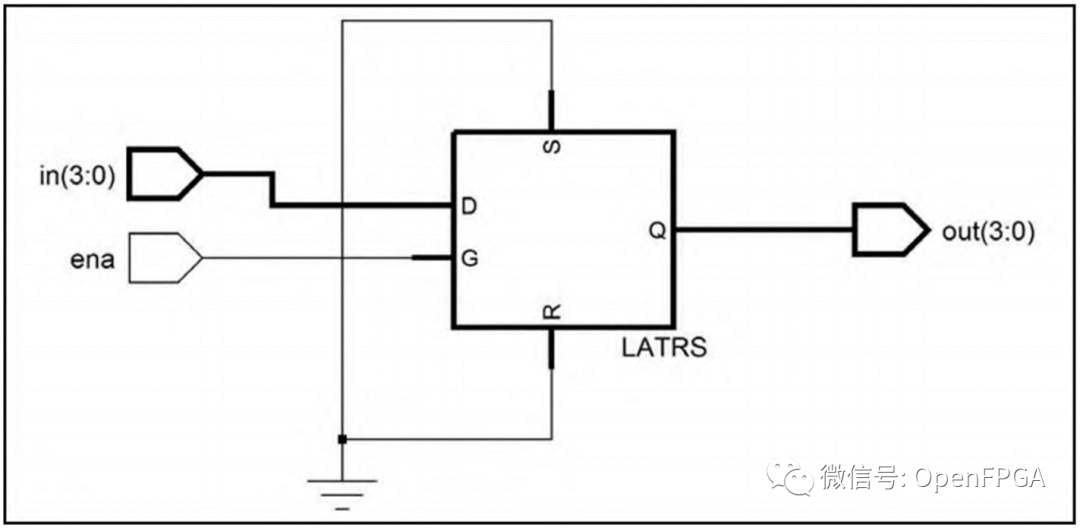

使用if-else作為鎖存器。示例6-2顯示了表示鎖存器的if語(yǔ)句。

示例6-2:使用if不適用else來(lái)仿真鎖存器功能

`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulelatch #(parameterN=4)//bussize (inputlogicena,//1-bitinput inputlogic[N-1:0]in,//scalableinputsize outputlogic[N-1:0]out//scalableoutputsize ); timeunit1ns;timeprecision1ns; always_latchbegin if(ena)out<=?in;? ??end endmodule:?latch `end_keywords圖6-2:示例6-2的綜合結(jié)果:if-else作為鎖存器

用于生成圖6-2的綜合編譯器將RTL功能轉(zhuǎn)換為具有未使用的set和reset輸入的通用鎖存器。最終實(shí)現(xiàn)中使用的鎖存器的具體類(lèi)型將取決于目標(biāo)ASIC或FPGA中可用的鎖存器類(lèi)型。

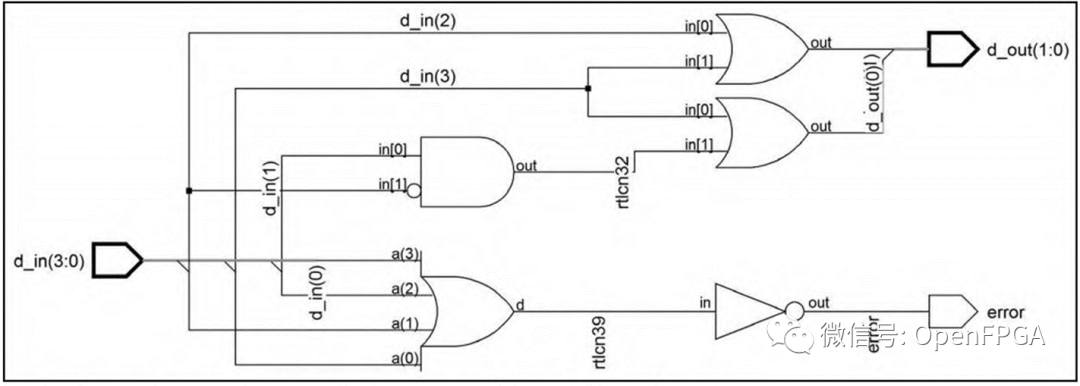

使用if-else作為優(yōu)先級(jí)編碼器。示例6-3說(shuō)明了4對(duì)2優(yōu)先級(jí)編碼器中的if-else-if。

示例6-3:使用if else if系列對(duì)優(yōu)先級(jí)編碼器建模

`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulepriority_4to2_encoder( inputlogic[3:0]d_in, outputlogic[1:0]d_out, outputlogicerror ); timeunit1ns;timeprecision1ns; always_combbegin error='0; if(d_in[3])d_out=2'h3;//bit3isset elseif(d_in[2])d_out=2'h2;//bit2isset elseif(d_in[1])d_out=2'h1;//bit1isset elseif(d_in[0])d_out=2'h0;//bit0isset elsebegin//nobitsset d_out=2'b0; error='1; end end endmodule:priority_4to2_encoder `end_keywords

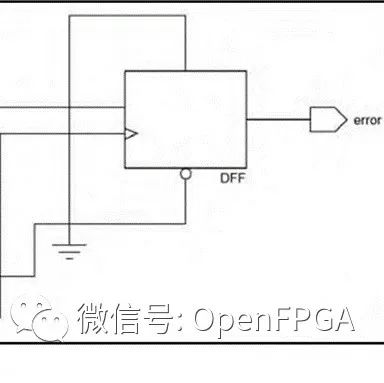

圖6-3;示例6-3的綜合結(jié)果:if-else作為優(yōu)先編碼器

圖6-3中的“優(yōu)先級(jí)編碼”被綜合為一系列邏輯門(mén),其中一級(jí)的輸出成為“序列中下一級(jí)”的輸入,而不是并行編碼d_in的所有位。“該串行數(shù)據(jù)路徑”是“if-else-if”系列中計(jì)算d_in數(shù)據(jù)位的優(yōu)先級(jí)的結(jié)果。

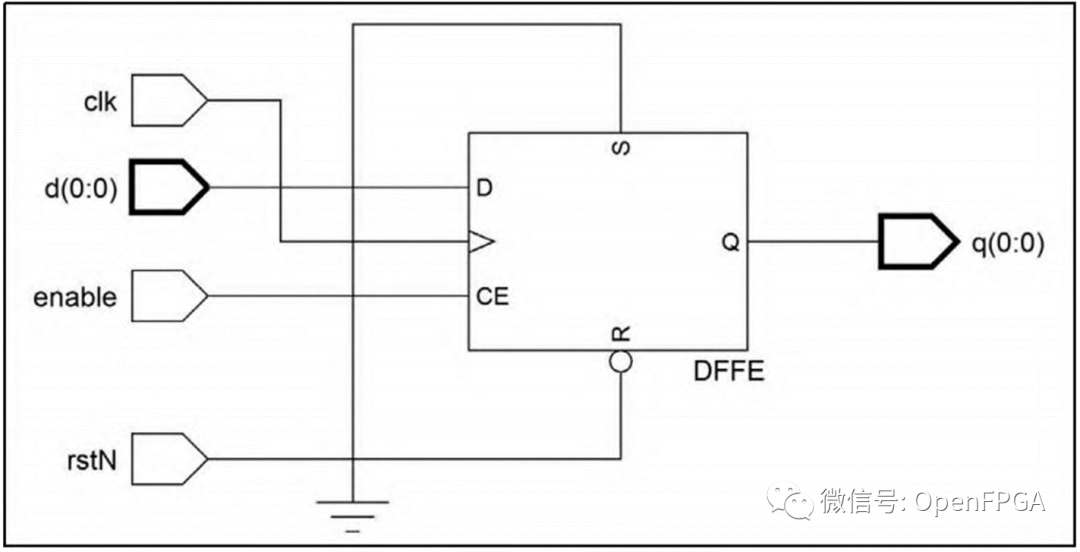

使用if-else作為觸發(fā)器。示例6-4顯示了帶有復(fù)位和芯片使能(也稱(chēng)為負(fù)載使能或數(shù)據(jù)使能)輸入的時(shí)序邏輯觸發(fā)器中的if-else-if。因?yàn)閺?fù)位輸入是首先評(píng)估的,所以它的優(yōu)先級(jí)高于使能輸入,圖6-4顯示了綜合這個(gè)if-else-if決策序列的結(jié)果。

例6-4;使用if-else-if系列為帶復(fù)位和芯片使能的觸發(fā)器建模

moduleenable_ff #(parameterN=1)//bussize (inputlogicclk,//posedgetriggeredclk inputlogicrstN,//activelowasyncreset inputlogicenable,//activehighchipenable inputlogic[N-1:0]d,//scalableinputsize outputlogic[N-1:0]q//scalableoutputsize ); timeunit1ns;timeprecision1ns; always_ff@(posedgeclkornegedgerstN)//asyncreset if(!rstN)q<=?'0;??????????????//?active-low?reset ???else?if?(enable)?q?<=?d;???????????????//?store?if?enabled endmodule:?enable_ff

圖6-4:示例6-4的綜合結(jié)果:if-else作為芯片啟用觸發(fā)器

圖6-4顯示了綜合如何將帶低電平復(fù)位和使能的芯片觸發(fā)器映射到通用組件。該過(guò)程的下一步是綜合編譯器將該通用組件映射到目標(biāo)ASIC或FPGA設(shè)備中可用的特定類(lèi)型的觸發(fā)器,如果該目標(biāo)設(shè)備沒(méi)有芯片使能觸發(fā)器,則綜合將在觸發(fā)器之外添加多路復(fù)用器功能,以模擬芯片使能行為,如果觸發(fā)器使能,多路復(fù)用器將把新的數(shù)據(jù)值傳遞給D輸入,并將觸發(fā)器Q輸出反饋給D輸入。

如果觸發(fā)器未使能,則輸入。以類(lèi)似的方式,如果目標(biāo)設(shè)備沒(méi)有具有異步低電平有效的復(fù)位的觸發(fā)器,則綜合編譯器將在觸發(fā)器之外添加功能,以模擬這種行為,后面再討論具有各種復(fù)位類(lèi)型的建模和綜合觸發(fā)器。

SystemVerilog-程序塊 (procedural blocks)

SystemVerilog-歸約運(yùn)算符(Reduction operators)

審核編輯:劉清

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110243 -

鎖存器

+關(guān)注

關(guān)注

8文章

907瀏覽量

41590 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59903 -

多路復(fù)用器

+關(guān)注

關(guān)注

9文章

873瀏覽量

65324

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

C語(yǔ)言中if語(yǔ)句、if-else語(yǔ)句和switch語(yǔ)句詳解

Proteus之if-else語(yǔ)句的應(yīng)用

python判斷語(yǔ)句的詳細(xì)說(shuō)明

帶初始化的if和switch語(yǔ)句詳解

RTL表達(dá)式和運(yùn)算符

決策語(yǔ)句允許程序塊的執(zhí)行流程

continue和break跳轉(zhuǎn)語(yǔ)句介紹

什么是SystemVerilog-決策語(yǔ)句-if-else語(yǔ)句?

C語(yǔ)言if語(yǔ)句最常見(jiàn)的幾種形式

詳解Python條件語(yǔ)句

在Python中的if...else條件語(yǔ)句介紹

Verilog中的If語(yǔ)句和case語(yǔ)句介紹

systemverilog的決策語(yǔ)句if…else語(yǔ)句介紹

systemverilog的決策語(yǔ)句if…else語(yǔ)句介紹

評(píng)論