內(nèi)容簡介

北京航空航天大學(xué)趙巍勝教授和曹凱華助理教授課題組與致真存儲(北京)科技有限公司研發(fā)團隊合作在自旋軌道矩MRAM器件方面取得重要進展,相關(guān)研究結(jié)果以“利用200 mm晶圓工藝平臺集成制備的高性能自旋軌道矩MRAM器件”(Integration of high-performance spin-orbit torque MRAM devices by 200-mm-wafer manufacturing platform)為題,將作為封面文章在Journal of Semiconductors (《半導(dǎo)體學(xué)報》) 2022年第10期發(fā)表。

磁性隨機存取存儲器(MRAM)作為一種新興的非易失性存儲器,具有高讀寫速度、高續(xù)航能力、長存儲時間和低功耗等特點。近年來TSMC、SAMSUNG、GlobalFoundries等大型半導(dǎo)體廠商也在MRAM領(lǐng)域積極布局。一方面?zhèn)鹘y(tǒng)的嵌入式閃存(e-flash)是基于先擦除后寫入的方式,每個擦寫單元的擦除次數(shù)有限,會因為擦除次數(shù)過多而被磨損,進而影響整個e-flash的生命周期,同時e-flash在28 nm CMOS技術(shù)節(jié)點以下成本過高。相比之下MRAM具有可實現(xiàn)近乎無限次寫入的優(yōu)勢,成本較低,因此,MRAM成為替代e-flash的重要解決方案。

另一方面,MRAM也可替代SRAM以解決先進CMOS節(jié)點的潛在漏電問題。然而,目前比較成熟的Toggle-MRAM和自旋轉(zhuǎn)移矩MRAM(STT-MRAM),由于寫入速度限制和可靠性問題,很難取代L1或L2緩存。為了解決以上問題,研究人員提出了在三端器件中讀寫路徑分離的自旋軌道矩MRAM(SOT-MRAM),從本質(zhì)上解決了高寫入電流導(dǎo)致的讀錯誤和隧道結(jié)老化問題。

目前SOT-MRAM在業(yè)界仍處于研發(fā)階段,并且在晶圓級制造中仍面臨著一些挑戰(zhàn)。這些挑戰(zhàn)主要來自于以下兩個方面:(1)SOT-MRAM器件結(jié)構(gòu)采用頂釘扎的結(jié)構(gòu),重金屬(SOT層)與后段工藝(BEOL)介質(zhì)相鄰,襯底的粗糙度嚴重影響上層重金屬層和磁隧道結(jié)(MTJ)膜堆的磁學(xué)性能和電學(xué)性能,這就使得BEOL工藝與SOT-MTJ器件的集成具有較大挑戰(zhàn);(2)由于SOT-MRAM器件的底電極很薄(通常5 nm左右),如何控制MTJ刻蝕精準(zhǔn)停止在底電極層(保證刻蝕工藝對底電極和MTJ的損傷最小)也是一項巨大的挑戰(zhàn),同時刻蝕深度均勻性直接影響晶圓級器件性能均勻性的分布。

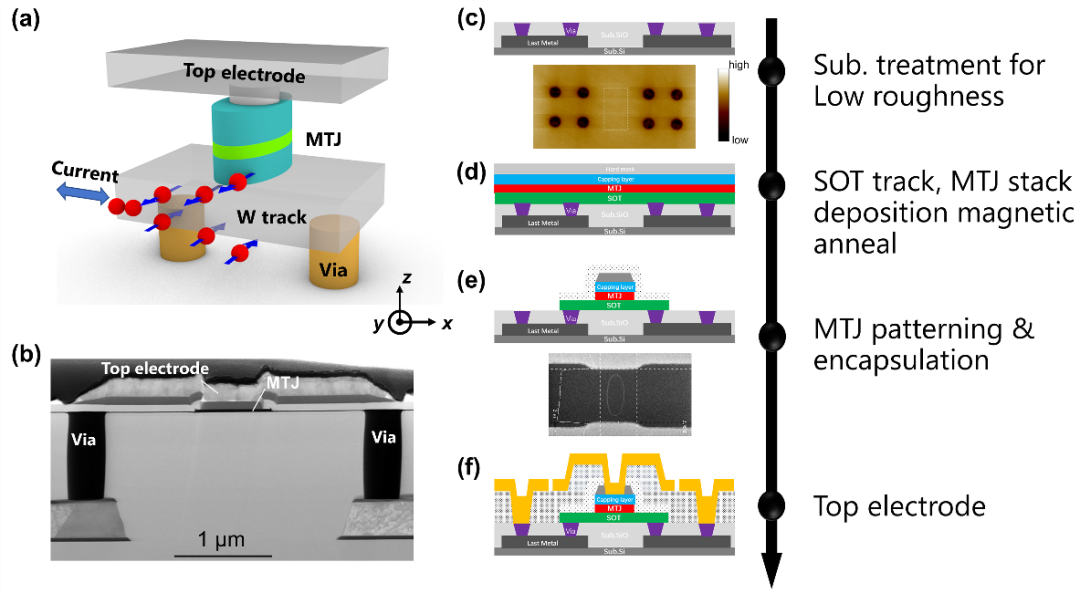

圖1. SOT-MRAM器件結(jié)構(gòu)及工藝流程圖。

針對上述挑戰(zhàn),本工作通過調(diào)整BEOL工藝后襯底的粗糙度,成功實現(xiàn)了BEOL與SOT-MTJ器件的集成,并通過調(diào)整刻蝕工藝參數(shù)使得MTJ刻蝕精準(zhǔn)停止在底電極層,保證了晶圓內(nèi)器件的短路率低于5%,同時刻蝕對MTJ的損傷較小。最終成功制備了8英寸晶圓級可實現(xiàn)無場翻轉(zhuǎn)的高性能SOT-MRAM器件,并對器件的磁學(xué)和電學(xué)性能(單器件和晶圓級)進行了系統(tǒng)的測試。器件各項指標(biāo)與臺積電2022年7月在VLSI會議上報道的8 Kb SOT-MRAM器件性能相當(dāng),在國內(nèi)外處于領(lǐng)先地位。

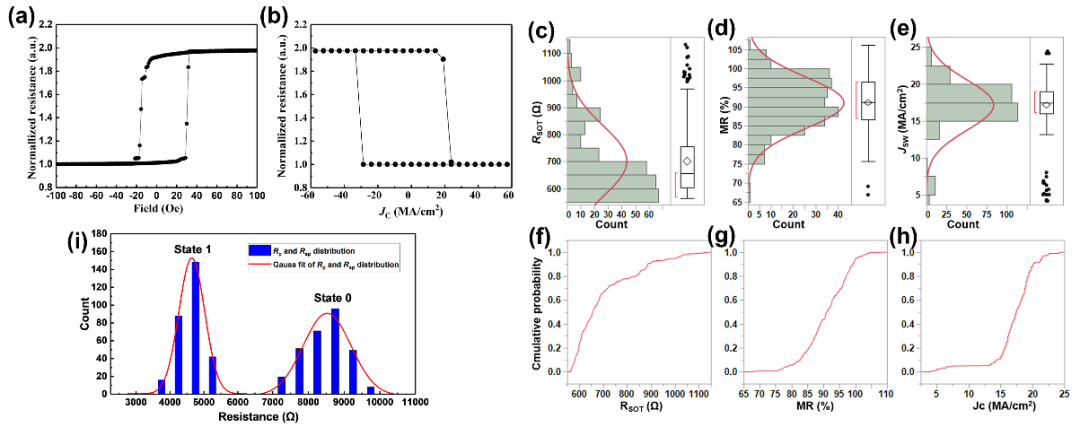

具體的,本工作首先測試了單器件的磁學(xué)和電學(xué)性能,在R-H和R-V測試中,器件TMR達到100%;晶圓級器件性能的均勻性RSOT sigma ~ 18%,TMR sigma ~ 7%,JSW sigma ~ 20%;器件短路率小于5%,Rap和Rp阻值間距~ 5 Rp sigma,滿足存儲器對器件的讀寫要求。在改變MTJ長軸大小時,發(fā)現(xiàn)器件翻轉(zhuǎn)電流隨長軸增大而逐漸增大,利用分流模型成功解釋了器件翻轉(zhuǎn)電流和MTJ尺寸的依賴關(guān)系。

同時測試了器件翻轉(zhuǎn)電流與電流脈寬之間的依賴關(guān)系,得到器件的原始翻轉(zhuǎn)電流JC0 ~±38 MA/cm2;在器件的耐久性測試中,寫入1010次電流后,測試器件底電極電阻、P態(tài)電阻和AP態(tài)電阻變化小于1%,具有良好的耐久性;利用磁場測得器件的熱穩(wěn)定因子Δ ~ 100,退火方法測試器件在工作溫度85 ℃下的熱穩(wěn)定因子Δ ~ 55,以上結(jié)果均表明流片的器件滿足十年期的存儲要求。

圖2. SOT-MRAM器件的電學(xué)和磁學(xué)性能測試;晶圓級RSOT、MR、JSW分布圖和相應(yīng)的CDF曲線;P態(tài)和AP態(tài)阻值的分布圖。

SOT-MRAM器件在200 mm晶圓工藝平臺的成功集成,為SOT-MRAM的產(chǎn)業(yè)化提供了一條可行的途徑。致真存儲研發(fā)團隊在此工作的基礎(chǔ)上已經(jīng)完成小容量SOT-MRAM的8英寸測試片流片工作,預(yù)期在年底會進行128Kb SOT-MRAM工程片流片。

文章PDF(點擊標(biāo)題即可下載):

Integration of high-performance spin-orbit torque MRAM devices by 200-mm-wafer manufacturing platform

審核編輯:劉清

-

CMOS

+關(guān)注

關(guān)注

58文章

5733瀏覽量

235872 -

存儲器

+關(guān)注

關(guān)注

38文章

7525瀏覽量

164161 -

MRAM

+關(guān)注

關(guān)注

1文章

236瀏覽量

31759

原文標(biāo)題:編輯推薦 | 利用200 mm晶圓工藝平臺集成制備的高性能自旋軌道矩MRAM器件

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

基于Rashba自旋軌道相互作用的非常規(guī)超導(dǎo)態(tài)和鐵磁序

自旋憶阻器:最像大腦的存儲器

自旋極化:開創(chuàng)半導(dǎo)體器件設(shè)計的新路徑

新型高性能阻尼器的特點

LMH7322怎樣去改善輸出波形呢 ?

自旋鎖和互斥鎖的使用場景是什么

技術(shù)巔峰!探秘國內(nèi)高性能模擬芯片的未來發(fā)展

探索存內(nèi)計算—基于 SRAM 的存內(nèi)計算與基于 MRAM 的存算一體的探究

電子元器件的封裝形式有哪幾種?

高性能 Flybuck

介紹一種高性能計算和數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu):InfiniBand(IB)

請問HDI PCB如何精準(zhǔn)契合現(xiàn)代電子產(chǎn)品小型化與高性能的雙重需求呢?

瑞薩電子宣布已開發(fā)具有快速讀寫操作的測試芯片MRAM

什么是HPC高性能計算

怎樣去制作一種高性能自旋軌道矩MRAM器件呢

怎樣去制作一種高性能自旋軌道矩MRAM器件呢

評論