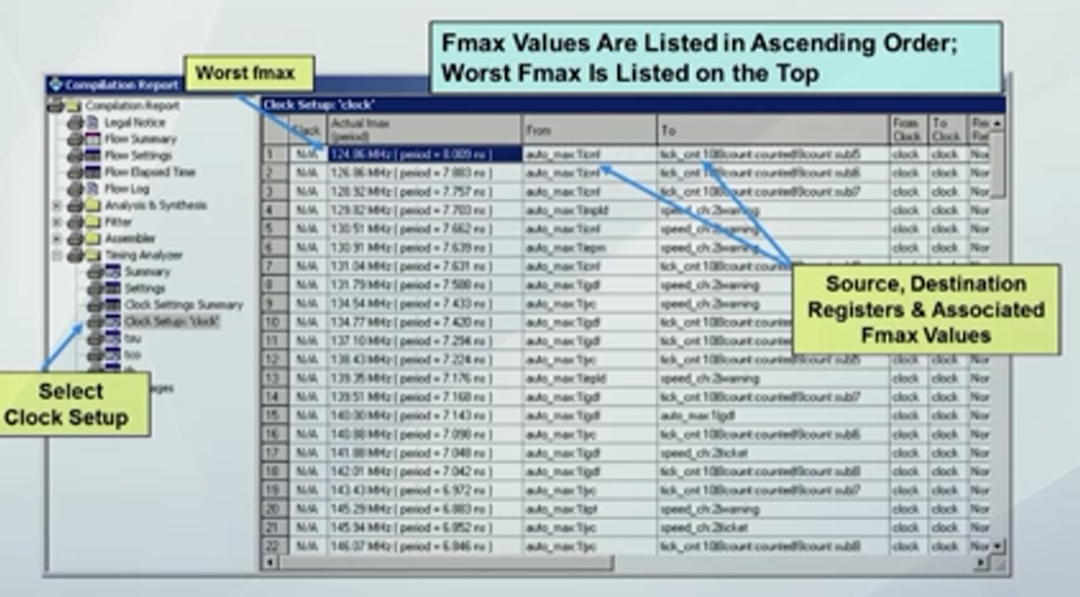

圖一是Quartus Ⅱ工具關(guān)于時序分析建立時間分析報告結(jié)果(個人理解:該報告可以作為時鐘周期報告)。Quartus Ⅱ工具可以詳細給出每一條路徑的分析結(jié)果,路徑信息按照延時由大到小的順序排列,因為延時最長的情況通常被認定為最壞情況,所以需要關(guān)注延時長的情況。

圖一的第一列展示的是延時的時間長度,最長的關(guān)鍵路徑延時為8ns(1ns=10-9s),對該時間取倒數(shù),可以得出芯片的工作頻率在125MHz左右。

除此之外,圖一還展示了延時路徑的一些信息,包括源節(jié)點(可以理解為數(shù)據(jù)發(fā)送端)信息、目標節(jié)點(可以理解為數(shù)據(jù)接收端)信息等。目標節(jié)點從頂層到底層(含個人理解:門級信息,具體到某個節(jié)點的某個引腳)的信息均列出,設計人員可以通過以上信息分析出該路徑在設計中的實際位置,方便對電路設計進行優(yōu)化。

圖一,圖片來源:學堂在線《IC設計與方法》

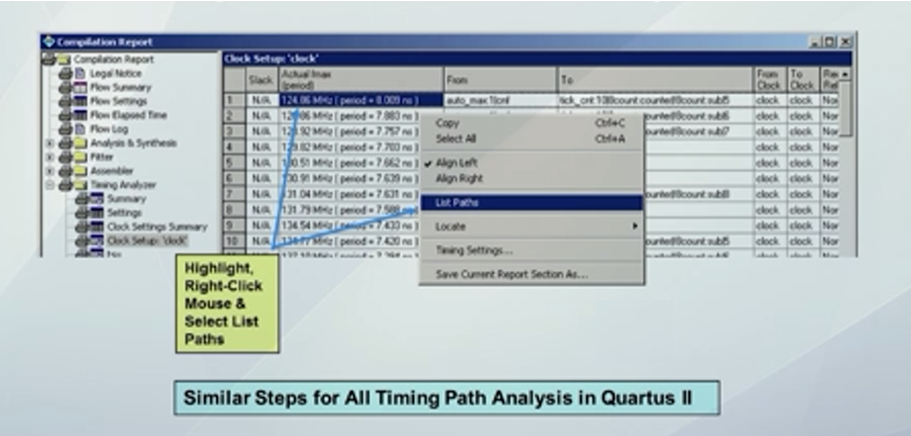

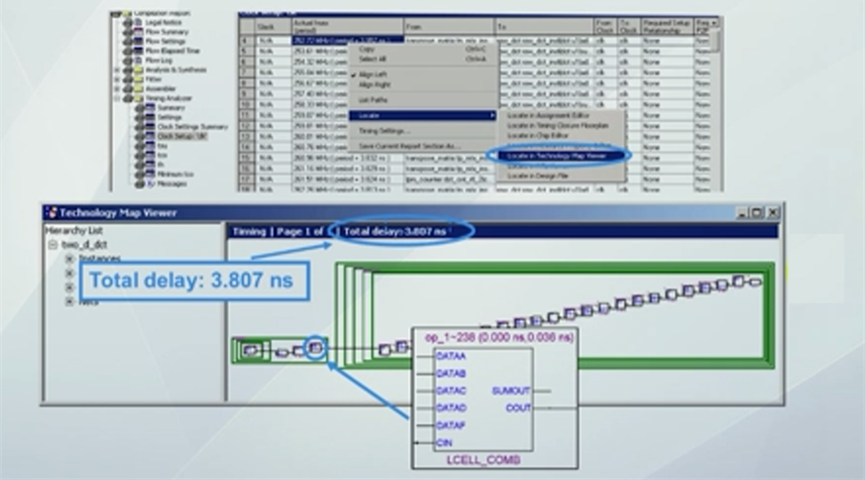

設計人員可以通過圖二的操作列出某一路徑的詳細信息,圖二的操作可以展示延時最長路徑的詳細信息。

圖二,圖片來源:學堂在線《IC設計與方法》

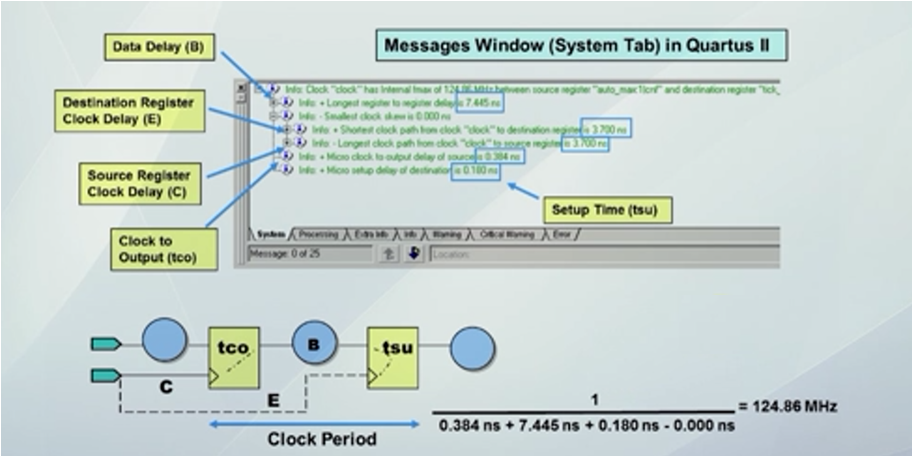

經(jīng)過圖二的操作,Quartus Ⅱ工具會顯示出圖三界面,圖三列出了延時最長路徑的詳細信息。

圖三左下角是時序分析的模型圖,設計人員可以對照模型圖在圖三界面中找到C(時鐘信號傳遞到源觸發(fā)器的延時)、E(時鐘信號傳遞到目標觸發(fā)器的延時)、B(從源觸發(fā)器到目標觸發(fā)器所經(jīng)過的組合邏輯電路的延時)、tco(源觸發(fā)器延時)、tsu的信息(目標觸發(fā)器延時)。

圖三界面中,一共有七行信息。第二行列出了最長的B的延時為7.445ns。第四行列出了最短的E的延時為3.7ns,第五行列出了最長的C的延時為3.7ns,可以發(fā)現(xiàn)C=E,這是因為該芯片面積較小,所以C和E相等。第六行列出了tco為0.384ns,第七行列出tsu為0.18ns。

根據(jù)時鐘周期的公式:

time period=tco+B+tsu-(E-C)

可以計算得出time period(時鐘周期)等于8.009ns。工作頻率為timeperiod的倒數(shù),其值約為124.86MHz。

圖三,圖片來源:學堂在線《IC設計與方法》

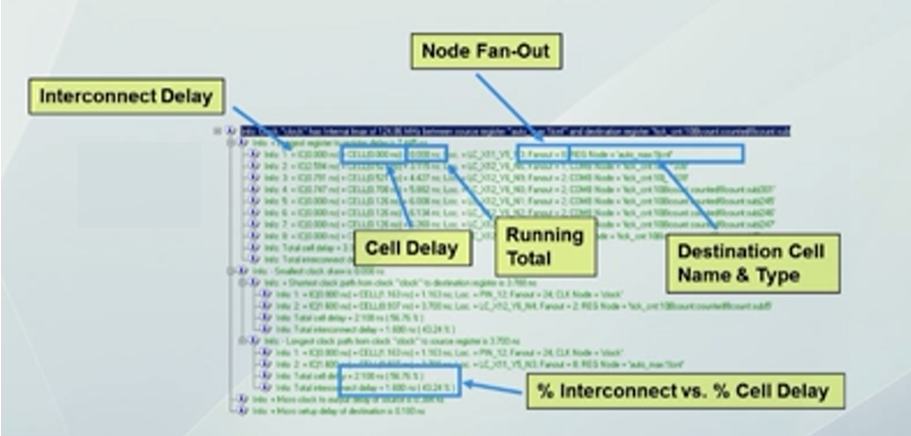

Quartus Ⅱ工具可以將圖三中更詳細的信息展示,如圖四上側(cè),列出B路徑的詳細信息。圖四上側(cè)展示了互連線延時和單元(個人理解:一個門器件)的延時、元器件的扇出系數(shù)(扇出系數(shù)越大,延時越大)、節(jié)點相關(guān)信息。

圖四下側(cè)展示了總結(jié)性的報告,包括總互連線延時、總的單元延時、以及兩種延時所占的比例。設計人員可以通過兩種延時的比例判斷延時過長的原因是因為互連線過長,還是因為邏輯過復雜。

圖四,圖片來源:學堂在線《IC設計與方法》

圖五下側(cè)的窗口展示了使用Technology Viewer(Quartus Ⅱ工具中一種運用圖形展示分析結(jié)果的方式)展示最長延時路徑。如圖五所示,輸入D觸發(fā)器經(jīng)過十幾個單元達到輸出D觸發(fā)器,說明最長延時路徑延時過長的原因是電路邏輯過復雜。

設計人員也可以通過Technology Viewer觀測某個元器件所使用的信號、元器件的類型、元器件的延時。

圖五,圖片來源:學堂在線《IC設計與方法》

審核編輯:劉清

-

IC設計

+關(guān)注

關(guān)注

38文章

1299瀏覽量

104176 -

時鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131667 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2002瀏覽量

61284 -

時序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22586

原文標題:芯片設計相關(guān)介紹(32)——Quarus Ⅱ工具時序分析結(jié)果

文章出處:【微信號:行業(yè)學習與研究,微信公眾號:行業(yè)學習與研究】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

混合信號分析儀的原理和應用場景

車載總線監(jiān)控分析及仿真工具 - VBA

超高速數(shù)據(jù)采集系統(tǒng)的時序設計與信號完整性分析

鎖存器的基本輸出時序

時序邏輯電路故障分析

電源時序器的電壓顯示功能

數(shù)據(jù)分析的工具有哪些

matlab神經(jīng)網(wǎng)絡工具箱結(jié)果分析

FPGA 高級設計:時序分析和收斂

影響氣密性測試結(jié)果的原因分析及解決方案分享

QuarusⅡ工具時序分析結(jié)果

QuarusⅡ工具時序分析結(jié)果

評論