英偉達的 Grace CPU 和 Grace Hopper Superchip 有望在 2023 年初發布。

英偉達在下周的 Hot Chips 34 發布會之前宣布了有關Grace CPU Superchip的新細節,并透露該芯片采用4N工藝制造。英偉達還分享了有關架構、數據結構、性能和效率基準的更多信息。Grace芯片和服務器將在2023年上半年投入市場。

英偉達的Grace CPU是該公司第一款專為數據中心設計的CPU專用Arm芯片,在一塊主板上有兩個芯片,共144個核心,而Grace Hopper超級芯片則將Hopper GPU和Grace CPU結合在同一塊板上。在披露中,英偉達最終正式確認 Grace CPU 使用 TSMC 4N 工藝。臺積電在其5nm節點系列中列出了“N4”4nm工藝,將其描述為5nm節點的增強版。英偉達使用該節點的專用變體,稱為“4N”,專門針對其GPU和CPU進行了優化。

隨著摩爾定律的減弱,這些類型的專用節點變得越來越普遍,隨著每個新節點的出現,晶體管的縮小變得越來越困難,成本也越來越高。為了實現英偉達4N等定制工藝節點,芯片設計公司和代工廠攜手合作,使用設計技術協同優化(DTCO)為其特定產品輸入定制功率、性能和面積(PPA)特性。

英偉達此前曾透露,其 Grace CPU 使用現成的Arm Neoverse內核作為其Grace CPU,但該公司尚未指定使用哪種特定版本。然而,英偉達披露,Grace使用Arm v9內核并支持SVE2,Neoverse N2平臺是Arm第一個支持Arm V7和SVE2等擴展的IP。N2 Perseus 平臺采用 5nm 設計(N4 屬于 TSMC 的 5nm 系列)并支持 PCIe Gen 5.0、DDR5、HBM3、CCIX 2.0 和 CXL 2.0。Perseus 設計針對每功率性能(瓦特)和每面積性能進行了優化。Arm 表示,其下一代核心 Poseidon 要到 2024 年才會上市,考慮到 Grace 2023 年初的發布日期,這些核心不太可能成為候選者。

英偉達Grace Hopper CPU 架構

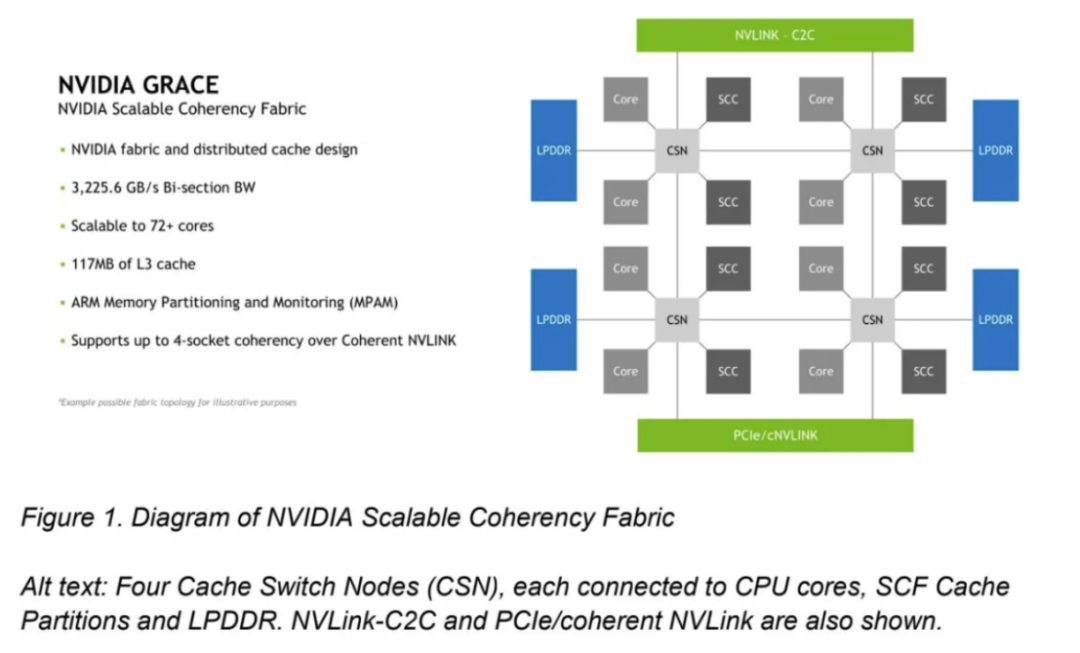

英偉達的新NVDIA calable Coherency Fabric (SCF) 是一種網狀互連,與Arm Neoverse核心使用的標準CMN-700相干網狀網絡非常相似。

英偉達SCF 在各種 Grace 芯片單元(如 CPU 內核、內存和 I/O)之間提供 3.2 TB/s 的雙向帶寬,更不用說將芯片連接到主板上其他單元(無論是另一個Grace CPU還是Hopper GPU)的NVLink-C2C接口。

該網格支持 72+ 個內核,每個 CPU 有 117MB 的總 L3 緩存。英偉達表示,上面圖片中的第一個方框圖是“出于說明目的的可能拓撲結構”,其對齊方式與第二個方框圖不完全一致。

此圖顯示了具有8個SCF緩存分區(SCC)的芯片,這些分區看起來是L3緩存片以及8個CPU單元。SCC 和內核以兩個一組連接到緩存交換節點 (CSN),然后 CSN 駐留在 SCF 網狀結構上,以提供CPU核心和芯片其余部分的存儲器之間的接口。SCF 還通過 Coherent NVLink 支持多達四個插槽的一致性。

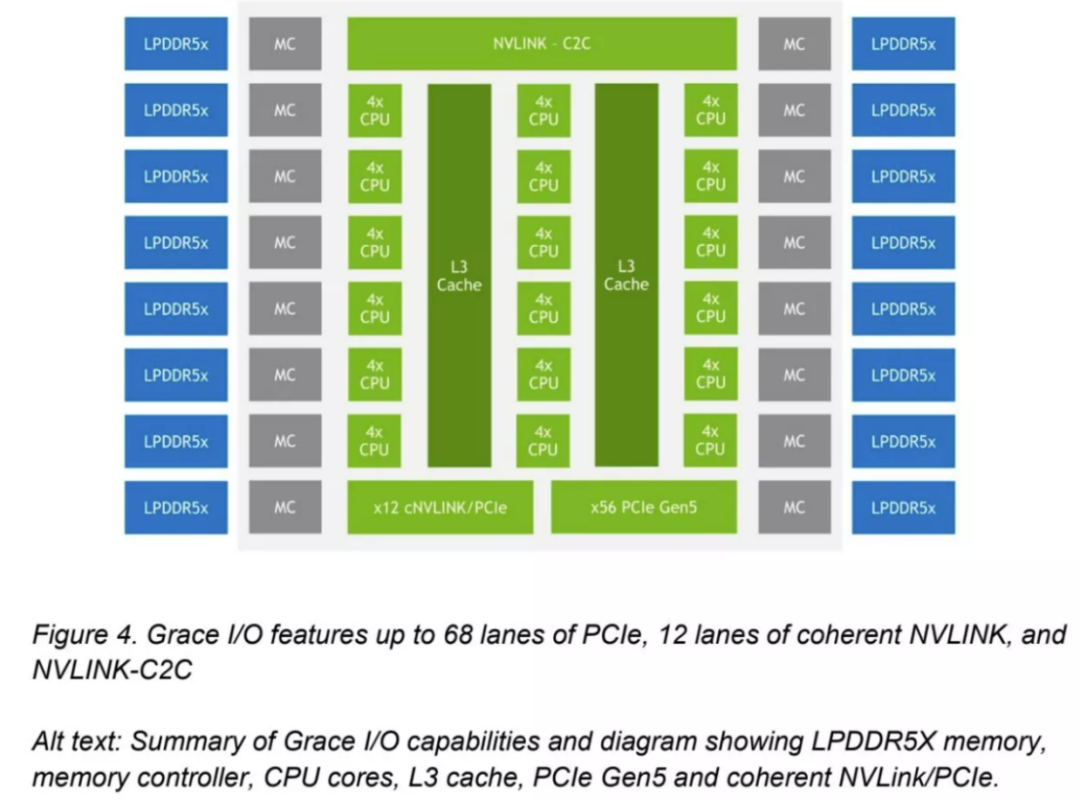

英偉達還分享了上圖,顯示每個Grace CPU支持多達68個PCIe通道和多達4個PCIe 5.0 x16連接。每個x16連接支持高達128 GB/s的雙向吞吐量(x16鏈路可以分成兩個x8鏈路),還有16個雙通道LPDDR5X內存控制器(MC)。然而,這張圖與第一張圖不同——它將 L3 緩存顯示為連接到四核 CPU 集群的兩個連續塊,這比之前的圖更有意義,芯片中總共有 72 個內核。但是,我我們在第一張圖中沒有看到單獨的SCF分區或CSN節點。

英偉達官方表示,Scalable Coherency Fabric (SCF) 是其專有設計,但 Arm 允許其合作伙伴通過調整核心數量、緩存大小和使用不同類型的內存(如 DDR5 和 HBM)來定制 CMN-700 網格,以及選擇各種接口,如 PCIe 5.0、CXL 和 CCIX。這意味著 英偉達有可能為片上結構使用高度定制的 CMN-700 實現。

英偉達Grace Hopper 擴展 GPU 內存

GPU 需要高的內存吞吐量,因此,英偉達將目光轉向提高內存吞吐量,不僅是芯片內部,還包括CPU和GPU之間。Grace CPU 有 16 個雙通道 LPDDR5X 內存控制器,最多可支持 32 個通道,支持高達 512 GB 的內存和高達 546 GB/s 的吞吐量。英偉達表示,由于容量和成本等多種因素,它選擇了 LPDDR5X 而不是 HBM2e。同時,與標準 DDR5 內存相比,LPDDR5X 提供了 53% 的帶寬和 1/8 的每 GB 功耗,使其成為更好的選擇。

英偉達還推出了擴展 GPU 內存 (EGM),它允許 NVLink 網絡上的任何 Hopper GPU 訪問網絡上任何 Grace CPU 的 LPDDR5X 內存。

英偉達的目標是提供一個統一的內存池,可以在 CPU 和 GPU 之間共享,從而在簡化編程模型的同時提供更高的性能。Grace Hopper CPU+GPU 芯片支持具有共享頁表的統一內存,這意味著芯片可以與 CUDA 應用程序共享地址空間和頁表,并允許使用系統分配器來分配 GPU 內存。

英偉達NVLink-C2C

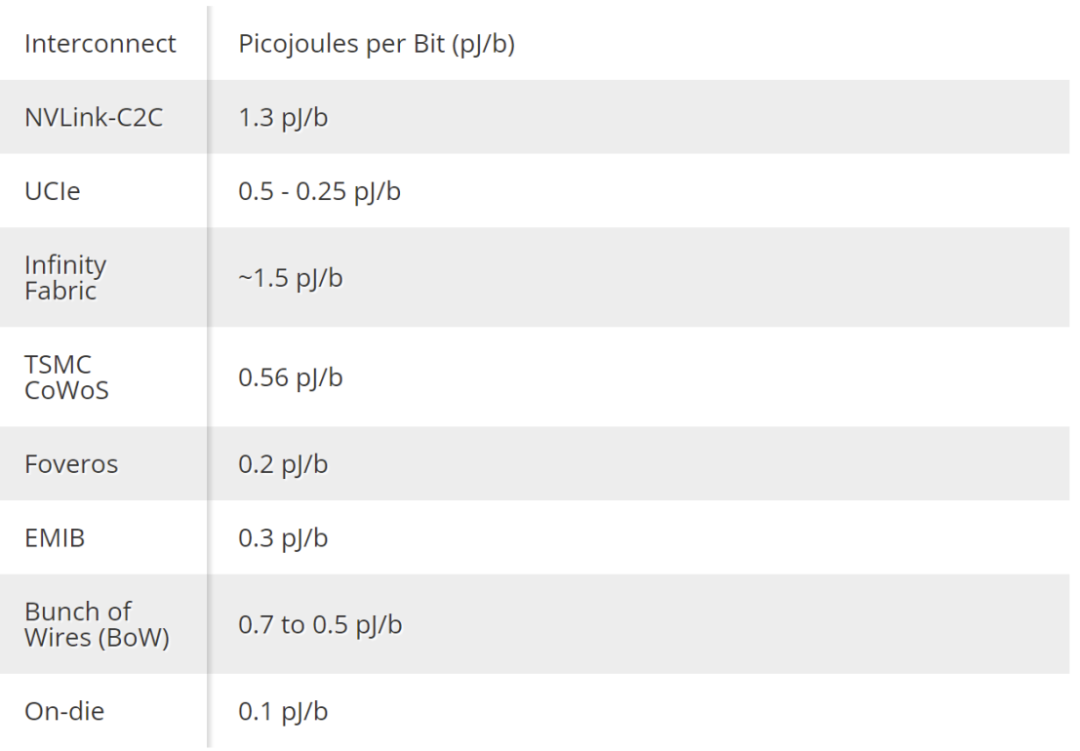

CPU 內核是計算引擎,但互連是決定計算未來的戰場。移動數據比實際計算數據消耗更多的能量,因此更快、更有效地移動數據,甚至避免數據傳輸,是一個關鍵目標。

英偉達的Grace CPU由一塊板上的兩個 CPU 組成,而 Grace Hopper Superchip 則由同一塊板上的一個 Grace CPU 和一個 Hopper GPU 組成,旨在通過專有的NVLink芯片到芯片(C2C)互連最大化單元之間的數據傳輸,并提供一致性內存,以減少或消除數據傳輸。

英偉達分享了有關其 NVLink-C2C 互連的新細節,這是一種支持內存一致性的芯片到芯片和芯片到芯片互連,可提供高達 900 GB/s 的吞吐量(是 PCIe 5.0 x16 鏈路帶寬的 7 倍)。該接口使用 NVLink 協議,英偉達使用其 SERDES 和 LINK 設計技術精心設計了該接口,重點關注能源和面積效率。NVLink-C2C 也支持行業標準協議,如 CXL 和 Arm 的 AMBA 相干集線器接口(CHI — Neoverse CMN-700 網格的CHI-key)。它還支持多種類型的連接,從基于PCB的互連到硅中介層和晶圓級實現。

功率效率是所有數據結構的一個關鍵指標,如今,英偉達共享鏈路傳輸的數據每比特消耗1.3微微焦耳(pJ/b)。這是 PCIe 5.0 接口效率的 5 倍,但它是未來將上市的 UCIe 互連(0.5 到 0.25 pJ/b)功率的兩倍多。封裝類型各不相同,C2C link為 英偉達提供了性能和效率的完美結合,以滿足其特定的使用情況。

英偉達Grace CPU 基準測試

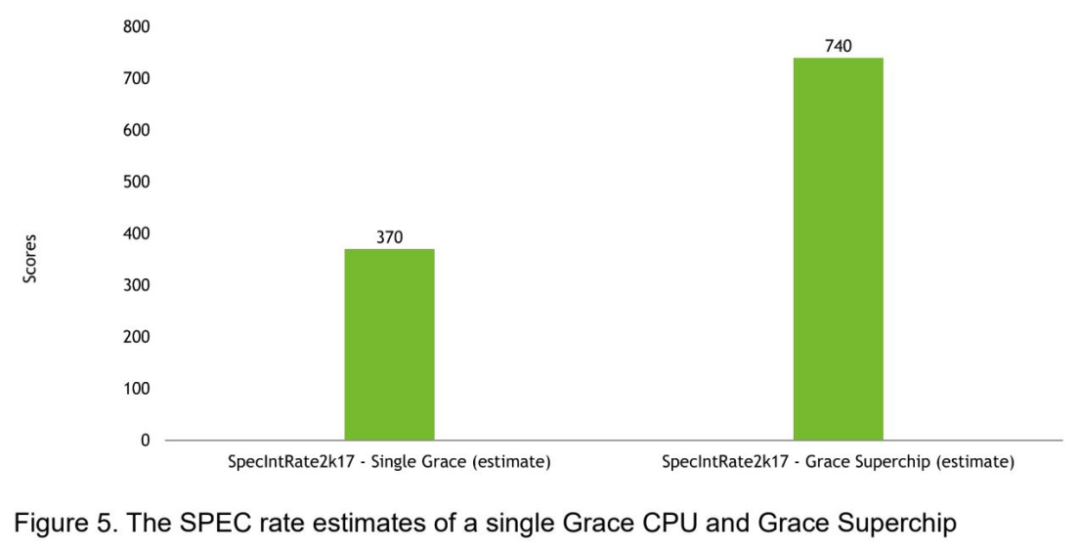

英偉達的新基準是SpecIntRate 2017基準中單臺Grace CPU的370分。這英偉達已經共享了一個多CPU基準,在SPECTINTRATE2017基準中,兩個Grace CPU的得分為740。顯然,這表明兩個芯片的線性縮放改進。

AMD目前的第二代EPYC Milan芯片是數據中心目前的性能領導者,發布的規格結果從382到424片不等,這意味著高端x86芯片仍將保持領先地位。然而,英偉達的解決方案將具有許多其他優勢,如功率效率和更GPU友好的設計。

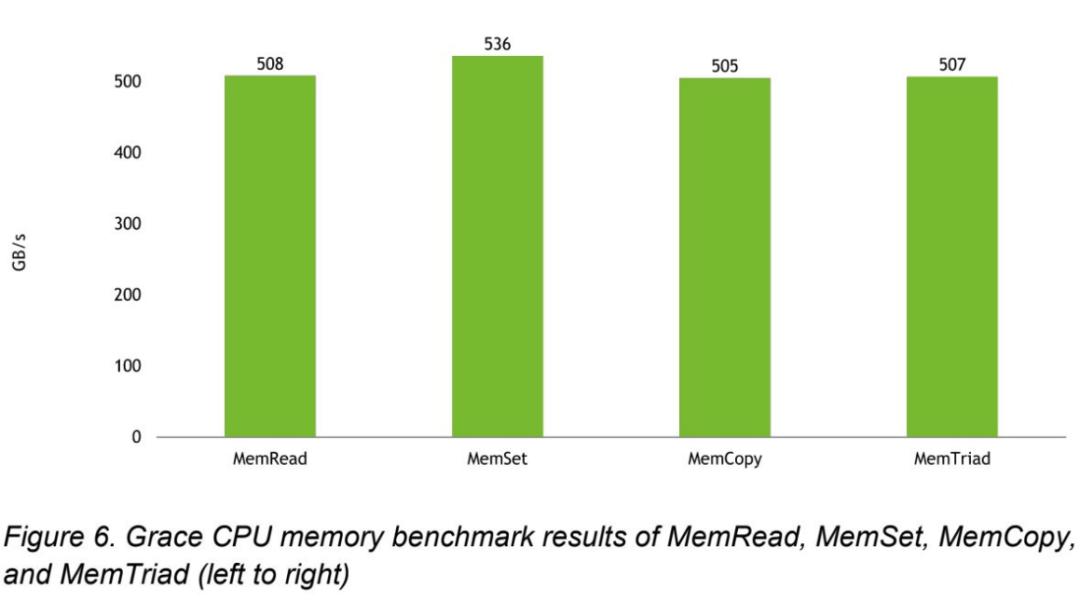

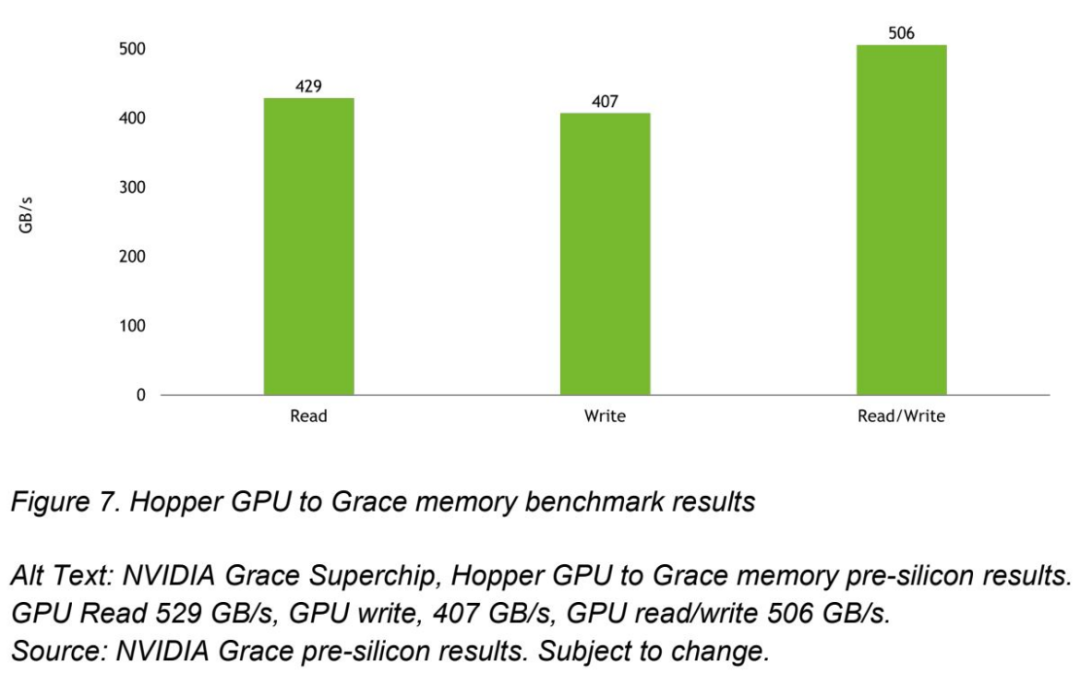

英偉達分享了其內存吞吐量基準,表明Grace CPU在CPU內存吞吐量測試中可以提供約500 GB/s的吞吐量。英偉達還聲稱,該芯片還可以將高達506Gb/s的組合讀/寫吞吐量推送到連接的Hopper GPU,并在讀吞吐量測試期間將CPU到GPU的帶寬計時為429Gb/s,在寫入時為407Gb/秒。

Grace Hopper ARM系統準備好了嗎?

英偉達還宣布 Grace CPU Superchip 將遵守獲得 System Ready 認證的必要要求。以獲得系統就緒認證。該認證意味著Arm芯片將與操作系統和軟件一起“正常工作”,從而簡化部署。Grace 還將支持虛擬化擴展,包括嵌套虛擬化和 S-EL2 支持。英偉達還列出了對以下內容的支持:

nRAS v1.1 通用中斷控制器 (GIC) v4.1

n內存分區和監控 (MPAM)

n系統內存管理單元 (SMMU) v3.1

nArm 服務器基礎系統架構 (SBSA) 可實現符合標準的硬件和軟件接口

此外,為了在基于 Grace CPU 的系統上啟用標準引導流程,Grace CPU被設計為支持Arm服務器基本引導要求(SBBR)。

對于緩存和帶寬分區以及帶寬監控,Grace CPU還支持Arm內存分區和監控(MPAM)。Grace CPU 還包括 Arm 性能監控單元,允許對 CPU 內核以及片上系統 (SoC) 架構中的其他子系統進行性能監控。這使得標準工具(例如 Linux perf)能夠用于性能調查。英偉達的 Grace CPU 和 Grace Hopper Superchip 有望在 2023 年初發布,其中 Hopper 變體適用于 AI 訓練、推理和 HPC,而雙 CPU Grace 系統則專為 HPC 和云計算工作負載而設計。

審核編輯 :李倩

-

cpu

+關注

關注

68文章

10877瀏覽量

212129 -

架構

+關注

關注

1文章

516瀏覽量

25494 -

英偉達

+關注

關注

22文章

3788瀏覽量

91290

原文標題:詳解英偉達Grace Hopper CPU 超級芯片設計

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

英偉達CEO確認:液冷Grace Blackwell服務器無過熱問題

英偉達進軍ARM架構CPU市場,預計2025年推出新產品線

今日看點丨蘋果與富士康接洽,商討在中國臺灣生產AI服務器;英偉達正在開發一款基于ARM架構的新型CPU

英偉達計劃2025年推出基于Arm架構的消費級CPU,挑戰英特爾和AMD

軟銀升級人工智能計算平臺,安裝4000顆英偉達Hopper GPU

英偉達:Hopper芯片需求強勁 英偉達發言人談生產增長

亞馬遜AWS暫緩采購英偉達GH200芯片,期待Blackwell更強

亞馬遜AWS暫緩訂購英偉達Grace Hopper,等待新品Grace Blackwel

亞馬遜未中斷英偉達訂單,等待Grace Blackwell更強性能

英偉達靜候新品來臨,亞馬遜暫緩購買Grace Hopper

進一步解讀英偉達 Blackwell 架構、NVlink及GB200 超級芯片

美國首個Grace Hopper架構超算Venado落地:達10 exaFLOPS

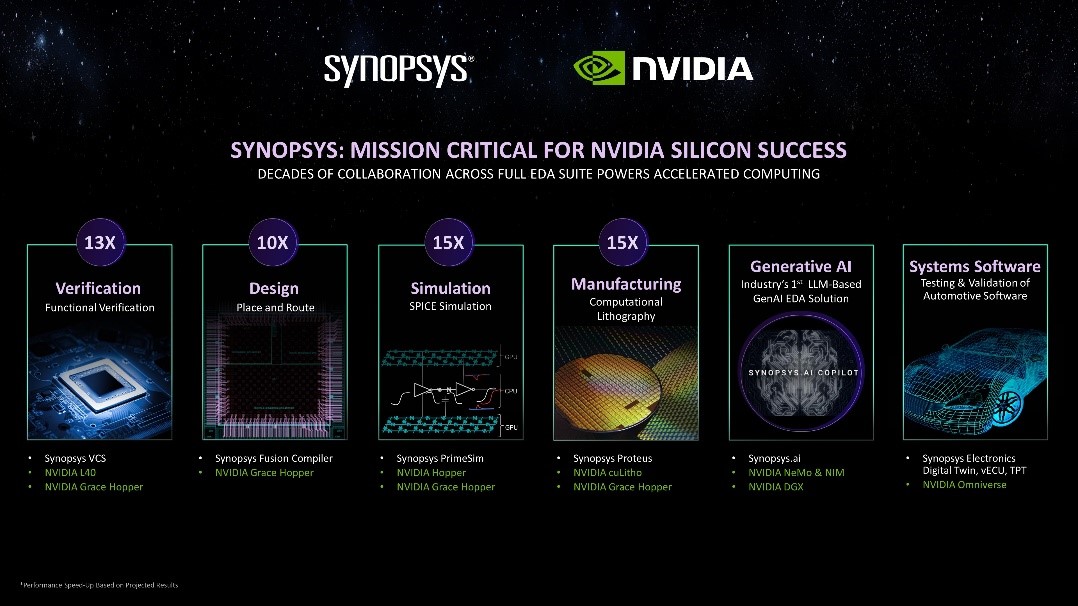

新思科技攜手英偉達:基于加速計算、生成式AI和Omniverse釋放下一代EDA潛能

英偉達Grace Hopper CPU架構

英偉達Grace Hopper CPU架構

評論