工程師通過邏輯綜合過程,將代碼轉化為電路圖,聘請sysnopsys公司的綜合工程師需要每天付費約1500美元。

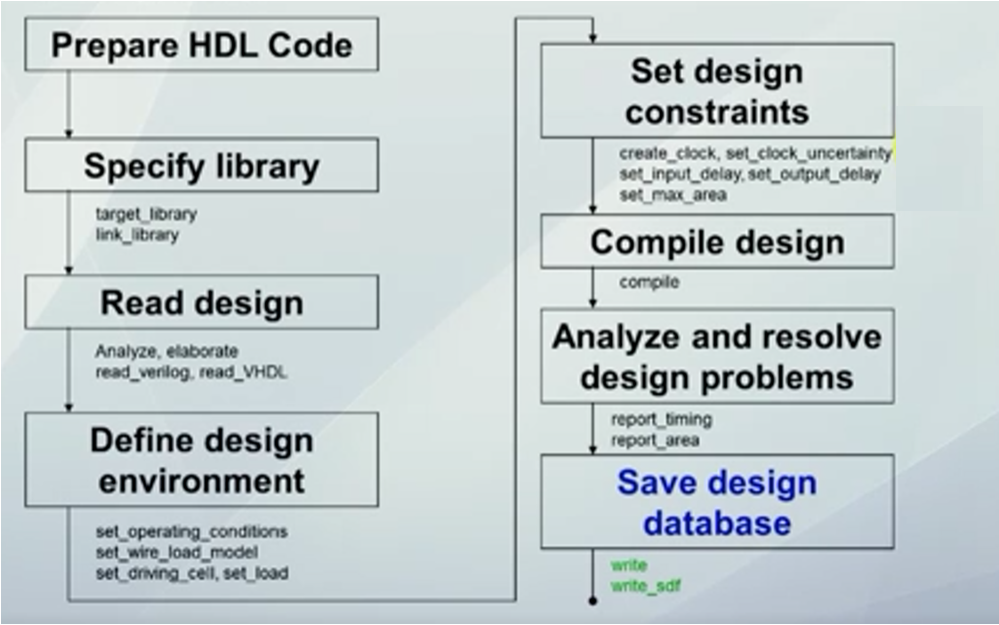

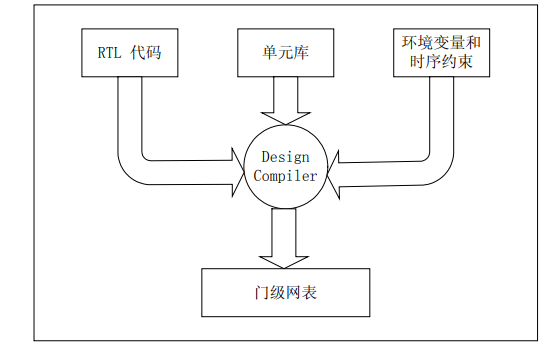

基本邏輯綜合過程如下:

(1)完成代碼編寫(Prepare HDL Code)。

(2)描述庫(Specify library),如標準單元(由其他設計人員完成的功能模塊,可直接在新的芯片設計中使用)的描述。

(3)讀取設計(Read design),讀取設計可以檢測代碼是否可以轉化成電路和轉化電路過程中是否有問題。

(4)定義設計環(huán)境(Define design environment),需定義芯片工作的環(huán)境,芯片外部信號由哪些其他芯片提供,芯片為哪些其他芯片提供信號。

(5)設置約束(Set design constraints),包括對芯片時鐘頻率的描述、輸入接口信號時序的描述、輸出接口時序的描述、對面積的要求、對功耗的要求等。

(6)邏輯綜合操作(Compile design),根據(jù)芯片的復雜程度,邏輯綜合操作的時間可能是幾秒,也可能是半個月。如果設計環(huán)境和約束設置不當,邏輯綜合操作的時間會被延長。

(7)分析結果(Analyze and resolve design problems),邏輯綜合操作結束后,計算機會輸出門級網(wǎng)單(電路)及門級網(wǎng)單的時序、功耗等參數(shù)。如果輸出結果與設計要求偏差在20%以內(nèi),可以通過修改設計環(huán)境(4)和約束(5),做進一步優(yōu)化。如果偏差較大,需要返回過程(1)代碼編寫,重新修改芯片設計代碼。

(8)保存結果(Save design database)當門級網(wǎng)單符合設計要求,可以將結果保存。所設計的門級網(wǎng)單和設計相關的時序信息都需要保存。

圖片來源:學堂在線《IC設計與方法》

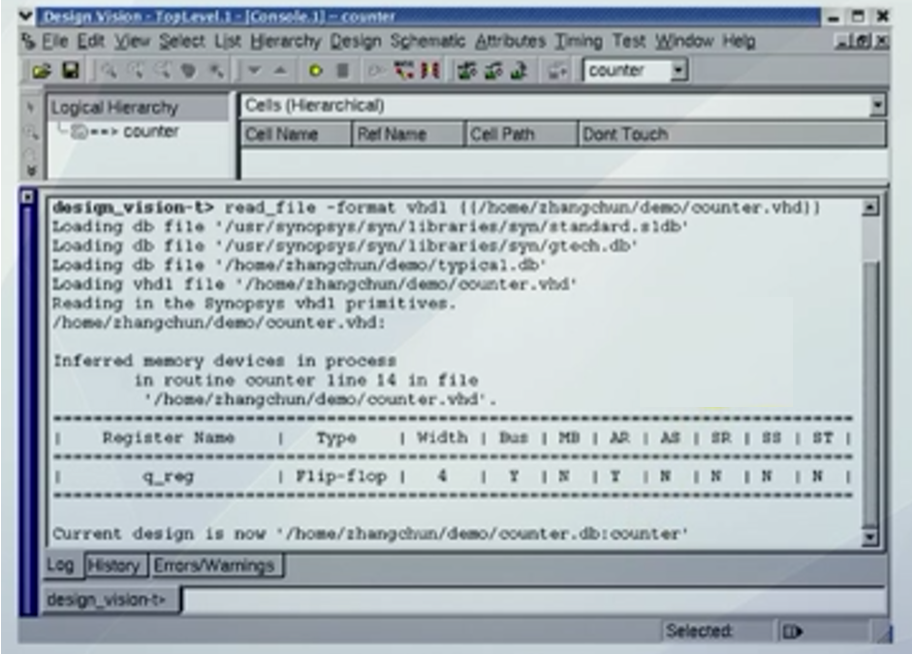

過程(3)讀取設計,工程師需要詳細檢查軟件給出的報告,檢查代碼是否有疏漏。

圖片來源:學堂在線《IC設計與方法》

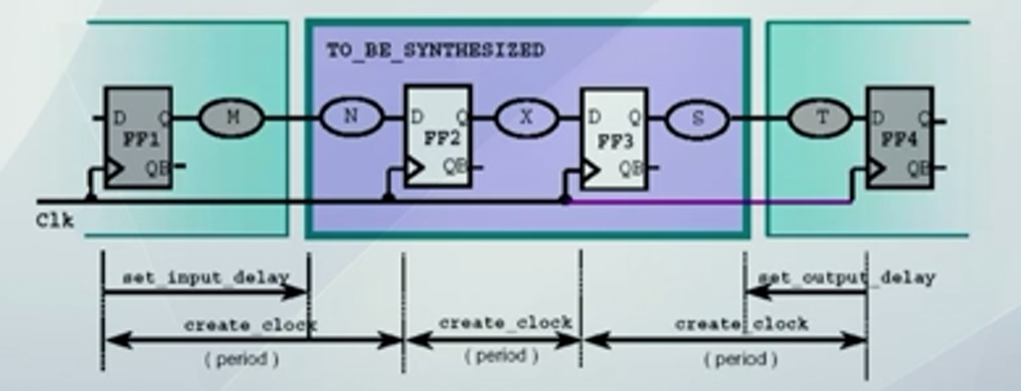

過程(5)設置約束包含時序和面積的約束,通常時序約束的優(yōu)先級更高。

對于下圖X路徑(只涉及內(nèi)特性)的約束,設計人員可以通過約束兩個觸發(fā)器(FF2、FF3)的時鐘周期令軟件計算出X路徑的延時,完成對X的約束。因為軟件可以提取Clock to Q和Set up的時間,根據(jù)時鐘周期>Clockto Q+穿越組合邏輯電路的最長延時+Set up公式,可計算X路徑的延時。

對于下圖N、S路徑(涉及電路外特性),設計人員可以通過約束外部信號輸入和外部電路穩(wěn)定裝載輸出信號的延時分別對N和S(S在紫色的框右側的橢圓中,有些模糊)約束。

圖片來源:學堂在線《IC設計與方法》

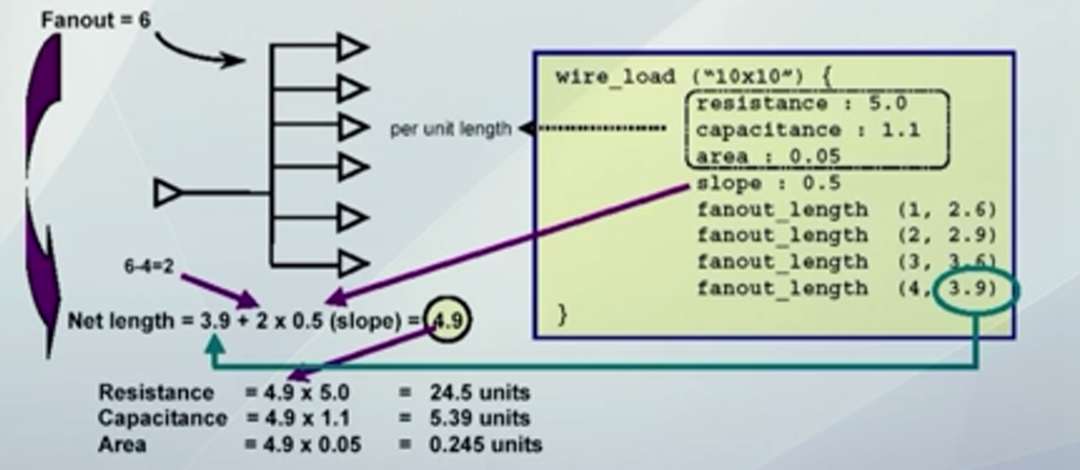

描述時序約束還需關注電路中的連線描述,因為在邏輯綜合階段,連線未確定,因此采用估計的方式得出連線電阻、電容、面積。

假設一個元器件有6個負載(Fanout=6),下圖中黃框內(nèi)fanoutlength表示負載個數(shù)對應的連線長度(Net lenght)。

對于6個負載(超過4個負載)的情況,采用公式:

Net lenght=3.9+2*0.5

上式中“2”表示超過4個負載的數(shù)量,“0.5”從黃框中顯示的slope等效長度得出。

估算出連線長度后,乘以黃框中電阻(resistance)、電容(capacitance)、面積(area)對應的參數(shù),估算出芯片連線的電阻、電容、面積。

圖片來源:學堂在線《IC設計與方法》

審核編輯 :李倩

-

芯片

+關注

關注

456文章

51154瀏覽量

426261 -

邏輯

+關注

關注

2文章

833瀏覽量

29498

原文標題:芯片設計相關介紹(24)——邏輯綜合過程(上)

文章出處:【微信號:行業(yè)學習與研究,微信公眾號:行業(yè)學習與研究】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

ASIC邏輯綜合及Synopsys Design Compiler 的使用資料說明

芯片設計之邏輯綜合過程

芯片設計之邏輯綜合過程

評論