概述

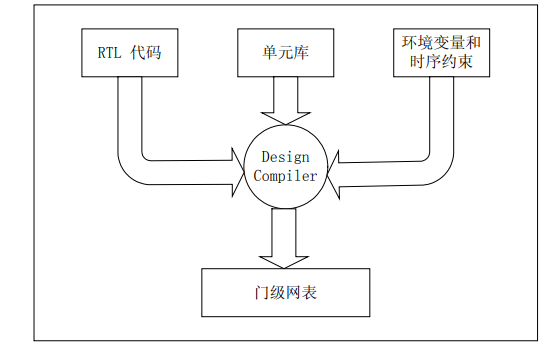

邏輯綜合是將RTL描述的電路轉換成門級描述的電路,將HDL語言描述的電路轉換為性能、面積和時序等因素約束下的門級電路網表。綜合后的門級網表也是.v構成的Verilog代碼,但是里面并沒有我們所寫的always或者assign這種語句,而是將標準單元(Standard Cell)實例化并進行連接。

圖1 RTL網表轉為門級網表

常見的工具是synopsys公司的Design Compiler。

原因

綜合最重要的目的是對電路進行約束,從而在性能、面積和時序之間尋求平衡。

圖2 性能面積和時序的平衡關系

與DFT的關系: DFT插入的測試邏輯也要與Function的邏輯一起綜合,也受上述三個因素的制約,所以Synthesis與DFT關系密切。

流程

邏輯綜合的流程為:翻譯(Translation)、優化(Optimize)、映射(Mapping)。

圖3 綜合流程

1.翻譯: 綜合工具將RTL-level的邏輯電路用門級的邏輯來實現,DC工具用自帶的GTECH庫中的標準單元去搭建門級邏輯電路,最終形成一個初級的、未優化的門級電路。

(GTECH:Generic Technology, 是Synopsys公司提供的獨立于工藝的, 不包含約束的元件庫)

2.映射: 將門級邏輯電路映射到由制造商提供的工藝庫上。(工藝庫包含時序、面積、功耗等約束信息)

3.優化: 綜合工具對門級邏輯電路進行分析,去掉電路中的冗余單元,根據設計者添加的約束條件對電路進行優化。

步驟

(1)準備HDL文件和dc_synthesis.tcl運行腳本

對于DFT工程師,需要準備好插入DFT測試邏輯之后RTL-level的HDL 文件和dc_synthesis.tcl運行腳本

(2)設置路徑和庫文件

設置DC工作路徑和庫文件搜索路徑

define_design_lib work –path work

set search_path /project/dft/library/db

在dc_synthesis.tcl運行腳本中設置target_library(目標庫),和link_lbirary(鏈接庫)

set link_library [list adk.db memory.db pad.db]

set target_library [list adk.db memory.db pad.db]

(3)用analyze/elaborate命令讀入設計

讀入1st insertion和2nd insertion之后的所有RTL文件

*source ../inputs/use_in_synthesis.tcl *

分析HDL文件代碼檢查設計錯誤。

讀入1st insertion和2nd insertion之后的sdc文件

source ../../tsdb_outdir/dft_inserted_designs/{design_name}_{design_id}.dft_inserted_ design/${design_name}.sdc。

elaborate ${design_name} //建立HDL代碼的門級描述

link //將讀到DC中的模塊連接起來

current_design ${design_name} //設置當前設計名稱

check_design //設計規則檢查

(4) 設置約束條件

可以在constrait.tcl約束腳本里將約束條件設置好,再導入到dofile。也可以直接在dofile里設置。

*set preserve_instances [tessent_get_preserve_instances icl_extract]

*

set optimize_instances [tessent_get_optimize_instances icl_extract]

set_boundary_optimization $preserve_instances false

set_ungroup $preserve_instances false

set_boundary_optimization $optimize_instances true

preserve_instances表示不做邊界優化的instances

optimize_instances表示做邊界優化的instances

set_boundary_optimization表示對指定instance做邊界優化

boundary_optimization即邊界優化是一種優化策略, 指是否允許DC跨module的邊界優化, 允許的話, 有些沒用的端口會被去掉, 有些邏輯會被優化掉, 有些信號的名字也會丟失。對于DFT工程師不希望插入的邏輯被優化掉,所以要對插入的邏輯有選擇地進行邊界優化

set_ungroup表示對指定instance做ungroup

ungroup指的是打破設計的層次關系, 把hierarchical設計變成flat設計, 不需要層次關系的端口, 更有利于優化

圖4 ungroup過程

(5) 用compile命令對施加約束的門級網表進行編譯,生成優化的門級網表

(6) 用write/write_sdf/write_sdc/命令將優化后的門級網表以指定的格式保存到指定的路徑

write -f verilog -output ../outputs/${design_name}.synthesis.v

write_file -format ddc -output ../outputs/${design_name}.synthesis.ddc

write_sdc ../outputs/${design_name}.synthesis.sdc

write_sdf ../outputs/${design_name}.synthesis.sdf

圖5 綜合具體流程

約束

DC綜合流程中設置約束的種類有:時序約束、面積約束。時序約束:包括時鐘約束、輸入/輸出接口約束和時序例外約束。時序約束是通過約束各類延遲信息,保證門級電路能夠正常工作。

圖6 約束的分類

1. 時鐘約束: 是對主時鐘進行約束定義,幫助時序分析工具定義時序路徑分析的一個時間零點,時鐘傳輸過程中的延時和不確定性也都會基于這個時間零點進行計算和分析。

主時鐘: 是指由外部輸入模塊內部的時鐘,或是內部模塊產生的時鐘。

約束的命令為:

create_clock -name clk -period 10 -waveform {0 5}

該命令用于定義有特定周期和波形的時鐘

create_clock用于定義一個時鐘

-name用于指定時鐘名

-period用于指定時鐘周期

-waveform用于指定上升沿和下降沿的時刻

圖7 時鐘約束1

圖8 時鐘約束2

set_clock_latency –source 3 [get_clks CLK]

上述命令用于對時鐘源延時進行約束

set_clock_latency 1 [get_clks CLK]

上述命令用于對時鐘網絡延時進行約束

set_clock_uncertainty -setup -hold

上述命令用于對時鐘的偏移和抖動進行約束

可通過*-setup 和 -hold*參數設置建立時間和保持時間的偏移值

set_clock_transition -max 3 [get_clks CLK]

上述命令用于對時鐘的轉換時間進行建模。默認的上轉換時間為從電壓的20%上升至80%的時間,下轉換時間為從電壓的80%下降至20%的時間

可通過*-rise 和 -fall*參數設置上轉換時間和下轉換時間:

set_clock_transition -rise 2 -fall 3 [get_clks CLK]

圖9 時鐘約束3

2. IO約束: 指定input信號和output信號輸入或輸出模塊的延遲時間。

set_input_delay

用于指定輸入數據的路徑延時, 分析從外部輸入到內部寄存器的延遲, 需滿足內部寄存器的建立/保持時間。

set_output_delay

用于指定輸出數據的路徑延時, 分析從內部寄存器到外部輸出的延遲,需滿足外部寄存器的建立/保持時間。

圖10 IO約束

3.時序例外約束: 可以對某些路徑放寬時序要求, 減少對布局布線資源的占用, 從而盡可能多地釋放出寶貴的資源給時序約束要求較高的關鍵路徑,合理分配資源,能夠更好地確保整個系統的時序收斂。

對時序例外進行約束的命令有:

set_multicycle_path

在2個時鐘域之間傳輸數據,指定從起始時鐘沿到目標時鐘沿所需的時鐘周期數。允許數據在多個周期后穩定并接收, 時序要求寬松。

set_false_path

指定在設計中不做分析的時序路徑,即最低優先級的路徑。

圖11 時序例外約束

4.面積約束: 就是告訴DC工具, 綜合完成后的電路面積不能超過多少。

set_max_area 100

指定綜合完成后的最大面積為100(單位與工藝庫的要求一致)。

-

寄存器

+關注

關注

31文章

5357瀏覽量

120659 -

RTL

+關注

關注

1文章

385瀏覽量

59850 -

SDC

+關注

關注

0文章

49瀏覽量

15560 -

DFT算法

+關注

關注

0文章

27瀏覽量

7555 -

HDL語言

+關注

關注

0文章

47瀏覽量

8935

發布評論請先 登錄

相關推薦

[啟芯工作室]邏輯綜合 06 Timing Analysis

FPGA的邏輯仿真以及邏輯綜合的一些原則

DC邏輯綜合

ASIC邏輯綜合及Synopsys Design Compiler 的使用資料說明

什么是邏輯綜合?邏輯綜合的流程有哪些?

什么是邏輯綜合?邏輯綜合的流程有哪些?

評論