封裝行業正準備將chiplet的應用范圍擴大(不再局限于少數芯片供應商),為下一代3D芯片設計和封裝奠定基礎。

新的chiplet標準和成本分析工具(確定一個基于chiplet設計的可行性),與其他努力一起,都在致力于推動chiplet模型向前發展,盡管該技術仍存在一些挑戰和差距。

使用這種方法,封裝廠可以在庫中擁有具有不同功能和過程節點的模塊化chiplet菜單。然后,芯片客戶可以從中選擇,并將它們組裝在一個先進封裝中,從而產生一種新的、復雜的芯片設計,作為SoC的替代品。

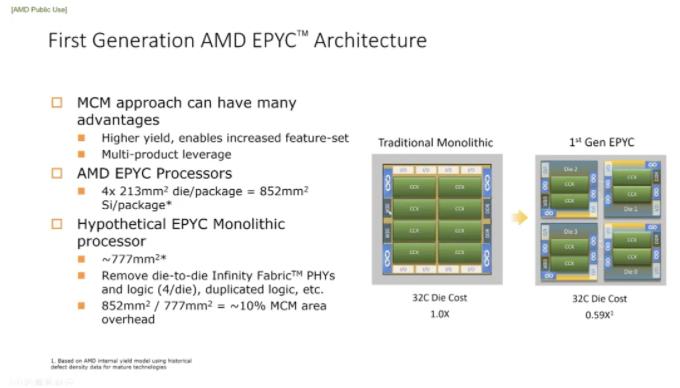

Chiplet模型已被證明是可行的,如英特爾、AMD和Marvell公司,他們設計了自己的chiplet和互聯。現在,業內其他公司也正在積極探索chiplet,因為對許多公司來說,擴展變得過于困難和昂貴,而遷移到新節點的功耗和性能優勢正在縮小。先進封裝提供了一種在不同的技術節點上組合chiplet的方法,而chiplet則提供了一種互聯RC延遲的解決方案。使用Chiplet還有望更快地開發復雜芯片,并且可以針對特定市場和應用進行定制。

為了開發一個復雜的集成電路產品,傳統方案是供應商設計一個芯片,將所有功能集成在同一個die上;后續的每一代產品中,die的函數數量都會顯著增加。在最新的7nm/5nm節點上,這種方案對應的成本和復雜性都在飆升。

谷歌的高級技術開發工程師Mudasir Ahmad表示:“新節點的設計成本在不斷上升。目前,制造一個5nm芯片的成本,幾乎等于制造10nm和7nm芯片的成本之和。這是非常昂貴的。”

雖然傳統方法仍然是芯片設計的一個可選方案,但chiplet為客戶提供了另一種解決方案。與任何新技術一樣,chiplet集成并不簡單。目前,基于chiplet的設計只用于高端產品,而不是日常設計。即便如此,也需要幾大要素才能打造出基于chiplet的模型。只有少數大公司擁有所需的專業知識和能力,其中大部分是私有的。所有這些,都導致采用基于chiplet的方法僅局限于少數。

現在,讓基于chiplet的設計更容易實現的工作正在進行中。包括以下幾點:

ASE、AMD、Arm、谷歌、英特爾、Meta、微軟、高通、三星、臺積電組成新的chiplet聯合體。該小組發布了一個新的、開放的die-to-die互聯規范,使chiplet可以在同一個封裝中相互通信;

ODSA子項目正在對類似的技術進行最后的潤色。ODSA也剛剛發布了一個新的成本分析工具,以幫助確定給定的基于chiplet的設計是否可行;

幾家封裝公司正在開發制造技術,將基于chiplet的設計投入生產。

Chiplet挑戰

一般來說,開發一個基于chiplet的設計,第一步是產品定義,然后需要產品架構、KGD(known-good die)和die-to-die互聯,此外還需要一個健全的制造策略。

KGD是設計中使用的die或chiplet。Die-to-die互聯允許chiplet在設計中相互通信。通過開發或采購這些組件,芯片客戶至少在理論上可以開發基于chiplet的設計。

但最大的問題是這種設計是否可行或是否具有成本效益。對于規避風險的芯片客戶來說,這可能是主要障礙。

為了幫助這些客戶,ODSA發布了一個成本分析軟件工具,列出了開發基于chiplet的設計所涉及的所有可能的組件和成本。

Ahmad表示:“沒有普適性法則確定是否應該使用chiplet,這完全取決于具體的應用。我們需要一個模型,可以對每個應用提供反饋。現在芯片客戶可以通過一個公共框架將數據輸入其中,然后可以嘗試理解為特定應用使用chiplet是否有意義。”

成本并不是唯一的因素。工程師們還必須正視chiplet帶來的挑戰,Ahmad表示,以下是其中的一些挑戰:

報廢成本:如果一個chiplet在最終設計中有缺陷,整個設備可能會報廢,這就增加了報廢成本;

測試:為了最小化報廢損失,設計需要更高的測試覆蓋率;

良率:封裝的復雜性可能會影響總體良率;

性能:將信號從一個die移動到另一個die,可能會降低產品的性能。

商業模式是另一個挑戰。Ahmad表示:“如果有不同的供應商提供不同的組件,最終產品出現問題后,誰來承擔責任?如何劃分責任?”

架構、KGD、互聯

成本和技術上的挑戰只是chiplet的一部分。客戶還必須定義產品,并為設計選擇一個體系結構。

這里有很多選擇。客戶可以將die合并到一個現有的高級封裝或一個新的架構。

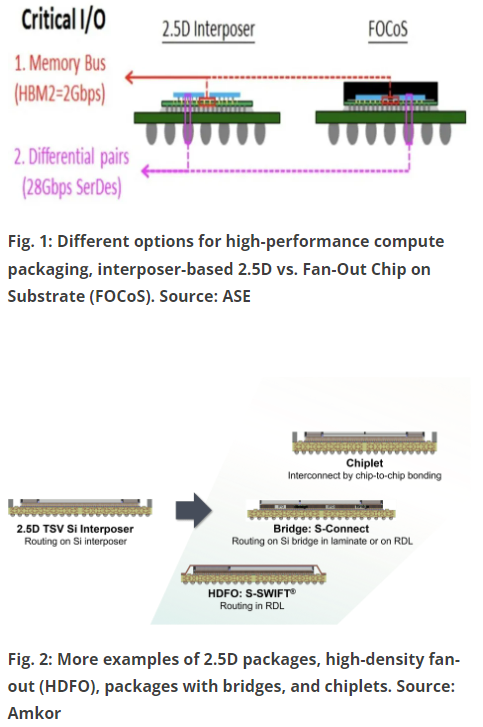

Fan-out是一種選擇。作為fan-out封裝的一個典型,DRAM芯片堆疊在封裝中的邏輯芯片上。

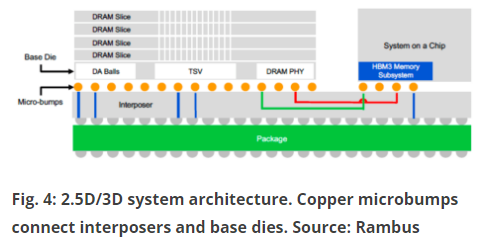

2.5D是用于高端系統的另一選擇。在2.5D中,die堆疊在一個插接器上,側對側連接。該插接器集成了通硅孔(TSV),TSV提供了die到電路板的電氣連接。舉個例子,ASIC和高帶寬內存(HBM)被并排放置在插接器上,這里HBM是一個DRAM內存棧。

另一種選擇是在新的3D架構中加入chiplet。例如,英特爾的GPU架構,代號為Ponte Vecchio。該設備在一個封裝中包含了5種不同節點的47個貼片或chiplet。

任何基于chiplet的架構都需要KGD。如果沒有KGD,整個封裝可能會面臨低良率或功能失敗。

ASE工程技術營銷總監Lihong Cao在最近一次活動中表示:“我們收到裸die,將其放入封裝中,以交付具有特定功能的產品。關于KGD,我們希望它的功能是經過全面測試的,良率是100%。”

這不是唯一的挑戰。在一個封裝中,一些die被堆疊在一起,而另一些則在其他地方,所以還需要die-to-die互聯。

如今的chiplet設計使用專有互聯技術連接die,這限制了chiplet普及。QP Technologies母公司Promex的總裁兼CEO Richard Otte表示:“標準化是chiplet成為新IP的最大障礙,必須在chiplet之間建立標準/通用的通信接口。”

好消息是,一些組織正在研究chiplet的開放式die-to-die互聯標準。目前,有幾種相互競爭的技術,目前還不清楚哪一種會勝出,也不清楚它們將如何結合。

ODSA正在準備一種名為Bunch of Wires(BoW)的die-to-die互聯技術。其他die-to-die技術包括高級接口總線(AIB)、CEI-112G-XSR和OpenHBI。

最近,由英特爾、三星、臺積電和其他公司支持的一個新的chiplet聯盟發布了UCIe,這是一個涵蓋了die-to-die I/O物理層、die-to-die協議和軟件棧的規范。

上述所有規范都定義了封裝內chiplet之間的標準互連,但它們都是不同的。Cao表示:“UCIe和BoW都是開放規范,定義了封裝內chiplet之間的互連,并使開放的chiplet生態系統成為可能。但它們在層的定義上和優化應用上有所不同。”

事實證明,沒有一種互聯技術可以滿足所有的需求。工程師將選擇一個滿足給定應用要求的選項。長電科技CEO Choon Lee表示:“各種標準之間存在重疊的子集。所以堅持一個標準可能沒有什么意義。一般情況下,chiplet的功能塊由設備制造商定義,他們知道如何優化chiplet之間的連接。”

Chiplet堆疊/鍵合

一旦定義了芯片架構、KGD和互連,下一步就是確定是否有必要將產品投入生產。

和以前一樣,封裝或chiplet設計可以在晶圓廠、存儲器制造商或OSAT進行制造和組裝。每個供應商都在開發一種或多種不同的方法來組裝、堆疊和連接不同的chiplet。先進的鍵合技術有熱壓鍵合、激光輔助鍵合和銅混合鍵合。

熱壓鍵合(TCB)和激光輔助鍵合(LAB)都利用了傳統的帶銅微凸點的倒裝芯片工藝。在這個過程中,一個die上會形成銅凸起,然后使用倒裝片粘結器(LAB或TCB)將設備粘結到另一個結構上。相比之下,銅混合鍵合使用銅互連堆疊/連接die,而不是傳統的凸點。

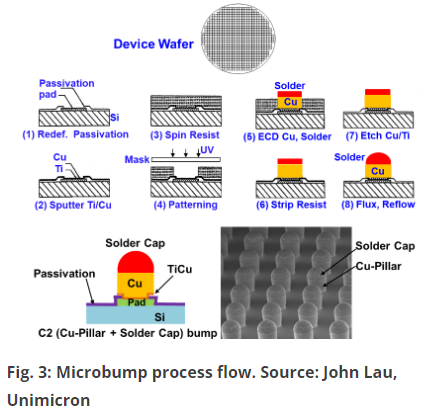

傳統的倒裝芯片工藝用于制造幾種封裝類型。其中一種稱為BGA,用于多種芯片應用。

要制造BGA封裝,首先要在晶圓廠的晶圓上制造芯片。然后,在晶圓片的一側形成基于焊料的微小銅凸點。銅凸點連接一個die到另一個die或封裝中的基板。這些突起在不同結構之間提供了小而快速的電連接。

一般情況下,倒裝焊片用于300μm至50μm凸塊間距(Bump Pitch)下的die堆疊/互聯。現在,凸塊間距已經達到40μm及以下。

所以該行業需要一種先進封裝解決方案,使用最先進的銅微凸點,針對40μm及以下的凸塊間距。在這種情況下,使用傳統的倒裝芯片互聯技術是很有挑戰性的。對于更小的間距,一些封裝廠使用TCB在40μm至10μm凸塊間距下進行die堆積和互聯。

對于2.5D/3D封裝,一般采用TCB進行芯片堆疊和互聯。

同時,LAB也是可行的。在LAB工藝中,使用傳統的凸塊工藝在die上形成微小的銅凸點。然后,將die和基板放置在LAB工具中。該系統利用激光產生的熱量將die對準并連接到基板上。

在LAB系統中,在低熱應力的情況下,粘合過程耗時不到一秒。可以看出,LAB比TCB更快,但它需要來自特定供應商的專門設備。

Amkor和長電科技正在開發LAB。該技術自2019年左右開始投入生產。長電科技的Lee說:“LAB已經在高性能計算應用上投入生產,在這些應用中,由于翹曲或殘余應力造成的凸塊non-wet或開裂可能是至關重要的。”

OSAT希望將LAB推至10μm左右。Amkor高級封裝開發和集成副總裁Michael Kelly表示:“我們已經演示了使用銅無鉛凸起和激光輔助連接方法,將間距降低到10μm。我們的產品在20μm下已經合格,這些都是片上芯片,大多數是專用傳感器。”

混合鍵合

TCB和LAB的凸距均可達到10μm。除此之外,行業需要一種新的解決方案,即銅混合鍵合,這種方案使用細間距銅連接直接堆疊/連接die,而不是傳統的微凸點。

銅混合鍵合并不是什么新鮮事。2005年,Ziptronix推出了一種名為低溫直接鍵連接(DBI)的技術,被認為是銅混合鍵合的第一個版本。(2015年,Tessera收購了Ziptronix;2017年,Tessera更名為Xperi。)

2015年,索尼授權DBI,并將該技術用于其CMOS圖像傳感器生產線。首先,兩個不同的晶圓在一個晶圓廠加工。第一個晶圓由許多處理器芯片組成;第二個晶圓由多個像素陣列晶圓組成。

目標是將每個像素陣列芯片堆疊在每個處理器芯片上。為此,兩個晶圓被插入到一個晶圓鍵合器中。首先形成介電鍵,然后是金屬對金屬的連接,最后對晶圓片上的die進行切割和封裝,得到圖像傳感器。

使用Xperi的DBI工藝,Sony和OmniVision分別生產了3.1μm和3.9μm間距的CMOS圖像傳感器。

現在,該行業正在開發用于3D芯片和封裝應用的銅混合鍵合。AMD、Graphcore和YMTC已經宣布了使用混合鍵合的產品。

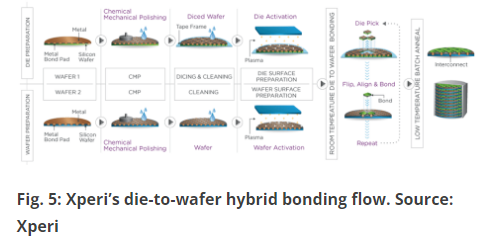

在封裝中,wafer-to-wafer和die-to-wafer的鍵合都采用混合鍵合。在die-to-wafer工藝中,晶圓廠加工兩個晶圓。然后,將第一個晶圓上的die切割出來并使用混合鍵合連接到第二個晶圓上。

Die-to-wafer為封裝客戶提供了更多選擇,但這是一個具有挑戰性的過程。Xperi產品營銷副總裁Abul Nuruzzaman表示:“CMOS圖像傳感器是通過wafer-to-wafer的混合鍵合形成的,鍵合的die具有相似的尺寸,兩種wafer具有成熟的硅供應鏈和工藝,良率足夠高。在2.5D或3D先進封裝中,有時需要一種die-to-wafer鍵合技術。它需要KGD,不同的die尺寸,不同工藝節點或晶圓尺寸下的die。切割、die處理和組裝必須與混合鍵合工藝兼容,這對行業來說是相對較新的。”

除Xperi外,Imec、Intel、Leti、Micron、Samsung和TSMC也在開發銅混合鍵合工藝。

結論

到目前為止,只有少數供應商開發和制造了基于chiplet的設計。為了使這項技術得到更廣泛的應用,幾個關鍵的組成部分正在落地。

考慮到在先進節點上開發芯片的成本不斷上升,業界比以往任何時候都更需要chiplet。

審核編輯 :李倩

-

集成電路

+關注

關注

5389文章

11574瀏覽量

362313 -

3D芯片

+關注

關注

0文章

52瀏覽量

18439 -

chiplet

+關注

關注

6文章

434瀏覽量

12606

原文標題:Chiplet普及之路已開啟!

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

解鎖Chiplet潛力:封裝技術是關鍵

啟明云端2024火山引擎FORCE原動力大會·冬正在進行中,共赴AI探索未來科技盛宴

Chiplet在先進封裝中的重要性

TI研討會正在進行中,米爾誠邀您參與

阿維塔正在進行C輪百億融資

IMEC組建汽車Chiplet聯盟

預決賽節點公布丨第七屆CCF開源創新大賽火熱進行中!

突破與解耦:Chiplet技術讓AMD實現高性能計算與服務器領域復興

使用stm8l的外部中斷的pin7的中斷,進行中斷處理時會立刻造成新的pin7中斷,會有什么影響嗎?

Chiplet是否也走上了集成競賽的道路?

什么是Chiplet技術?

Chiplet成大芯片設計主流方式,開啟IP復用新模式

SOLIDWORKS 2024通過自動化和縮短工作流程來實現智能工作

基于chiplet的設計更容易實現的工作正在進行中

基于chiplet的設計更容易實現的工作正在進行中

評論