為了在用戶級別保持可接受的性能特征,固態驅動器 (SSD) 的存儲系統設計人員必須開發復雜的架構和算法來解決 NAND 閃存的固有限制。這些變通辦法促成了快速可靠的內存解決方案,這些解決方案已經成功地為存儲系統提供了幾十年的動力,但時間不長。這就是為什么。

除了與行業向更小和更簡單技術發展的趨勢背道而馳之外,復雜的變通方法系統還影響了整體性能和成本,同時也造成了主要的系統瓶頸,隨著技術節點的不斷縮小,預計只會惡化

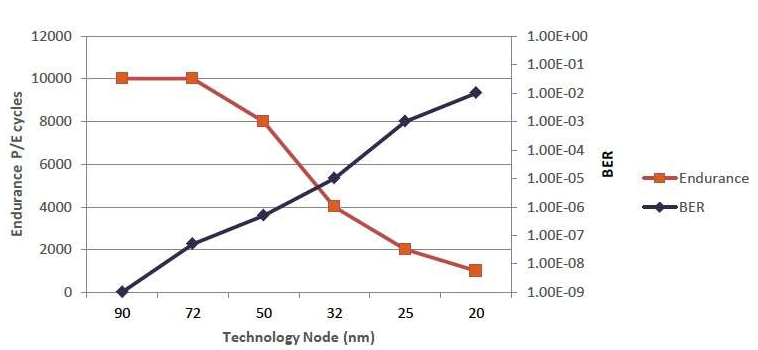

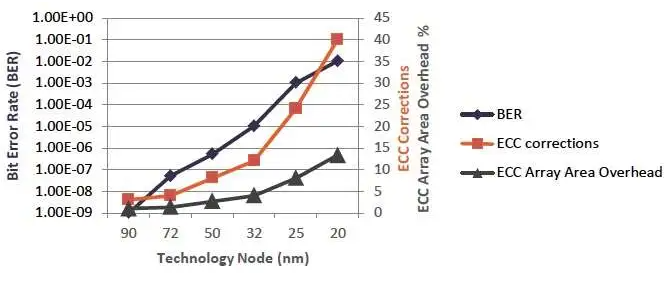

例如,當縮小到 25nm 以下時,NAND 閃存的耐用性和可靠性會嚴重下降,以至于現在采用的解決方法幾乎無濟于事(圖 1)。此類性能指標促使整個行業競相開發更強大的非易失性存儲器 (NVM) 解決方案,通過簡化存儲器的工作方式來滿足下一代電子設備的容量、性能、功率和可靠性要求。

那么,是什么阻礙了 NAND 閃存呢?設計約束。固有的設計約束。本文將討論 NAND 閃存面臨的挑戰,因為制造商試圖縮小規模,特別是在固態驅動器方面,并涵蓋將改變 NVM 市場格局的新興內存技術。

圖 1 NAND 耐用性和誤碼率 (BER) 趨勢 — 隨著技術節點的減少,NAND 耐用性周期減少并且 BER 增加。耐用性衡量一個存儲單元在變得容易出錯以至于無法使用之前可以承受多少個周期。BER 測量每個存儲器陣列的誤碼率。

NAND 閃存設計約束

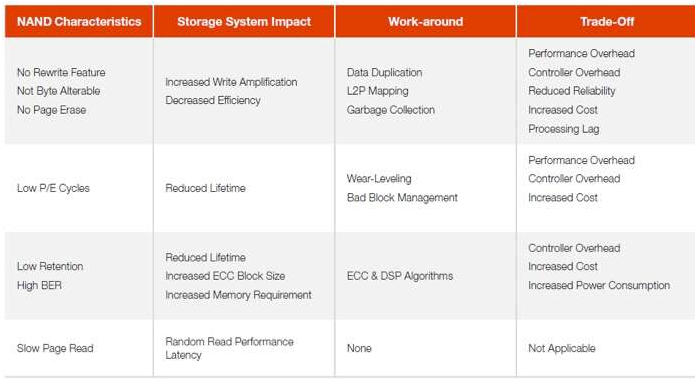

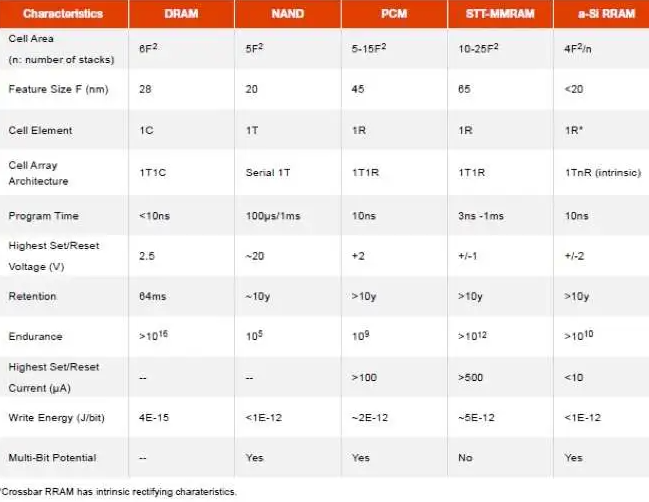

在最近開發的基于閃存的 SSD 中,內存訪問由連接到 DRAM 緩沖區和多個原始 NAND 閃存組件的高端內存控制器芯片管理。盡管大多數精通技術的人都知道 NAND 閃存技術的局限性,但對現有解決方法的深入研究可以說明它們如何影響 SSD 和整個系統。這些特征總結在表 1 中。

表 1 NAND 特性和存儲系統相關解決方法的總結。

Block Erasure

NAND Flash 技術只能擦除塊并且只能編程頁面。它無法在不擦除整個塊的情況下以任何粒度(字節、頁或塊)修改完全編程的塊,這是一種設計約束,它通過以下解決方法增加了整體復雜性:數據復制、邏輯到物理映射表(L2P )、緩沖和垃圾收集。

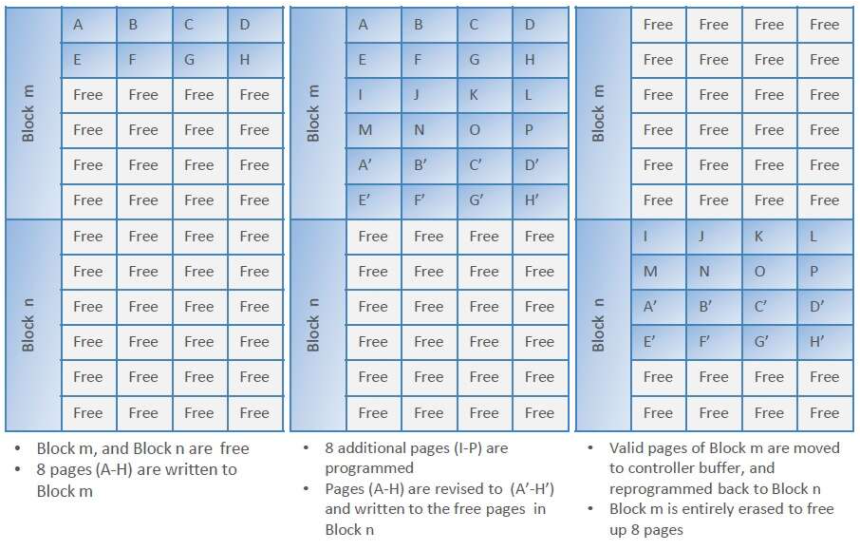

數據復制: 對于數據的修改,NAND系統控制器必須首先將數據讀入一個臨時內存位置(如DRAM),然后在需要時將讀取的數據與修改后的數據合并,最后將修改后的數據重寫到新的頁面(圖2)。

L2P 映射:因此,每次執行此過程時,控制器都必須更新和維護 L2P 映射表。L2P 保存原始和修改的數據位置,指導主機訪問和執行數據管理過程。存儲設備的容量越大,這些表就需要越大。因此,大多數控制器必須使用外部 DRAM 來維護這些較大的表。

垃圾收集:修訂過時的頁面,也稱為陳舊數據,無法擦除或覆蓋;相反,它們被另一種稱為垃圾收集的控制器啟動的解決方法釋放。圖 2 演示了垃圾收集過程之后的數據修訂過程。

圖 2垃圾收集過程 - 發生 24 個頁面寫入以重寫 8 個頁面,這意味著寫入放大 (WA) 等于 3,是理想效率衡量標準的三倍。

對寫放大的影響

重要的是要注意此示例中的控制器執行 24 頁寫入以完成 8 頁的預期重寫。

寫放大 (WA) 通過定義控制器對 NAND 進行的每次來自主機的預期寫入的寫入次數來衡量控制器的效率。WA 表示理想的效率——每次主機寫入一次寫入 NAND 設備。大多數系統的 WA 通常在 3 到 4 之間。更高的 WA 直接影響存儲設備的可靠性和性能,因為它會增加對設備的寫入次數,從而更快地使單元達到其最大周期。這對于較小的技術節點尤其重要,其中存儲單元的最大周期降至三千以下(參見圖 1)。

在圖 2 所示的示例中,可以通過獲取塊中的總頁數 (24) 并將其除以釋放的頁數 (8) 來定義寫入放大。因此,在這種情況下,WA 是 3。

低編程/擦除周期 – 低耐用

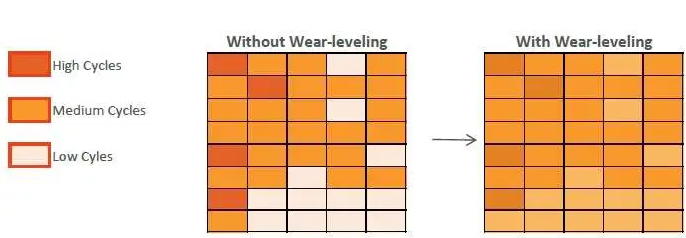

性 NAND 閃存的一個固有特性是其單元的低耐用性,由單元在變得不可靠之前可以經歷的最大編程/擦除周期定義。盡管如此,NAND 閃存仍能夠通過磨損均衡和壞塊管理等變通辦法來維持系統壽命,這兩者都會增加控制器和性能開銷以及成本。

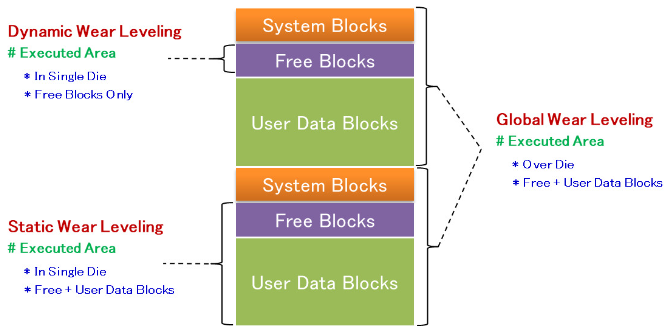

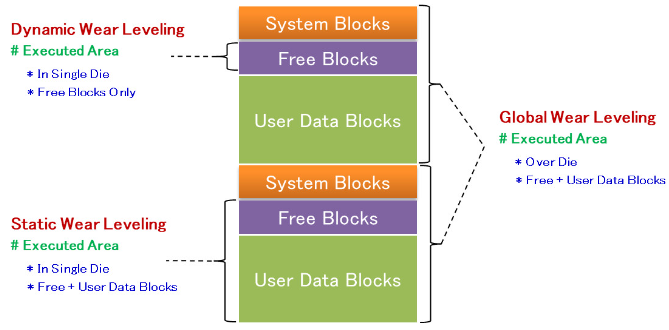

磨損均衡: 磨損均衡算法使循環塊的數量盡可能均勻,與主機操作系統和文件系統無關。如果沒有磨損均衡,一些存儲單元會累積高周期,如圖 3 所示,從而縮短存儲系統的壽命。系統控制器必須支持這一強制性流程以延長產品壽命,這會增加控制器的計算和管理開銷。

圖 3磨損平衡 — 實施磨損平衡算法以提高和最大化存儲系統的耐用性和使用壽命。

壞塊管理: 當一個塊達到其周期最大值時,數據可能由于“浮柵到浮柵耦合”的電荷泄漏或讀/寫干擾而損壞。壞塊管理執行寫入驗證以查找故障扇區。如果發現任何錯誤,壞塊管理會映射它們以防止更多數據存儲在這些塊中——實質上是淘汰這些塊。在較小的節點上,當最大周期已經以驚人的速度減少時,塊將需要盡快退出,同時消耗寶貴的內存空間來存儲跟蹤這些塊的映射。

來自低保留 NAND 閃存的高誤碼率 (BER)

有出現錯誤的趨勢,這是通過 BER 來衡量的。為了監控和糾正錯誤,NAND 閃存使用糾錯碼 (ECC)。但是在較小的節點上,隨著 BER 的不斷增加,ECC 的復雜性也必須增加。圖 4 說明了 20nm NAND 閃存需要對 1KB 數據進行超過 40 次 ECC 校正,從而以指數方式增加 ECC 算法的復雜性、存儲 ECC 字所需的分配空間以及處理相關復雜性所需的控制器開銷。

圖 4 ECC 和 BER — 20nm 閃存需要對 1KB 數據進行超過 40 次 ECC 校正。

更大的 ECC: 在 20nm NAND 閃存陣列中,用于存儲 ECC 奇偶校驗位的硅存儲器的開銷區域使總陣列大小增加了 10%。這種陣列尺寸的增加與下一代存儲系統的要求特別相關,因為它表明 NAND 在適應未來在更小技術節點上實現更大內存密度的趨勢的能力有限。

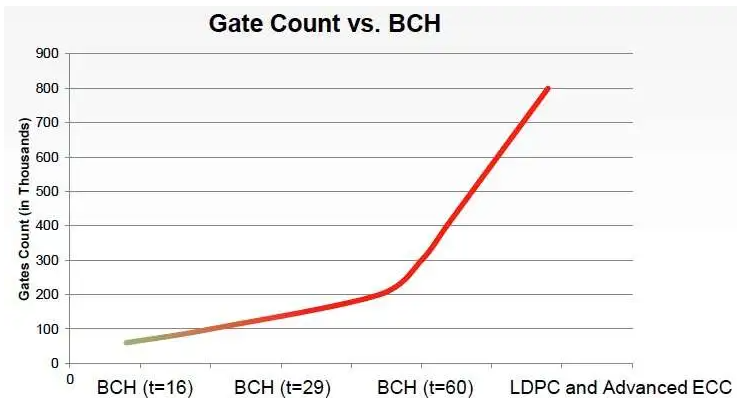

更強大的 ECC: 此外,隨著 NAND 閃存容量的不斷增加,其可靠性不斷下降,傳統的 ECC,例如常用的 BCH 代碼,已經越來越不適合 SSD。為了有效提高 SSD 的可靠性,需要更強大的 ECC,例如 LDPC 碼。

然而,與 BCH 處理相比,LDPC 實現需要更強大和更復雜的處理以及更多的晶體管數量,如圖 5 所示。雖然使用硬判決的 LDPC 碼解碼可以實現比傳統 BCH 碼顯著的編碼增益,但軟判決可以顯著提高LDPC碼解碼糾錯強度。從 NAND 讀取和處理軟信息會導致存儲系統的讀取響應時間不可預測,這是企業應用程序中不希望出現的副作用。

圖 5門數——低密度奇偶校驗碼需要比傳統 BCH 更多的晶體管門數。

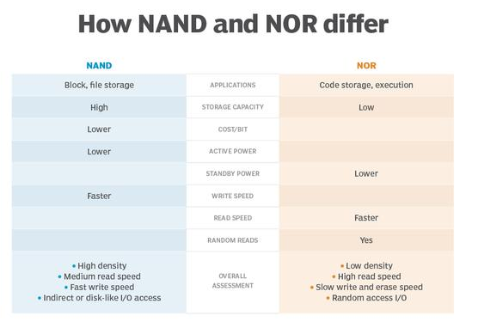

頁面讀取

速度慢 基于 NAND 閃存的存儲系統的另一個固有問題是頁面讀取速度慢 50μs。這種延遲不足以支持企業存儲系統和實時嵌入式內存應用程序。諸如此類的系統需要低于 100ns 的讀取訪問時間。迄今為止,NAND Flash還沒有解決辦法。NAND存儲單元的讀取電流非常低,不到300nA,目前的存儲架構設計無法提供快速的隨機讀取操作。

NAND Flash 對存儲控制器的影響

由于這些設計復雜性,基于 NAND 的存儲控制器不僅體積更大,而且必須使用更多的幕后內存,而犧牲實際的“工作內存”或最終用戶記憶。原因如下:

ECC: ECC 塊必須大得多,因為在較小的技術節點上 NAND 的 BER 較高。

緩沖: 需要增加緩沖來維護 L2P 表和增加數據復制過程。

DRAM: 外部 DRAM 通常用于維護較大的 L2P 表。

多核中央處理器單元 (CPU): 大多數高性能存儲控制器使用多核 CPU 來處理垃圾收集和磨損均衡算法,并跨多個通道管理 L2P 表和 NAND 設備。

增加 CPU 帶寬: CPU 的大部分帶寬用于定期將表存儲在 NAND 中,以防意外電源中斷。這些表必須在斷電后完全恢復……否則數據將丟失。

壓縮引擎: 壓縮引擎用于通過減少寫入 NAND 的實際主機數據來降低寫入放大。

由于這些衰退趨勢以及 NAND 閃存所面臨的障礙,存儲系統制造商已經意識到通過不受閃存技術的可擴展性問題和設計限制的新技術突破來解決存儲系統問題的重要性。

經過多年的深入研究和開發,最有希望的候選者之一通常被認為是電阻式 RAM (RRAM)。

表 2當前技術與新興技術的比較,包括稱為 a-Si RRAM 的高性能 RRAM 類型。

RRAM 的工作原理

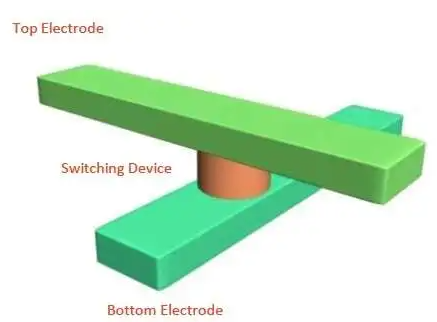

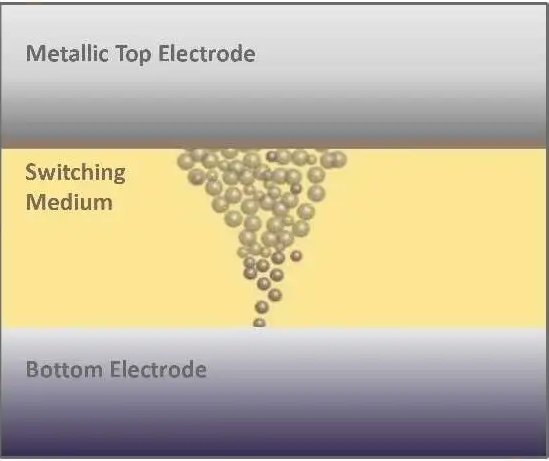

一個典型的設備由兩個金屬電極組成,它們夾在一個薄的介電層中,作為離子傳輸和存儲介質(圖 6)。

所使用的不同材料之間的確切機制存在顯著差異,但所有 RRAM 器件之間的共同聯系是電場或熱量會導致離子運動和存儲介質中的局部結構變化,進而導致器件電阻發生可測量的變化。

圖 6交叉開關架構中的典型 RRAM 單元

圖 7工作原理 - 在開關介質中,納米顆粒在頂部和底部電極之間形成傳導路徑。

盡管有幾種類型的 RRAM 技術正在開發中(見邊欄),但 RRAM 技術面臨的最常見挑戰是溫度敏感性和 CMOS 不兼容。

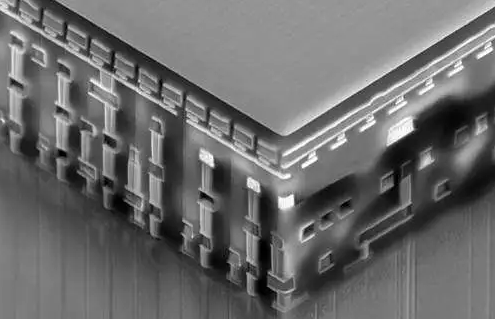

一種類型是 a-Si RRAM,它采用常用的非晶膜,例如非晶硅 (a-Si),作為形成燈絲的主體材料。在電阻切換期間產生的導電“細絲”由離散的金屬顆粒組成,而不是在其他 RRAM 方法中發現的連續金屬塞。這些特性帶來了許多性能優勢,有望消除 Flash 面臨的許多問題。Crossbar, Inc. 是一家總部位于加利福尼亞的公司,已成功開發出使用該技術的演示產品(圖 8)。

圖 8 Crossbar 的集成器件 RRAM 產品

表3常用RRAM類型比較

a-Si RRAM 技術展示的主要特性 是

什么讓 a-Si RRAM 成為如此有前途的候選者?與 NAND Flash 無法跟上技術節點減少的原因相同,a-Si RRAM 可以。它固有的簡單、兼容的元素使 a-Si RRAM 成為支持下一代技術的精確設計。

可擴展性: a-Si RRAM 能夠縮小到 5nm 節點,將能夠跟上未來幾十年存儲系統的發展。

3D 可堆疊和 MLC 能力: 非常大的 R off /R on比率 (》1000) 可提供較大的傳感余量并支持 MLC(多層單元)操作。與基于 NAND 的存儲器技術相比,可堆疊存儲器與 MLC 存儲器單元相結合可提高存儲器密度并降低每比特成本。

耐用性: 具有高耐用性(》10E10),a-Si RRAM 的循環特性明顯優于 NAND。這大大減少了對磨損均衡的需求,并降低了主機控制器的 ECC 要求,從而提高了整體系統性能和功耗。

保留: Crossbar, Inc. 對 a-Si RRAM 進行并成功通過了 85°C 十年保留測試。預計與 NAND 相比,該技術將具有出色的保留率和 BER。

高速: 因為 a-Si RRAM 單元的單元電流比 NAND 高幾個數量級,所以存儲器陣列提供更快的頁面讀取。快速頁面讀取可實現更快的隨機訪問,非常適合企業存儲內存和實時內存系統。

字節和頁面可更改性: 此特性通過消除寫入放大和垃圾收集所需的系統開銷,大大提高了性能和可靠性。

突破性的基于 RRAM 的存儲解決方案

基于 RRAM 的 SSD 控制器不受 NAND Flash 給存儲系統帶來的諸多負擔。

在基于 RRAM 的存儲控制器中,CPU 不需要管理 L2P 表或處理相同級別的垃圾收集和磨損均衡。有了這些較低的需求,基于 RRAM 的存儲控制器將得到簡化,并且成本將低于基于 NAND 的存儲控制器。

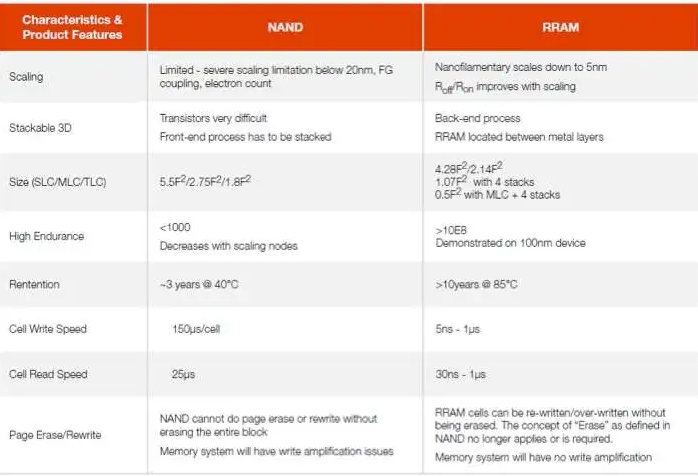

下表 4 列出了比較 NAND 和 RRAM 技術的不同單元級和產品級特性。這些特性表明,基于 a-Si RRAM 的存儲系統將在需要高性能、功率或耐用性以實現高容量、高速和低成本的新興應用中提供卓越的性能和可靠性。

表 4在單元和產品級別上基于 NAND 和基于 RRAM 的性能概覽比較。

關于設計和 CMOS 兼容性的一句話

使 a-Si RRAM 從其他新興技術中脫穎而出的原因在于它非常易于集成。與許多新技術中使用的材料不同,a-Si RRAM 中使用的非晶硅薄膜具有良好的特性和堅固性,并且已經在 CMOS 晶圓廠中使用。例如,Crossbar, Inc. 開發的內存可以是一個獨立的陣列,也可以嵌入到 CMOS 頂部的后端中,形成多個 3D 堆疊層。

目前,RRAM 可以在后端 (BEOL) 工藝中制造,因為大多數 RRAM 單元的操作不依賴于晶體管。在典型的工藝基礎中,晶圓制造(包括地址和傳感電路)將在 CMOS 代工廠中制造,然后在同一工廠或單獨的 BEOL 存儲器工廠中制造 RRAM 存儲器。Crossbar Inc. 進行了多項測試,以確保他們的產品與 CMOS 兼容,并且已經使用不同的工具集在多種集成方案上展示了他們的內存陣列。

集成: 集成 a-Si RRAM 涉及圖案化和減材蝕刻工藝。該工藝流程具有重復的塊以實現存儲元件的堆疊。a-Si RRAM 集成使用各種晶圓廠常用的標準工藝步驟和工具。

在過去的幾十年里,NAND 對固態存儲設備中的系統控制器提出了苛刻的任務。這些管理任務增加了系統復雜性、功耗、晶體管門數和整體存儲系統開發成本。

a-Si RRAM 技術的突破性特性,例如 Crossbar Memory,為存儲設備提供了高性能規格和靈活的功能,例如無需擦除塊即可重寫到存儲位置的能力。簡化的設備可簡化存儲系統并顯著降低系統控制器開銷,從而為后代創造新興技術提供支持。

作者Hagop Nazarian和Sylvain Dubois

-

CMOS

+關注

關注

58文章

5733瀏覽量

235875 -

NAND

+關注

關注

16文章

1687瀏覽量

136332 -

RRAM

+關注

關注

0文章

28瀏覽量

21360

發布評論請先 登錄

相關推薦

Xilinx Spartan 6是否支持NAND閃存?

關于不同NAND閃存的種類對比淺析

你知道NAND閃存的種類和對比?

解析NAND閃存和NOR閃存

NAND閃存芯片有哪些類型

NAND閃存的應用中的磨損均衡

NAND閃存應用中的磨損均衡介紹

NAND閃存面臨的挑戰,是什么阻礙了NAND閃存?

NAND閃存面臨的挑戰,是什么阻礙了NAND閃存?

評論