這就要根據(jù)信號(hào)的特征來確定了,差分走線一般用于高速信號(hào)傳輸當(dāng)中,可以有效減少干擾。差分走線是在需要進(jìn)行差分阻抗匹配的時(shí)候才能夠使用,此外,等長匹配的時(shí)候也可以用,但僅僅只是用于等長而已。

差分走線有哪些優(yōu)勢(shì)呢

1、能有效抑制EMI;

2、抗干擾能力強(qiáng);

3、時(shí)序定位精確。

本文綜合整理自青青河邊草er、百度網(wǎng)友3a080c612、瀛洲煙雨

責(zé)任編輯:lq6

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

相關(guān)推薦

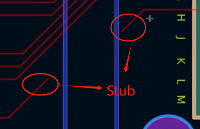

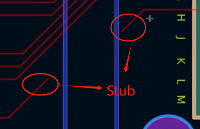

PCB設(shè)計(jì)中應(yīng)盡量減少Stub的存在,或者在無法完全避免Stub的情況下,通過優(yōu)化Stub的長度和幾何形狀來降低它們對(duì)信號(hào)的影響。

![的頭像]() 發(fā)表于

發(fā)表于 12-20 18:28

?215次閱讀

ad,cadense 阻抗匹配計(jì)算和差分走線設(shè)置

發(fā)表于 10-17 16:59

?2次下載

一站式PCBA智造廠家今天為大家講講什么是PCB設(shè)計(jì)爬電距離?PCB設(shè)計(jì)爬電距離的重要性。在電子制造業(yè)中,

![的頭像]() 發(fā)表于

發(fā)表于 09-26 09:39

?579次閱讀

詳細(xì)探討差分信號(hào)的幾個(gè)顯著優(yōu)點(diǎn),這些特點(diǎn)使其在許多高端電子設(shè)計(jì)中成為首選的信號(hào)傳輸方式。 強(qiáng)大的抗干擾能力:在充滿電磁噪聲的環(huán)境

![的頭像]() 發(fā)表于

發(fā)表于 09-10 10:30

?659次閱讀

射頻(RF)電路的PCB設(shè)計(jì)是一個(gè)復(fù)雜且要求精確的過程,涉及到信號(hào)完整性、電磁兼容性、熱管理、材料選擇等多個(gè)方面。 射頻電路PCB設(shè)計(jì)概述 1. 信號(hào)完整性(SI) 阻抗匹配 :確保傳輸線

![的頭像]() 發(fā)表于

發(fā)表于 09-07 10:02

?617次閱讀

在PCB設(shè)計(jì)中,坐標(biāo)原點(diǎn)是一個(gè)非常重要的概念,它決定了PCB布局的起始位置和方向。 一、坐標(biāo)原點(diǎn)

![的頭像]() 發(fā)表于

發(fā)表于 09-02 14:45

?2621次閱讀

一站式PCBA智造廠家今天為大家講講PCB設(shè)計(jì)與PCB制板有什么關(guān)系?PCB設(shè)計(jì)與PCB制板的關(guān)系。PC

![的頭像]() 發(fā)表于

發(fā)表于 08-12 10:04

?567次閱讀

/O接口,信號(hào)走線和參考平面都是將信號(hào)從PCB上的一個(gè)位置傳輸?shù)搅?b class='flag-5'>一個(gè)位置所必需的。對(duì)于差分I/O接口,傳輸

發(fā)表于 07-19 16:56

一站式PCBA智造廠家今天為大家講講PCB設(shè)計(jì)中的常見問題有哪些?PCB設(shè)計(jì)布局時(shí)容易出現(xiàn)的五大常見問題。在電子產(chǎn)品的開發(fā)過程

![的頭像]() 發(fā)表于

發(fā)表于 05-23 09:13

?950次閱讀

建議采用多層PCB設(shè)計(jì),以提供更多的布線層和地層。這有助于降低電阻、電感和噪聲,并提高PCB的抗干擾能力。在儲(chǔ)能系統(tǒng)中,信號(hào)的穩(wěn)定傳輸是至關(guān)重要的,因此合理的

發(fā)表于 05-14 11:25

?1145次閱讀

作為電子設(shè)計(jì)中重要組成部分,在PCB設(shè)計(jì)中出現(xiàn)電磁問題時(shí)如何解決呢?本文將從多方面細(xì)節(jié)探討問題要點(diǎn),可以采取以下解決辦法來降低或消除電磁干擾(EMI): 1.合理的

發(fā)表于 05-08 14:39

?3170次閱讀

在PCB設(shè)計(jì)中,差分走線是一種常見的信號(hào)傳輸方式,它

![的頭像]() 發(fā)表于

發(fā)表于 04-10 16:51

?3956次閱讀

在PCB設(shè)計(jì)中,差分對(duì)的走線操作是一項(xiàng)關(guān)鍵任務(wù),它直接影響到信號(hào)的完整性和電路的性能。

![的頭像]() 發(fā)表于

發(fā)表于 04-10 16:34

?2784次閱讀

差分走線是一種在高速PCB設(shè)計(jì)中常用的信號(hào)傳輸方式,它與射頻走

![的頭像]() 發(fā)表于

發(fā)表于 04-10 16:26

?2438次閱讀

在PCB設(shè)計(jì)中,如何避免串?dāng)_? 在PCB設(shè)計(jì)中,避免串?dāng)_是至關(guān)重要的,因?yàn)榇當(dāng)_可能導(dǎo)致信號(hào)失真、

![的頭像]() 發(fā)表于

發(fā)表于 02-02 15:40

?1886次閱讀

探討一下在PCB設(shè)計(jì)中的差分走線

探討一下在PCB設(shè)計(jì)中的差分走線

評(píng)論