繼年前介紹的時序邏輯電路之時鐘分頻后,今天我們來介紹第7講:流水燈。

流水燈,有時候也叫跑馬燈,是一個簡單、有趣又經典的實驗,基本所有單片機的玩家們在初期學習的階段都做過。本次我們也來介紹一下如何通過小腳丫FPGA實現一個流水燈。

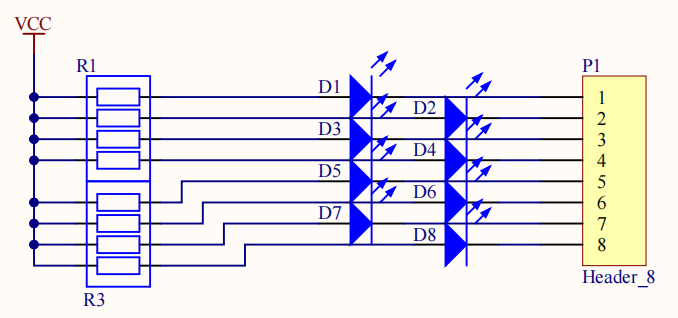

流水燈就是讓一連串的燈在一定時間內先后點亮并循環往復,所以其中的關鍵要領就在于控制每兩個相鄰LED亮滅的時間差,以及所有LED燈完成一組亮滅動作后的循環。很久都沒有用過小腳丫的朋友可以再回顧一下,這上面有8個LED燈,且低電平點亮。

實現流水燈的方法絕不止一種,在這里我們采用模塊化的設計思路,因為模塊化設計對于之后構建大型電路系統非常有幫助,并且我們還可以借機溫習一下以前學過的內容。

現在我們的目標是每過1秒后點亮下一個LED燈并且熄滅當前燈,且在第8個燈熄滅之后循環整個流程,該如何設計整個模塊?我們先上圖后解釋。

毫無疑問,第一步需要做的就是通過分頻來生成一個周期為1秒的時鐘信號,不了解時鐘分頻童鞋可以讀一下本系列的第6篇內容。

有了一個1秒鐘嘀嗒一次的時鐘后,我們還要考慮到循環問題,因為在第8個LED燈熄滅之后還需要再返回到第1個。那么這個時候我們就需要一個計數器,它的作用就是數羊,一只,兩只…。..數到第八只后重頭再來。數8只羊需要一個3位寬的變量(23=8)。

最后,由于我們是要依次點亮,也就是說8位的輸出中每次只有1位是低電平,其余均為高電平(小腳丫LED燈為低電平點亮)。這個特性正好對應了我們之前學過的3-8譯碼器。

現在我們再來捋一遍。首先,通過分頻在小腳丫上生成一個周期為1秒的慢速時鐘信號,這個時鐘信號傳送到計數器之中;這個計數器是3位寬的,因此最多可以計八次慢速時鐘的嘀嗒,并且計數每增加1時,都對應著3-8譯碼器的下一種輸出,也就對應著流水燈的下一個狀態。

現在我們上代碼:

module runningled (clk,led); input clk,rst; output[7:0] led; reg [2:0] cnt ; //定義了一個3位的計數器,輸出可以作為3-8譯碼器的輸入 wire clk1hz; //定義一個中間變量,表示分頻得到的時鐘,用作計數器的觸發 //例化分頻模塊,產生一個1Hz時鐘信號 divide #(.WIDTH(24),.N(12000000)) u2 ( //除數為12,000,000,因此頻率為1Hz .clk(clk), .rst_n(rst), .clkout(clk1hz) ); //生成計數器,上沿觸發并循環計數 always@(posedge clk1hz) cnt 《=《 span=“”》 cnt +1; // 達到位寬上限后可自動溢出清零 //例化3-8譯碼器模塊 decode38 u1 ( .X(cnt), //例化的輸入端口連接到cnt,輸出端口連接到led .D(led) );endmodule

在第四篇講譯碼器的文章里,我們介紹過,如果需要調用/例化子模塊時,需要將各子模塊與大模塊放入同一個工程文件下進行編譯。最后我們再來對小腳丫進行管腳配置并燒錄就可以了。

對應變量小腳丫管腳FPGA管腳

clkClockJ5

led [0]LED1N15

led [1]LED2N14

led [2]LED3M14

led [3]LED4M12

led [4]LED5L12

led [5]LED6K12

led [6]LED7L11

led [7]LED8K11

如果大家成功地在小腳丫上實現了流水燈的程序,還可以自己玩一個有意思的實驗:比如,你可以通過修改程序來提高流水燈的刷新頻率,然后看看LED燈的刷新率為多少時你的肉眼無法分別。同時再打開手機的攝像頭,也以同樣的方法試驗一番。結合到你觀察的現象,可以自己琢磨并思考一下,說不定能挖掘出更多的知識。

備注一些大伙都知道的常識:我國交流電工頻為50Hz,電腦常用顯示器的刷新率有60,75和144赫茲。華為Mate30刷新頻率為90赫茲,蘋果6-12的刷新頻率為60赫茲。

編輯:lyn

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605171 -

單片機

+關注

關注

6042文章

44617瀏覽量

637528 -

代碼

+關注

關注

30文章

4823瀏覽量

68894

原文標題:基于FPGA的數字電路實驗7:流水燈的實現

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字電路與控制系統關系

數字電路編程語言介紹

數字電路與模擬電路的區別

模擬電路與數字電路的區別

數字電路可以處理模擬信號嗎

數字電路是對什么信號進行傳輸的

FPGA 實驗一:流水燈模塊

數字電路中的亞穩態是什么

【紫光同創盤古PGX-Nano教程】——(盤古PGX-Nano開發板/PG2L50H_MBG324第三章)鍵控流水燈實驗例程

數字電路和模擬電路的區別與聯系

數字電路仿真元件符號是什么

【紫光同創盤古PGX-MINI-4K教程】——(盤古PGX-MINI-4K開發板/PGC4KD-6ILPG144第二章)LED 流水燈實驗例程

【紫光同創盤古PGX-Lite 7K教程】——(盤古PGX-Lite 7K開發板/PGC7KD-6IMBG256第二章)?LED 流水燈實驗例程

51單片機流水燈制作

詳解基于FPGA的數字電路對流水燈的實驗

詳解基于FPGA的數字電路對流水燈的實驗

評論