數(shù)字電路是一種電子系統(tǒng),它使用數(shù)字信號(hào)進(jìn)行信息傳輸和處理。數(shù)字信號(hào)是由離散的電壓水平或電流水平表示的信號(hào),通常用二進(jìn)制代碼表示。與模擬電路不同,數(shù)字電路在處理信號(hào)時(shí)不涉及連續(xù)的信號(hào)變化,而是使用離散的邏輯電平。

在現(xiàn)代電子技術(shù)中,數(shù)字電路扮演著至關(guān)重要的角色。從計(jì)算機(jī)、智能手機(jī)到家用電器,數(shù)字電路無處不在。

數(shù)字電路的基本原理

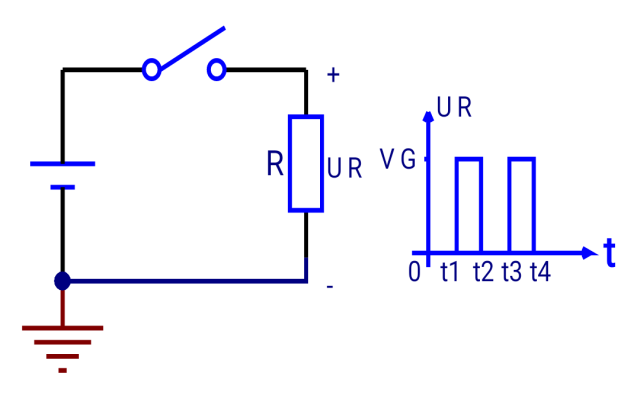

1. 數(shù)字信號(hào)與模擬信號(hào)

數(shù)字信號(hào)是一種離散的信號(hào),它由一系列離散的電壓或電流水平組成。這些電壓或電流水平通常表示為二進(jìn)制數(shù)字,即0和1。與之相對(duì)的是模擬信號(hào),它是一種連續(xù)變化的信號(hào),可以表示為時(shí)間的函數(shù)。

2. 數(shù)字邏輯

數(shù)字邏輯是數(shù)字電路的基礎(chǔ),它使用布爾代數(shù)來描述和實(shí)現(xiàn)邏輯運(yùn)算。布爾代數(shù)是一種數(shù)學(xué)方法,用于描述邏輯關(guān)系和邏輯運(yùn)算,如AND、OR、NOT等。

3. 數(shù)字電路的組成

數(shù)字電路主要由以下幾部分組成:

- 邏輯門:實(shí)現(xiàn)基本邏輯運(yùn)算的電路,如與門、或門、非門等。

- 觸發(fā)器:存儲(chǔ)一位二進(jìn)制信息的電路,如D觸發(fā)器、JK觸發(fā)器等。

- 寄存器:存儲(chǔ)多位二進(jìn)制信息的電路,通常由多個(gè)觸發(fā)器組成。

- 計(jì)數(shù)器:用于實(shí)現(xiàn)數(shù)字計(jì)數(shù)功能的電路,如二進(jìn)制計(jì)數(shù)器、十進(jìn)制計(jì)數(shù)器等。

- 存儲(chǔ)器:用于存儲(chǔ)大量數(shù)據(jù)的電路,如隨機(jī)存取存儲(chǔ)器(RAM)和只讀存儲(chǔ)器(ROM)。

數(shù)字電路的關(guān)鍵組件

1. 邏輯門

邏輯門是數(shù)字電路中最基本的組件,它可以實(shí)現(xiàn)基本的邏輯運(yùn)算。常見的邏輯門有:

- 與門(AND):只有當(dāng)所有輸入都為1時(shí),輸出才為1。

- 或門(OR):只要有一個(gè)輸入為1,輸出就為1。

- 非門(NOT):輸出是輸入的反。

- 異或門(XOR):當(dāng)輸入不相等時(shí),輸出為1;相等時(shí),輸出為0。

- 同或門(XNOR):當(dāng)輸入相等時(shí),輸出為1;不相等時(shí),輸出為0。

2. 觸發(fā)器

觸發(fā)器是一種存儲(chǔ)一位二進(jìn)制信息的電路。常見的觸發(fā)器有:

- D觸發(fā)器:根據(jù)輸入信號(hào)D的值,存儲(chǔ)一位二進(jìn)制信息。

- JK觸發(fā)器:根據(jù)輸入信號(hào)J和K的組合,實(shí)現(xiàn)置位、復(fù)位、保持和翻轉(zhuǎn)功能。

- T觸發(fā)器:根據(jù)輸入信號(hào)T的值,實(shí)現(xiàn)翻轉(zhuǎn)功能。

3. 寄存器

寄存器是一種存儲(chǔ)多位二進(jìn)制信息的電路,通常由多個(gè)觸發(fā)器組成。寄存器可以用于實(shí)現(xiàn)數(shù)據(jù)的暫存、移位等功能。

4. 計(jì)數(shù)器

計(jì)數(shù)器是一種用于實(shí)現(xiàn)數(shù)字計(jì)數(shù)功能的電路。常見的計(jì)數(shù)器有:

- 二進(jìn)制計(jì)數(shù)器:按照二進(jìn)制遞增的方式進(jìn)行計(jì)數(shù)。

- 十進(jìn)制計(jì)數(shù)器:按照十進(jìn)制遞增的方式進(jìn)行計(jì)數(shù)。

5. 存儲(chǔ)器

存儲(chǔ)器是一種用于存儲(chǔ)大量數(shù)據(jù)的電路,常見的存儲(chǔ)器有:

- 隨機(jī)存取存儲(chǔ)器(RAM):可以隨機(jī)訪問存儲(chǔ)器中的任何位置。

- 只讀存儲(chǔ)器(ROM):存儲(chǔ)器中的數(shù)據(jù)在制造過程中寫入,用戶無法修改。

數(shù)字電路的設(shè)計(jì)方法

1. 硬件描述語言(HDL)

硬件描述語言是一種用于描述和設(shè)計(jì)數(shù)字電路的語言,如VHDL和Verilog。HDL可以用于描述電路的行為、結(jié)構(gòu)和時(shí)序特性。

2. 邏輯仿真

邏輯仿真是一種在計(jì)算機(jī)上模擬數(shù)字電路行為的方法。通過仿真,設(shè)計(jì)師可以在實(shí)際制造電路之前,檢查電路的功能和性能。

3. 綜合與優(yōu)化

綜合是將高級(jí)描述(如HDL代碼)轉(zhuǎn)換為低級(jí)描述(如邏輯門或觸發(fā)器)的過程。優(yōu)化是在綜合過程中對(duì)電路進(jìn)行改進(jìn),以提高性能、降低成本或減小功耗。

-

電子系統(tǒng)

+關(guān)注

關(guān)注

0文章

450瀏覽量

31423 -

數(shù)字信號(hào)

+關(guān)注

關(guān)注

2文章

987瀏覽量

48003 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1635瀏覽量

81321 -

信息傳輸

+關(guān)注

關(guān)注

1文章

42瀏覽量

9509

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速數(shù)字電路的仿真

數(shù)字電路的基礎(chǔ)知識(shí)

最通用的數(shù)字電路

模擬和數(shù)字電路基礎(chǔ)知識(shí)匯總

如何對(duì)高速數(shù)字電路進(jìn)行仿真測(cè)試?

高速數(shù)字電路信號(hào)完整性分析與設(shè)計(jì)

高速數(shù)字電路設(shè)計(jì)

模擬電路與數(shù)字電路的區(qū)別詳解

數(shù)字電路是對(duì)什么信號(hào)進(jìn)行傳輸?shù)?/h1>

數(shù)字電路是對(duì)什么信號(hào)進(jìn)行傳輸?shù)?/h1>

評(píng)論