作者:zgezi

一、SoC設計的特點

一個完整的SoC設計包括系統結構設計(也稱為架構設計),軟件結構設計和ASIC設計(硬件設計)。

SoC設計與傳統的ASIC設計最大的不同在于以下兩方面:

SoC設計更需要了解整個系統的應用,定義出合理的芯片架構,使得軟硬件配合達到系統最佳工作狀態。因而,軟硬件協同設計被越來越多地采用。

SoC設計是以IP復用或更大的平臺復用為基礎的。因而,基于IP 復用的設計是硬件實現的特點。

二、軟硬件協同設計流程

SoC(System on Chip)通常被稱作系統及芯片或者片上系統,作為一個完整的系統,其包含了硬件和軟件兩部分內容。這里硬件指SoC芯片部分,軟件指運行在SoC芯片上的系統及應用程序。所在在進行設計時需要同時從軟件和硬件的角度去考慮。

傳統的設計中,設計工程師很難對結構在系統層次上進行詳細評估,隨著設計的細節化,要改變系統架構變得更加困難。此外,由于仿真速度的限制,軟件開發難以在這種詳細的硬件平臺上進行,所以采用傳統的設計流程進行SoC設計可能會存在產品設計周期長,芯片設計完成后發現系統架構存在問題等。

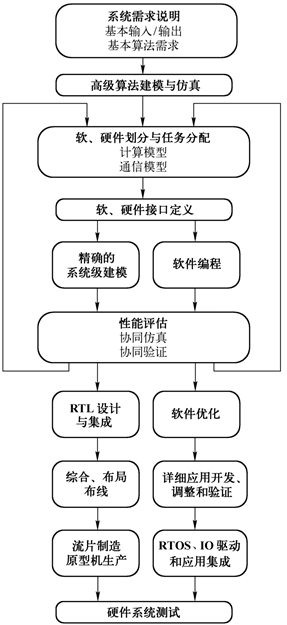

軟硬件協同設計指的是軟硬件的設計同步進行,如下圖所示,在系統定義的初始階段兩者就緊密相連,近年來,由于電子系統級設計(ESL Electronic System Leverl Design)工具的發展,軟硬件協同設計逐漸被采用。這種方法使得軟件設計者在硬件設計完成之前就可以獲得軟件開發的虛擬硬件平臺,在虛擬平臺上開發應用軟件,評估系統架構設計。

2.1 系統需求說明

系統設計首先從確定所需的功能開始,包含系統基本輸入和輸出及基本算法需求,以及系統要求的功能、性能、功耗、成本和開發時間等。在這一階段,通常會將用戶的需求轉換為用于設計的技術文檔,并初步確定系統的設計流程。

2.2 高級算法建模與仿真

設計者將使用如C和C++等高級語言創建整個系統的高級算法模型和仿真模型。目前,一些EDA工具可以幫助我們完成這一步驟。有了高級算法模型,便可以得到軟硬件協同仿真所需的可執行的說明文檔。此類文檔會隨著設計進程的深入而不斷地完善和細化。

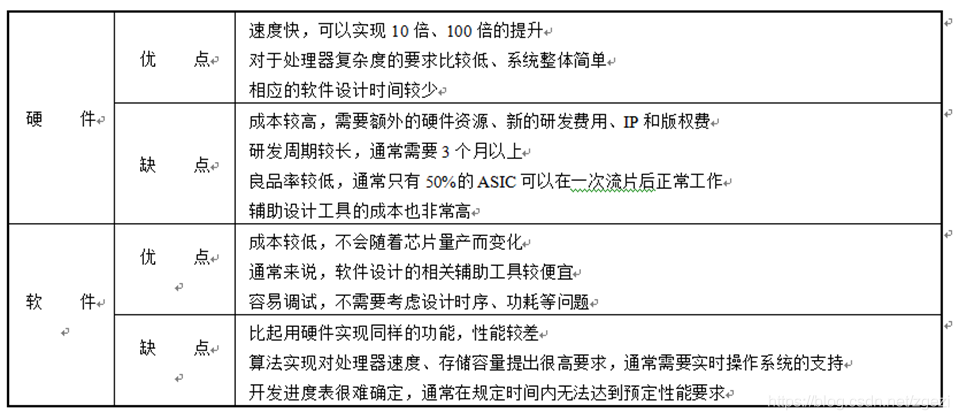

2.3 軟硬件劃分過程

設計者通過軟硬件劃分來決定哪些功能應該由硬件完成,哪些功能應該由軟件來實現。這是一個需要反復評估-修改直至滿足系統需求的過程。

2.4 軟硬件同步設計

由于軟硬件的分工已明確,芯片的架構及同軟件的接口也已定義,接下來便可以進行軟硬件的同步設計了。其中硬件設計包括RTL設計和集成、綜合、布局布線及最后的流片。軟件設計則包括算法優化、應用開發,以及操作系統、接口驅動和應用軟件的開發。

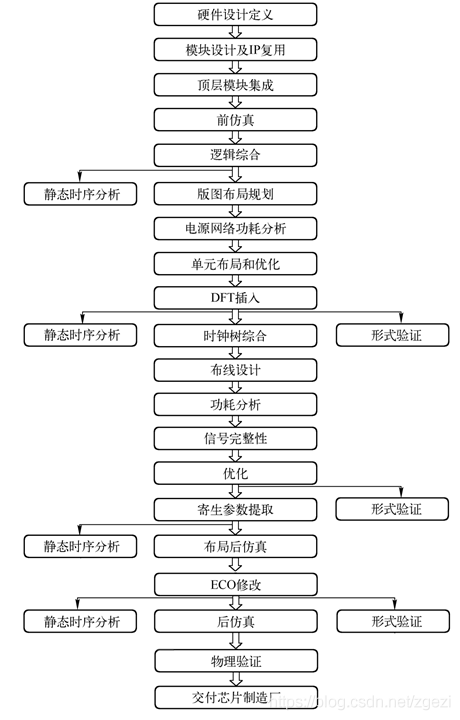

三、基于標準單元的SoC芯片設計流程

硬件設計定義說明(Hardware Design Specification)

? 硬件設計定義說明描述芯片總體結構、規格參數、模塊劃分、使用的總線,以及各個模塊的詳細定義等。

模塊設計及IP復用(Module Design & IP Reuse)

? 對于需要重新設計的模塊進行設計;對于可復用的IP核,通常由于總線接口標準不一致需要做一定的修改。

頂層模塊集成(Top Level Integration)

? 頂層模塊集成是將各個不同的功能模塊,包括新設計的與復用的整合在一起,形成一個完整的設計。通常采用硬件描述語言對電路進行描述,其中需要考慮系統時鐘/復位、I/O環等問題。

前仿真(Pre-layout Simulation)

? 前仿真也叫RTL級仿真。通過HDL仿真器驗證電路邏輯功能是否有效。在前仿真時,通常與具體的電路物理實現無關,沒有時序信息。

邏輯綜合(Logic Synthesis)

? 邏輯綜合是指使用EDA工具把由硬件描述語言設計的電路自動轉換成特定工藝下的網表,即從RTL級的HDL描述通過編譯與優化產生符合約束條件的門級網表。

版圖布局規劃(Floorplan)

? 版圖布局規劃完成的任務是確定設計中各個模塊在版圖上的位置,主要包括:

I/O規劃,確定I/O的位置,定義電源和接地口的位置;

模塊放置,定義各種物理的組、區域或模塊,對這些大的宏單元進行放置;

供電設計,設計整個版圖的供電網絡,基于電壓降(IR Drop)和電遷移進行拓撲優化。

功耗分析(Power Analysis)

? 在設計中的許多步驟都需要對芯片功耗進行分析,從而決定是否需要對設計進行改進。

? 在版圖布局規劃后,需要對電源網絡進行功耗分析(PNA,Power Network Analysis),確定電源引腳的位置和電源線寬度。

? 在完成布局布線后,需要對整個版圖的布局進行動態功耗分析和靜態功耗分析。

? 除了對版圖進行功耗分析以外,還應通過仿真工具快速計算動態功耗,找出主要的功耗模塊或單元。

單元布局和優化(Placement & Optimization)

? 單元布局和優化主要定義每個標準單元的擺放位置并根據擺放的位置進行優化。

靜態時序分析(STA,Static Timing Analysis)

? STA是一種靜態驗證方法

? 通過對提取電路中所有路徑上的延遲等信息的分析,計算出信號在時序路徑上的延遲,找出違背時序約束的錯誤,如檢查建立時間(Setup Time)和保持時間(Hold Time)是否滿足要求。

形式驗證(Formal Verification)

? 形式驗證也是一種靜態驗證方法。

? 在整個設計流程中會多次引入形式驗證用于比較RTL代碼之間、門級網表與RTL代碼之間,以及門級網表之間在修改之前與修改之后功能的一致性。

可測性電路插入(DFT,Design for Test)

? 可測性設計是SoC設計中的重要一步。通常,對于邏輯電路采用掃描鏈的可測試結構,對于芯片的輸入/輸出端口采用邊界掃描的可測試結構。基本思想是通過插入掃描鏈,增加電路內部節點的可控性和可觀測性,以達到提高測試效率的目的。一般在邏輯綜合或物理綜合后進行掃描電路的插入和優化。

時鐘樹綜合(Clock Tree Synthesis)

? SoC設計方法強調同步電路的設計,即所有的寄存器或一組寄存器是由同一個時鐘的同一個邊沿驅動的。構造芯片內部全局或局部平衡的時鐘鏈的過程稱為時鐘樹綜合。分布在芯片內部寄存器與時鐘的驅動電路構成了一種樹狀結構,這種結構稱為時鐘樹。時鐘樹綜合是在布線設計之前進行的。

布線設計(Routing)

? 這一階段完成所有節點的連接。

寄生參數提取(Parasitic Extraction)

? 通過提取版圖上內部互連所產生的寄生電阻和電容值,進而得到版圖實現后的真實時序信息。

? 這些寄宿生電路信息將用于做靜態時序分析和后仿真。

后仿真(Post-layout Simulation)

? 后仿真也叫門級仿真、時序仿真、帶反標的仿真,需要利用在布局布線后獲得的精確延遲參數和網表進行仿真,驗證網表的功能和時序是否正確。后仿真一般使用標準延時(SDF,Standard Delay Format)文件來輸入延時信息。

ECO修改(ECO,Engineering Change Order)

? ECO修改是工程修改命令的意思。

? 這一步實際上是正常設計流程的一個例外。當在設計的最后階段發現個別路徑有時序問題或邏輯錯誤時,有必要通過ECO對設計的局部進行小范圍的修改和重新布線,并不影響芯片其余部分的布局布線。在大規模的IC設計中,ECO修改是一種有效、省時的方法,通常會被采用。

物理驗證(Physical Verification)

? 物理驗證是對版圖的設計規則檢查(DRC,Design Rule Check)及邏輯圖網表和版圖網表比較(LVS,Layout Vs. Schematic)。

? DRC用以保證制造良率。

? LVS用以確認電路版圖網表結構是否與其原始電路原理圖(網表)一致。

來源:電子創新網

審核編輯黃昊宇

-

soc

+關注

關注

38文章

4177瀏覽量

218464 -

設計

+關注

關注

4文章

818瀏覽量

69911

發布評論請先 登錄

相關推薦

Vivado之實現布局布線流程介紹

數字設計ic芯片流程

芯片設計進階之SOC電源管理系統介紹

soc開發流程常見問題及解決方案

SOC芯片在汽車電子中的應用

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

簡單介紹SoC設計流程

簡單介紹SoC設計流程

評論