超大規模集成電路設計進入到深亞微米工藝后,以時序驅動為主的開發方法使用更加普遍,面臨的新挑戰也隨之而來:為了可制造性而要面臨越來越多的金屬層密度問題和天線效應問題,同時面積減小了,但由于連線延時效應影響,給布局布線帶來了困難,以至于不得不根據布線后時序的結果回過頭重新調整時序約束以保證后面布線后滿足時序要求。這使得整個后端的時間進度壓力加大,尤其對物理驗證而言,作為后端設計人員將設計交給代工廠家前的最后一道程序,時間被壓縮的很緊。因此有必要提出一套成熟的物理驗證方法,來加快物理驗證的速度,為加快芯片研發速度,盡快進入市場贏得時間。

1 物理驗證及工具簡述

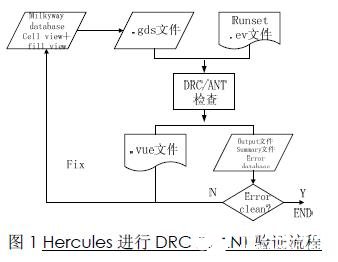

傳統的物理驗證主要包括設計規則檢查(DRC),天線效應檢查(ANT),版圖一致性驗證(LVS)和電氣規則檢查(ERC)四部分,本課題使用的工具是Synopsys公司的版圖工具Astro和物理驗證工具Hercules。Hercules擁有進行超深亞微米(UDSM)工藝驗證的能力,可進行億門級的微處理器和千萬門級的ASIC的物理驗證。通過更加高效的驗證來縮短設計周期,并提供圖形界面來幫助設計人員快速發現和改正違例錯誤。它可以和Synopsys公司的milkyway數據進行無縫連接,設計人員使用milkyway數據進行布局布線和版圖優化。Milkyway是Astro工具的版圖格式,它的設計單元稱為cell,含有多種視圖 (View),其中與物理驗證關系密切的是CEL View和FILL View,CEL View含有實現邏輯功能的版圖信息,FILL View含有進行可制造性設計(Design for Manufacturing,DFM)時插入的填充金屬(metal filler)信息。本處的DFM是指對布線結束后的設計為了滿足工藝制造性要求,根據天線效應規則、密度設計規則等進行的插入二極管,添加填充金屬,放人fill單元等操作的總稱。其中添加metal filler是為了滿足覆蓋密度要求而添加冗余的多晶硅或金屬,結果是生成了對應cell的FILLView。FILL View在修復DRC錯誤及ANT錯誤后要及時進行調整,不然又會引入新的DRC問題。Astro進行物理驗證時支持Hercules explorer和vue兩種圖形化界面工具,本課題使用的是vue界面,來對hercules發現的問題進行定位和修復。在腳本設置文件 (runset)文件中設定OPTIONS {CRE-ATE_VUE_OUTPUT=TRUE}生成.vue文件,在Astro中啟動Hercules然后借助.vue文件就可以借助錯誤定位進行修改了。

在Hercules工具進行物理驗證之前,可以使用Astro工具進行后端驗證,先行檢查Milkyway文件中存在的DRC和LVS錯誤并更正。Astro支持深亞微米工藝下在工藝文件中進行了定義的設計規則檢查,使用命令geAdvDRC或者geNewDRC可以調用這一功能,工具會生成錯誤單元位置信息,在上面會標出可能出現問題的區域,便于更正。使用命令geNewLVS可以進行簡單的LVS檢查---連接性檢查,可以發現版圖中的斷路或開路問題,同樣也會生成一個錯誤單元位置信息方便改正。

2 物理驗證組成

DRC,即設計規則驗證,它要求設計的版圖文件要滿足多邊形最小面積,同層以及不同層間多邊形內部最小間距,外部最小間距,以及為了確保可制造性而進行的密度檢查等。在物理驗證階段,為了消除DRC錯誤而進行手工改動時常常會引入新的錯誤。尤其是經過DFM后的設計,填充金屬的引入會增加最小間距或最小面積等類型的錯誤,這些因金屬填充產生的錯誤可在最后集中在FILL View中改完。

ANT是天線效應檢查,這也是和電路制造過程有關的問題,為了防止太多的電子在鋪金屬層的過程中集中到導線上擊穿柵極,必須保證同層的導線長度不能太長。解決天線效應問題有兩種方法,一是在產生天線效應的走線上添加反向二極管,這樣可以保護柵極;二是采用向更高層的金屬進行跳線連接,這樣在加工過程中就可以避免過多電子的積聚。在可制造性工藝之前,由于版圖中沒有加入填充用的金屬,可以用第一種方法來加入二極管以消除天線效應,但在DFM之后的物理驗證部分,已經很難再找到空閑的空間插人二極管,這時就應該使用第二種方法來解決天線效應問題。

就流程而言,DRC檢查和ANT檢查有相似之處,如圖1所示。在使用Astro進行流文件輸出得到CDSII文件后,根據實際設計的頂層模塊名稱和路徑,對代工廠家提供的基于Hercules的DRC規則設置文件進行改動,如下例:

Header部分下面是檢查時候一些選項的設置,還有層的定義以及規則的描述。設置好之后就可以運行He rcules進行DRC或ANT驗證了。如果使用了正確的runset文件,得到的DRC錯誤一般是圖形間距錯誤、寬金屬間距錯誤,金屬密度錯誤等,而ANT錯誤也會給出具體發生問題的走線名稱,這樣再在Astro里調用vue圖形界面進行改錯即可。

LVS是版圖原理圖一致性驗證,用于比較兩者晶體管級的連接是否正確,邏輯功能是否一致,其過程分兩步:第一步,Hercules讀入版圖文件,從包含有器件及其相互間的連通性的版圖數據庫中提取出版圖網表;第二步,Hercules讀入版圖網表和原理圖網表,然后對照這兩個網表的連接情況以確定它們是否一致。對照時,Hercules從電路的輸入輸出開始搜索,找到一個匹配節點后就給該匹配節點和器件賦以匹配狀態值,當遇到不匹配的節點時,就停止該路徑的搜索,直到所有的路徑都搜索完畢,Her-cules將節點和器件的匹配結果寫入輸出文件,給出連接及匹配情況的報告,設計人員可以根據報告來改正不匹配的元件,LVS驗證流程如圖4所示。

進行LVS驗證的設置較為復雜,除了與DRC類似的對foundry提供的runset文件進行設置外,還要提取verilog網表,進行網表轉換(netTran)得到Hercules格式網表和對等文件(Equivalence File)。對等文件可以簡化比較過程,比如文件中指定equiv dpram_8xlk=dpram_8xlk{}

Hercules在LVS比較的時候就直接比較用戶指定的這些單元的版圖和電路圖的匹配性,而不比較其他的模塊。運行Hercules生成結果后,查看結果文件并結合Astro進行改正。

3 物理驗證流程

一般而言LVS與電氣規則檢查(ERC)的關系密切,ERC主要包括比如短路、開路、懸浮等,對于一個ERC檢查通過的設計,LVS才真正可以檢查出元件的連接問題。因此,ERC應該在LVS之前完成,需要注意的是Hercules的ERC檢查可以集成在DRC和LVS檢查中,以利于整體進行檢查和改進。本課題所采用Smic18LG工藝的物理驗證將ERC檢查分別集成到天線效應檢查和LVS的電氣連接檢查中。但一般而言,DRC,ANT與LNS則沒有必然的先后順序。根據工程經驗,在修復ANT錯誤時,常常需要更改填充金屬形狀和位置,而這又會帶入新的DRC問題,因此比較理想的做法是先修ANT錯誤,等檢查通過后再進行DRC修復前面引入的設計規則違例,這樣不但可以修復 DRC,而且可以為后面進行LNS盡可能的排除干擾,然后進行LVS,需要注意的是,LVS不涉及FILL View,即含有填充金屬信息的版圖層,而進行LVS時在提取版圖參數階段,如果含有填充金屬信息會導致提取的參數文件過大,一致性比較時也會占用較多內存,因此可以使用不含FILL View信息的CDSII版圖文件進行LVS初步檢查,經比較并修改至檢查通過時再使用含填充金屬信息的GDSII文件提取參數并作最后的LVS,這時的結果會與前面類似,如果檢查通過則可作最后的DRC檢查,若結果顯示沒有違例則可進行最后的流片。物理驗證流程如圖5所示。

4 結論

本課題使用的服務器是浪潮服務器NL380G2,3.6G雙核CPU,Xeon8G內存,進行驗證的設計為二百萬門級某型號調制芯片設計,工具為Her-cules2004.12。舊有的流程是按經驗采用或先LVS或先DRC,而按照本文提出的流程在實際的設計中已經經過驗證。

-

電路圖

+關注

關注

10349文章

10721瀏覽量

531413 -

天線

+關注

關注

68文章

3206瀏覽量

140903 -

晶體管

+關注

關注

77文章

9706瀏覽量

138494

發布評論請先 登錄

相關推薦

SoC驗證平臺的FPGA綜合怎么實現?

深亞微米集成電路靜態功耗的優化

一種基于省時考慮的深亞微米VLSI的物理驗證方法

深亞微米下ASIC后端設計及實例

基于深亞微米MOS器件溝道的熱噪聲淺析

超深亞微米IC設計中的天線效應

一種增強超深亞微米集成電路測試質量和抑制測試代價增長趨勢的可

一種全新的深亞微米IC設計方法

TSMC推出最新深亞微米互通式EDA格式

深亞微米CMOS IC全芯片ESD保護技術

深亞微米pMOS器件的HCI和NBTI耦合效應與物理機制

基于深亞微米VLSI的物理驗證可實現加快芯片研發速度

基于深亞微米VLSI的物理驗證可實現加快芯片研發速度

評論