GAL(Generic Array Logic, GAL,通用數組邏輯)以PAL(可編程數組邏輯,PLD的一種)為基礎,此是由萊迪思半導體公司所發明,GAL的特性與PAL相同,不過PAL的電路配置、配置只能進行一次的程序刻錄,不能再有第二次,而GAL則可反復對電路配置、配置進行刻錄、清除、再刻錄、再清除。

這種可重復刻錄的特性,讓GAL在研發過程時的試制階段(prototyping stage)特別好用,一旦在邏輯電路的設計上發現有任何程序錯誤,若是用GAL就能以重新刻錄的方式來修正錯誤。 此外,GAL也可以用PAL的刻錄器來進行刻錄及再刻錄。 還有PEEL(Programmable Electrically Erasable Logic),與GAL類似,PEEL由International CMOS Technology公司提出。 CPLD

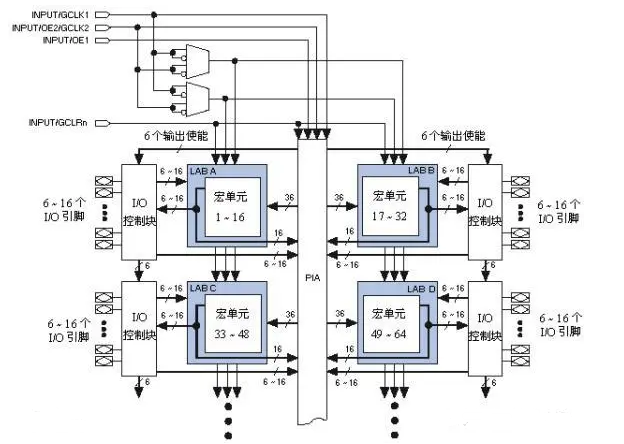

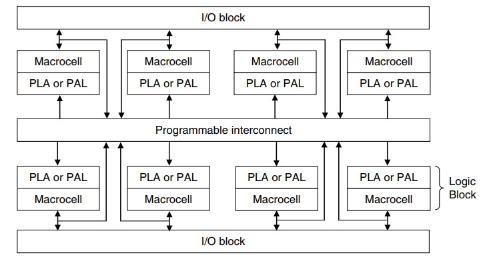

PAL、GAL僅適合用在約數百個邏輯門所構成的小型電路,若要實現更大的電路,則適合用CPLD(Complex PLD,復雜型PLD),一顆CPLD內等于包含了數顆的PAL,各PAL(邏輯區塊)間的互接連線也可以進行程序性的規劃、刻錄,運用這種多合一(All-In-One)的集成作法,使一顆CPLD就能實現數千個,甚至數十萬個邏輯門才能構成的電路。 有些CPLD可以用PAL的刻錄器來進行刻錄,但這種刻錄方式對經常有數百只接腳的CPLD來說并不方便。

另一種刻錄方式是CPLD已焊于印刷電路板上,之后透過額外的臨時外接,或原有線路的內接,使CPLD與個人電腦間能獲取連線,由個人電腦以串列或并行方式將新的刻錄資料發送到CPLD上,而CPLD內部也具有解碼電路能對接收到的資料進行還原解析,之后再進行重新的刻錄,以此方式讓CPLD內的程序獲得更新。 FPGA

FPGA(Field Programmable Gate Array,FPGA),場式可編程閘數組或現場可編程閘數組,是以閘數組(Gate Array)技術為基礎所發展成的一種PLD。 FPGA運用一種邏輯門式的網格(Grid),這種網格與普通的「閘數組」相類似,網格可以在FPGA芯片出廠后才進行配置配置的程序性規劃。 FPGA通常也可以在焊接后再進行程序刻錄、變更的工作,這某種程度上與大型的CPLD相似。

絕大多數的FPGA,其內部的程序配置配置是易失性的,所以在設備重新獲得電力后,就必須將配置配置內容重新加載(re-load)到FPGA中,或者期望改變FPGA內的配置配置時,也必須進行重新加載的動作。 FPGA與CPLD都很適合用在特殊、特定的工作上,這是以此類芯片的技術本質來做為合適性的考量,然而有時在以經濟性為主的權衡評估下也適合使用FPGA、CPLD,或者有時也會以工程師的個人偏好與經驗來決定。

責任編輯:xj

原文標題:三類主要的可編程邏輯器件

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605129 -

pal

+關注

關注

1文章

43瀏覽量

27301 -

gal

+關注

關注

0文章

24瀏覽量

20277 -

可編程邏輯器件

+關注

關注

5文章

144瀏覽量

30333

原文標題:三類主要的可編程邏輯器件

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

德州儀器推出全新可編程邏輯產品系列

什么是現場可編程邏輯陣列?它有哪些特點和應用?

FPGA零基礎學習系列精選:半導體存儲器和可編程邏輯器件簡介

可編程片上系統的基本特征和主要應用

可編程片上系統是什么

現場可編程門陣列的基本結構和優缺點

現場可編程門陣列是什么

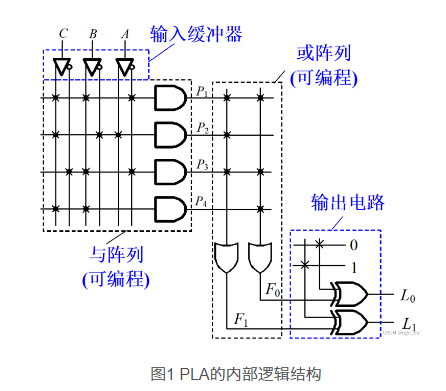

可編程邏輯陣列PLA內部邏輯結構示意

三類主要的可編程邏輯器件簡介

三類主要的可編程邏輯器件簡介

評論