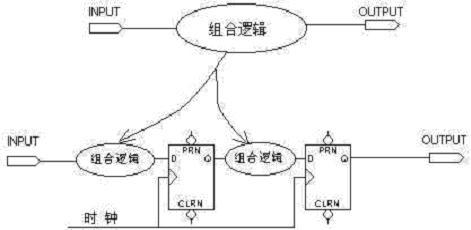

組合邏輯生成的時鐘,在FPGA設計中應該避免,尤其是該時鐘扇出很大或者時鐘頻率較高,即便是該時鐘通過BUFG進入全局時鐘網絡。

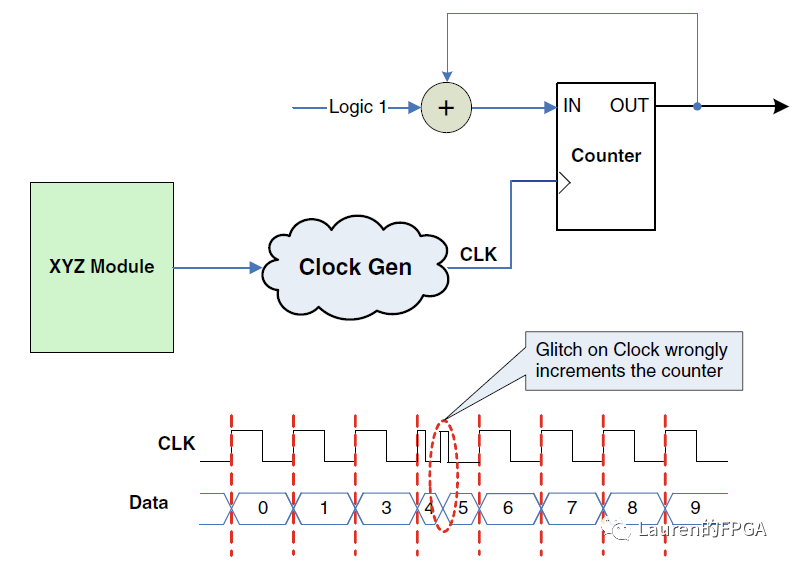

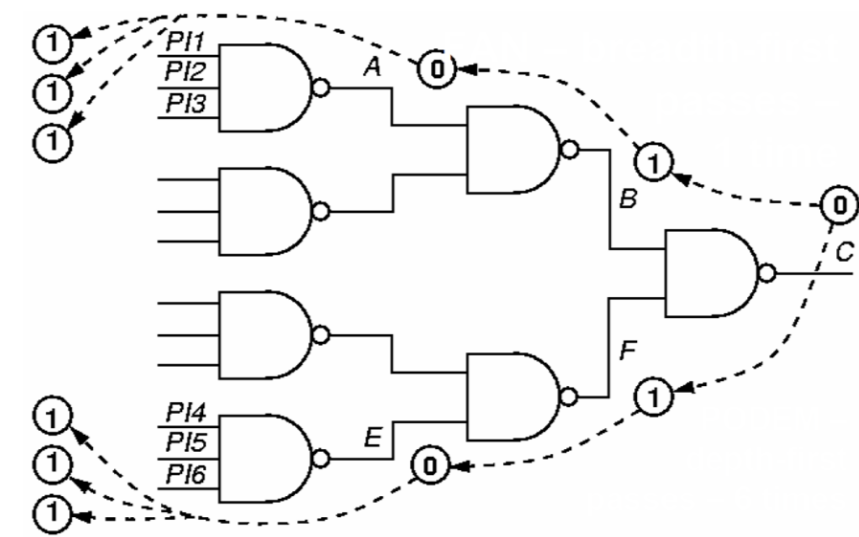

組合邏輯生成時鐘的典型特征是在網表中我們能夠看到LUT(查找表)的輸出直接連接或通過BUFG連接到時序邏輯單元比如觸發器的時鐘端口。最直接的危害是組合邏輯可能會產生毛刺(Glitch),從而導致電路功能錯誤。看個案例,如下圖所示。由于毛刺的存在,計數器多計數了一次,導致錯誤。

從時序角度而言,組合邏輯生成的時鐘會增加時鐘線上的延遲,從而導致過大的Clock Skew,最終造成建立時間和保持時間違例。此外,如果有毛刺,毛刺通常很窄,很可能無法滿足觸發器的Pulse Width要求。還有的工程中盡管沒有直接把LUT的輸出當作時鐘,而是將其通過一個觸發器之后再用作時鐘,這可以過濾掉毛刺,但同樣會增加時鐘線上的延遲,導致Clock Skew過大。因此,在FPGA設計中,要避免此類時鐘。

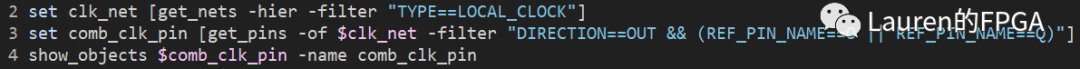

拿到一個網表,如何判定設計中是否包含此類時鐘呢?從上面的描述可以看到,這類時鐘要么是LUT輸出,要么是觸發器輸出,這是第一個特征。第二個特殊,既然是時鐘,時鐘網線的類型就是LOCAL_CLOCK,根據這兩點就能找到時鐘管腳,相應的Tcl腳本如下圖所示。

代碼第2行是找到所有的時鐘網線,第3行對該時鐘網線進行過濾篩選,凡是與網線相連的pin是輸出端口且其REF_PIN_NAME是O(對應LUT輸出)或Q(對應觸發器輸出)的,即為目標時鐘端口。代碼第4行則是將找到的對象以圖形界面方式顯示出來。

找到了這類時鐘,如何優化呢?如果這類時鐘是在MMCM或PLL可生成頻率范圍內,那么建議用MMCM或PLL生成,尤其是該時鐘扇出比較大的時候。如果MMCM或PLL無法生成,且時鐘頻率很低,例如低于5MHz,而設計已經到了后期,不太可能大范圍修改,那么嘗試是否可能將該時鐘驅動的邏輯都放在一個時鐘區域內,同時保證時鐘源也在該時鐘區域內,這可通過手工布局的方式(畫Pblock)實現。這樣做對于降低Clock Skew會有些幫助。

責任編輯人:CC

-

時鐘

+關注

關注

11文章

1746瀏覽量

131673 -

組合邏輯

+關注

關注

0文章

47瀏覽量

10059

原文標題:如何快速找到組合邏輯生成的時鐘

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

組合邏輯消除競爭

勇敢的芯伴你玩轉Altera FPGA連載25:組合邏輯與時序邏輯

【技巧分享】時序邏輯和組合邏輯的區別和使用

在FPGA中何時用組合邏輯或時序邏輯

組合邏輯電路的分析與設計-邏輯代數

實現拆分大組合邏輯的方法

組合邏輯電路和時序邏輯電路比較_組合邏輯電路和時序邏輯電路有什么區別

組合邏輯自動測試生成的PDF文件免費下載

組合邏輯生成的時鐘有哪些危害

組合邏輯生成的時鐘有哪些危害

評論