高速度的DAC運用的非常多,為了達到高速數/模轉換器(DAC)的最佳性能,需要嚴格滿足數字信號的時序要求。隨著時鐘頻率的提高,數字接口的建立和保持時間成為系統設計人員需要重點關注的參數。此文對建立和保持時間進行詳盡說明,因為這些參數與Maxim的高性能數據轉換方案密切相關。

建立和保持時間

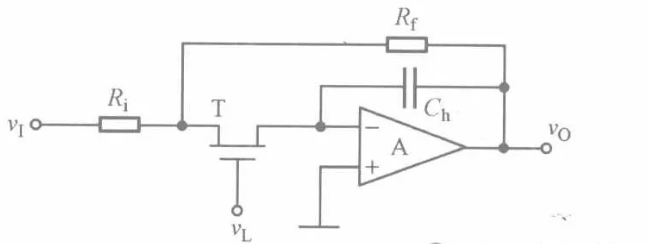

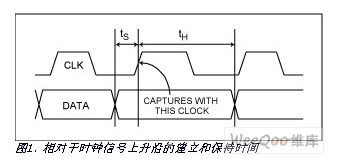

數模轉換器,又稱D/A轉換器,簡稱DAC,它是把數字量轉變成模擬的器件。D/A轉換器基本上由4個部分組成,即權電阻網絡、運算放大器、基準電源和模擬開關。建立時間(tS)是相對于DAC時鐘跳變,數據必須達到有效的邏輯電平的時間。保持時間(tH)則定義了器件捕獲/采樣數據后允許數據發生變化的時間。DAC在“down”轉換過程中,傳統電容陣列中需要有兩個電容進行切換,而控制電容轉換的開關在轉換過程中的任何不匹配,無論是隨機的還是確定的,都可以引起電容陣列向錯誤的方向進行轉換,甚至引起前置放大器的過載。而分割電容陣列在每一位的比較過程中,只有一個電容變化時,對開關信號的歪斜有很好的抵制作用。當分割電容陣列和傳統陣列開關時間的寬度相同時,分割電容陣列的建立時間比傳統陣列的建立時間快了8%左右,而且電容值越大,建立時間縮小的越明顯。特定器件的時鐘信號有效邊沿可能是上升/下降沿,或由用戶選擇, 500Msps、插值和調制雙通道DAC,CMOS輸入。

采用CMOS技術設計的數字電路通常將電源擺幅的中間值作為切換點。因此,時間參考點定在信號邊沿的中點。注意此時定義的這兩個參數均為正值,但在建立或保持時間出現負值時將會令人迷惑不解。為滿足這些是需要求,用戶需要分析數據源的傳輸延遲和抖動。傳輸延遲決定了時鐘的標稱定時要求,而抖動指標則決定了所允許的容限。為了解釋這一關系,我們以具有1.5ns傳輸延遲的邏輯門電路為例。如果在邏輯門電路作用相同的時鐘信號,這種情況下,對于溫度漂移、時鐘或數據抖動以及器件之間存在的差異都不具備任何設計裕量。

可以采用兩種方法對建立和保持時間進行優化,包括增加時鐘延遲、保持一致的引線長度等。在數據源和DAC之間增加時鐘延遲有助于解決上述例子中的傳輸延遲問題。保持一致的數據源與DAC輸入引腳之間的引線長度可以確保抖動、漂移不會使某一位進入下一個時鐘周期。需要注意的是,我們現在處理的是包含多條數據線的高速數據總線,任何時刻所有位都必須滿足時序要求。

處理高頻數據的定時面臨諸多挑戰,解決這些難題需要設計人員或系統設計工程師充分理解具體信號鏈路中所有器件的規格。如果鏈路中任一器件的規格要求得不到滿足,系統性能將會降低。性能的降低表現為DAC輸出精度的下降或限制時鐘頻率。

審核編輯 黃昊宇

-

轉換器

+關注

關注

27文章

8741瀏覽量

147706

發布評論請先 登錄

相關推薦

D/A轉換器什么是轉換器?

如何選擇RS232轉換器?RS232與RS485區別

ADC采樣保持電路的工作原理和技術指標

將模擬量轉換為數字量,采用什么轉換器

D/A轉換器的基本原理和性能指標

模數轉換器的性能指標

高速數模轉換器(DAC)的建立和保持時間

高速數/模轉換器的指標選擇之建立保持時間

高速數/模轉換器的指標選擇之建立保持時間

評論