01 案例重點

通過部署在線電氣測試,測量和分析,減少晶圓損失和成本

使用24個專用的并行SMU通道(每一個探針一個通道),以較小的尺寸將制造周期縮短3 倍

使用軟件包開發靈活的測試和測量例程,進一步提高系統功能

晶圓/芯片工藝過程從空白的硅晶圓開始到最終制成電子功能芯片終結,整個過程需要依次執行數百個專業的工藝步驟(稱為工藝流程)。但是,考慮到R&D環境的性質以及各個工藝步驟的復雜性,如果在某個工藝流程中出現問題,可能導致功能器件的良率大幅下降。 在工藝流程的早期對晶圓上的單個芯片/器件進行電子測試,有助于了解片上設備的性能和執行早期的半導體工藝監管。目前已有具備在線測試功能的大型設備,但是對于之前的fab工廠來說,若沒有在其中嵌入在線(in-line)電氣測試系統,就無法獲得工藝流程中關鍵點的反饋。因此不得不從fab廠中取出晶圓,然后使用現有的參數測試儀對其進行測試,這就會導致整個流程中斷。而且,由于污染問題,從fab廠取出來的晶圓無法返回進行進一步加工,就會損失大量的晶圓,制造周期大大增長,項目交付時間也大大延遲了。

圖1.半導體制造工藝流程簡圖 工廠研發的測試芯片系統由數千個具有各種尺寸和架構的晶體管、電阻器和電容器組成。其中可能包含小型演示電路,我們需要測試所有這些器件,以正確分析特定的半導體制造工藝。 如果有一套工廠內部半導體自動測試設備(ATE),能夠24/7全天候執行測試操作,就可以大大減少研發項目的交付時間并降低總體成本。因此我們需要一種多功能的測試系統,可以快速、準確地執行測試,以支持我們的各種行業聯盟計劃。并要求該系統需要能夠滿足所有的參數和功能IC測試需求,而且可以輕松擴展來滿足未來半導體制造工業技術的測試需求。

02 第一階段測試

為了減少晶圓檢測的成本就需要更高效的替代解決方案。但是市場上的測試系統不是專注于參數測試,就是專注于功能測試,無法兼顧。而且,傳統的參數測試儀利用開關矩陣來共享SMU,數字萬用表(DMM)和LCR測試儀等資源,這會降低信號的完整性并使操作順序化,無法并行執行。此外這些儀器通常需要花費很長時間來進行編程序,而且采用固定密封裝,缺乏靈活的性,價格也很昂貴。

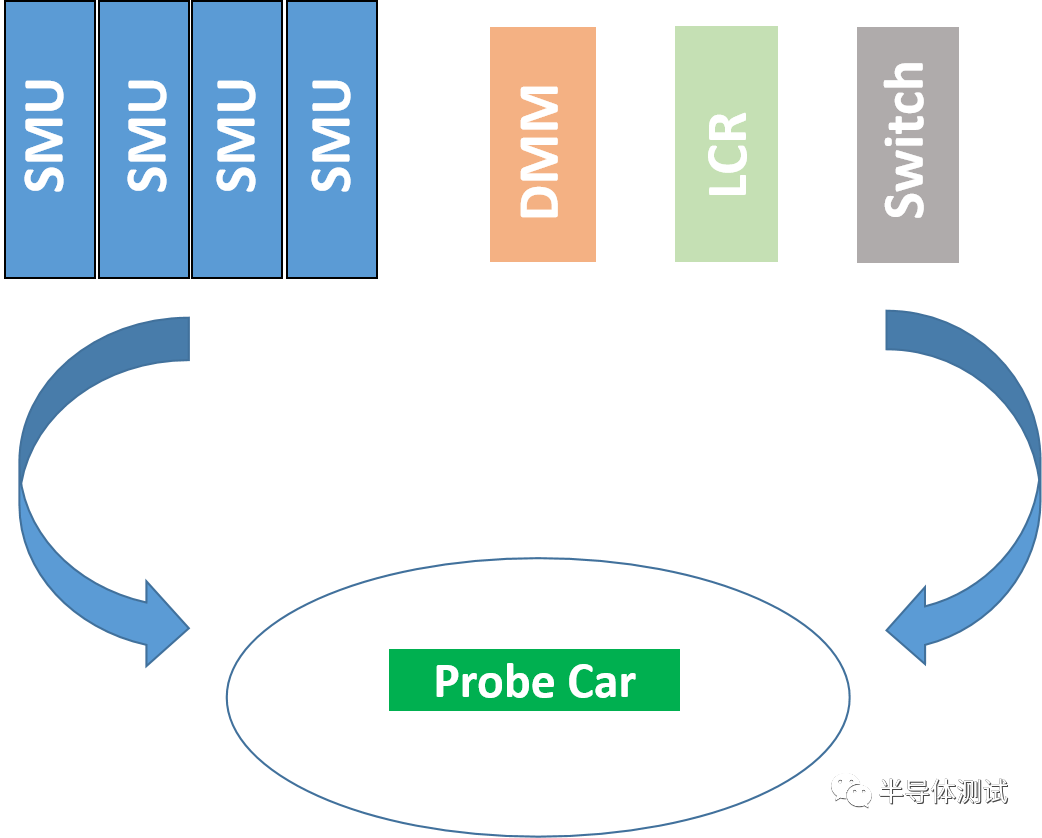

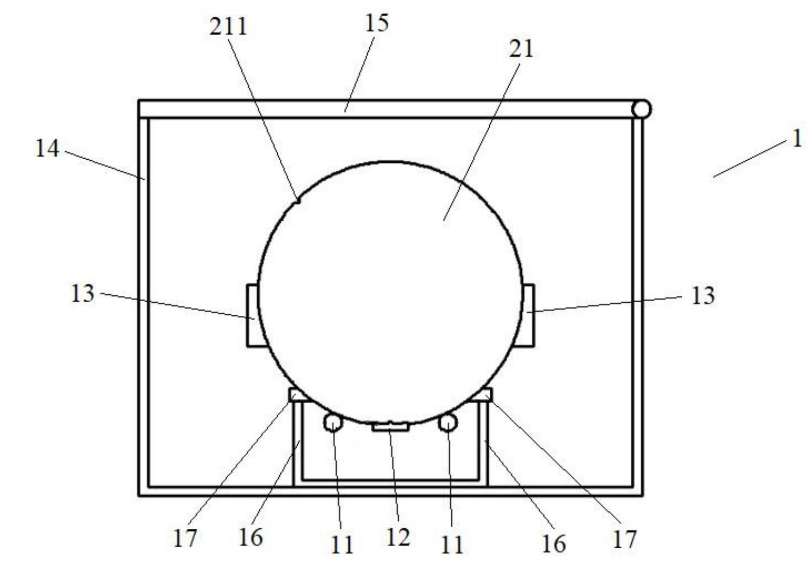

自發展至今,PXI被各行各業廣泛采用,可有效的幫助企業降低成本、提高績效,同時具有強大的經濟實力,可以更輕松地幫助各個企業度過不同的產業波動期。最終選擇了一種高精度的每通道SMU儀器;除了PXI儀器外,還配備了自動晶圓加工系統的探針臺,該系統可以在無人值守的情況下運行;開發了一個定制的探針卡,并將所有晶圓探測組件連接到一個容納PXI儀器的19英寸機架中。測試系統包括PXI SMU與DMM、LCR儀表和第三方低泄漏開關矩陣,他們在測試點之間共享資源。如圖2所示。

接著利用軟件,在使用PXI模塊化儀器的ATE上開發并部署了一個參數測試例程庫,并對其進行了基準測試,最終對過程監控結構進行了測量。實現了全自動、無人值守的晶圓測試,并順利地將電氣數據覆蓋為其他在線(光學)計量數據,進行深入地進行過程分析。

圖2.第一階段測試系統框架圖

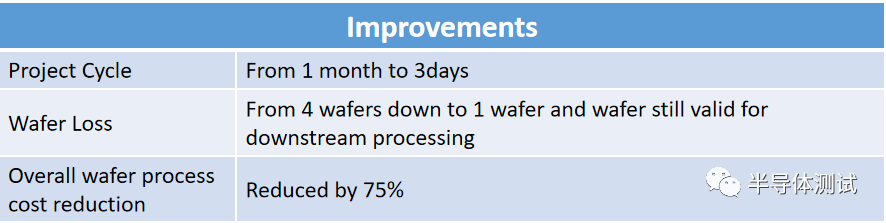

圖3.相對于傳統測試方法的改進

通過fab工廠內部ATE,我們可以執行以前的不可能完成的實驗或晶圓成本很高的實驗。作為一個獨立的研究機構,這些新的實驗為研發的半導體工藝技術提供了非常有價值的信息。圖3顯示的是實驗中一些非常重要的改進。

03 第二階段測試

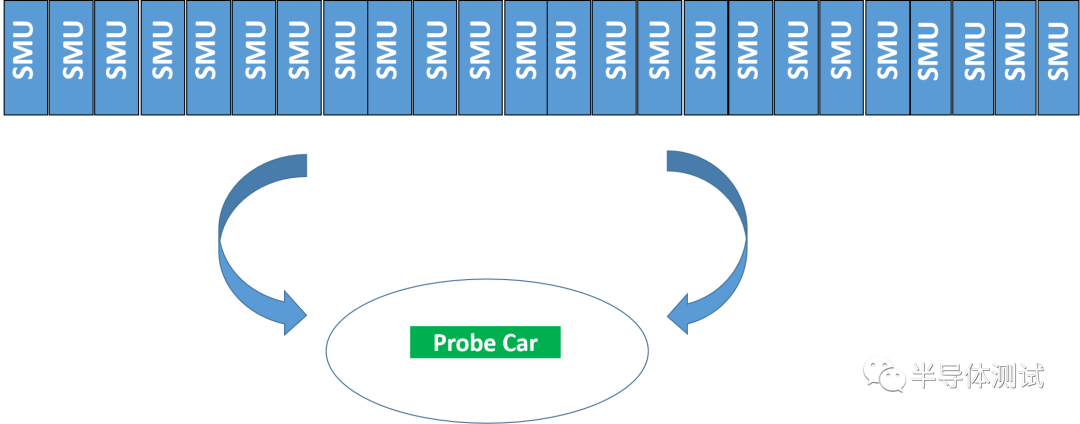

將ATE系統的硬件配置為兩臺菊花鏈式PXI機箱,25個PXIeSMU(其中24個連接到與晶圓前端接觸的探針,一個連接到吸盤觸點),以及一個功能強大的機架式控制器。探針臺和晶圓上料設備通過GPIB-USB接口進行控制,軟件包依然作為軟件架構的核心。 這種每針SMU方法的性能非常驚人,大大減少了測試時間,這對于大型的傳統臺式SMU來說是不可能的。由于這一方法可實現高度并行測量,不需要按順序進行測量,節省了中間的切換步驟,因此總測試時間減少到僅為測試一個測試點的時間。

圖4.第二階段測試系統框架

假設一個探針墊模塊具有24個焊盤和12個二極管;每個二極管連接到兩個焊盤。對于fA級的二極管泄漏測量,我們需要較長的測試積分(孔徑)時間來抑制測量噪聲。這一個積分時間可能會超過32個電源周期(PLC),相當于640 ms(32 PLC x 20 ms/PLC)。在采用開關矩陣的傳統順序測試中,開關和建立時間大約為10 ms,這也是一個重要的影響因素。關于這一點,在第1階段的系統中,每一個探針墊模塊塊的開關和建立時間大約為7.92 s。而對于高度并行的配置,測試時間有效地減少到一個二極管的測量時間(640毫秒),快了12倍。

04 總結

根據多個應用程序的測試時間數據,并綜合考慮了探針的步進時間之后,可以發現測試速度提高了 3.35倍,過去的測試時間為每晶圓67分鐘,而現在采用并行測試后,每晶圓的測試時間減少為20分鐘。因此可以肯定地說,從第一階段到第二階段,測試吞吐量增加了三倍!在工藝制造周期日益縮短的情況下,吞吐量的增加將有助于于我們更加快速地交付研發成果 。此外,還可以在工藝流程的早期提取大量數據,進行晶圓級可靠性研究。

總而言之,基于PXI的模塊化測試儀器可以有效降低檢測成本、提高檢測速率。

原文標題:降低芯片測試成本的有效手段!

文章出處:【微信公眾號:半導體測試】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

456文章

51155瀏覽量

426452 -

晶圓

+關注

關注

52文章

4973瀏覽量

128235

原文標題:降低芯片測試成本的有效手段!

文章出處:【微信號:gh_7b104c88257c,微信公眾號:半導體測試】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

WAT晶圓接受測試簡介

減少晶圓損失和成本的測試方法!

減少晶圓損失和成本的測試方法!

評論