之前介紹了 SelectIO 邏輯資源,本篇咱們就聊一聊與SelectIO 邏輯資源水乳交融、相得益彰的另一個概念——IO_FIFO。

1個IO_FIFO包括1個IN_FIFO 和1個OUT_FIFO,它是7系列FPGA新設計的IO專用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)邏輯功能的擴展。

FPGA的每個BANK有4個IN_FIFO和4個OUT_FIFO,相當于每12個IO對應1個IN_FIFO和1個OUT_FIFO。

IN_FIFO從ILOGIC接收4bit位寬的輸入數據,但卻可以輸出4bit或者8bit位寬的數據到FPGA內部SLICE。OUT_FIFO正好相反,從OLOGIC接收4bit或者8bit位寬的輸入數據,但卻輸出4bit位寬數據。

每一個IO_FIFO的存儲大小為768bit,可以配置成12組4X4位寬數據的FIFO,也可以配置成10組4X8bit位寬數據的FIFO。每個IO_FIFO的深度為9。如圖1所示為IO_FIFO的結構示意圖:

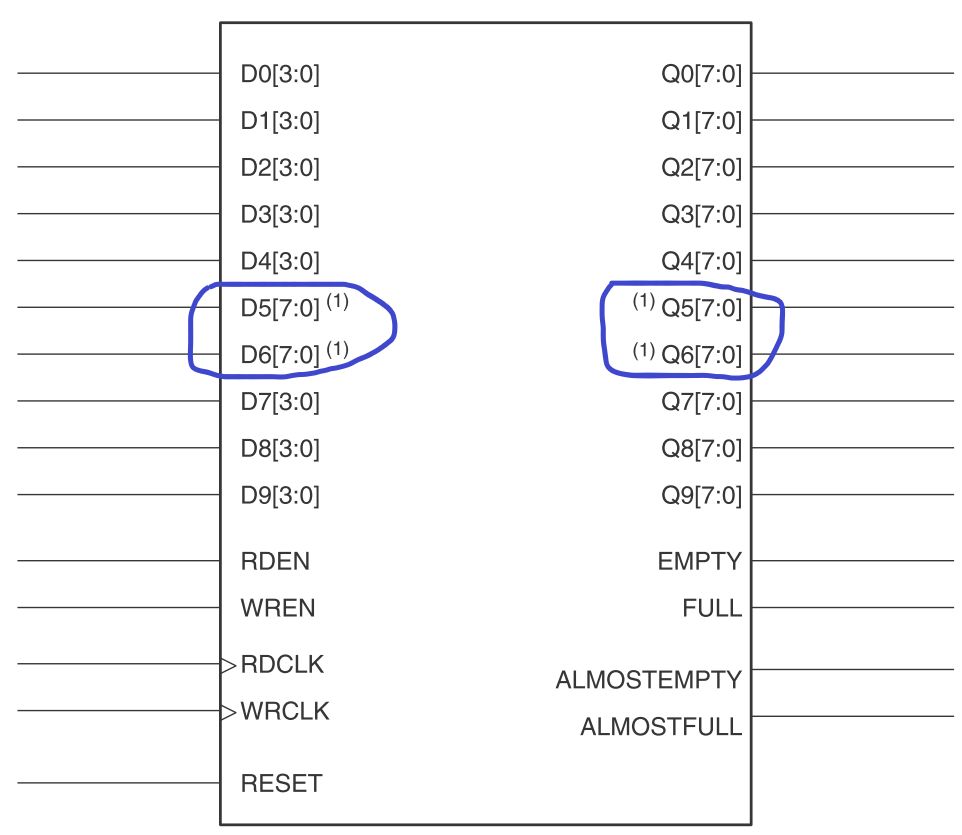

如圖2所示為IN_FIFO的原語框圖:

正如前面所說,當配置成12組的4bit位寬輸入,4bit位寬輸出時,輸入D0[3:0]~ D9[3:0]對應輸出Q0[3:0]~ Q9[3:0];輸入D10[3:0]即為輸入D5[7:4],對應輸出Q5[7:4];輸入D11[3:0]即為輸入D6[7:4],對應輸出Q6[7:4]。

當配置成10組4bit位寬輸入,8bit位寬輸出時,D0[3:0]~D9[3:0]對應輸出Q0[7:0]~ Q9[7:0],此時寫時鐘頻率是讀時鐘頻率的2倍。OUT_FIFO和IN_FIFO操作過程正好相反,咱們這里就不羅嗦了。

總的來說,IO_FIFO其實就是存儲深度比較小、位寬固定為4/8bit的普通FIFO ,7系列FPGA單獨設計了這樣的FIFO,更適用于IO接口處的字節/半字節數據緩存。

編輯:hfy

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605204 -

數據緩存

+關注

關注

0文章

23瀏覽量

7117

發布評論請先 登錄

相關推薦

【米爾-Xilinx XC7A100T FPGA開發板試用】Key-test

【米爾-Xilinx XC7A100T FPGA開發板試用】測試一

【米爾-Xilinx XC7A100T FPGA開發板試用】+01.開箱(zmj)

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx 7系列FPGA PCB設計指導

FPGA | Xilinx ISE14.7 LVDS應用

國產FPGA核心板!米爾紫光同創Logos-2和Xilinx Artix-7核心板

FPGA核心板 Xilinx Artix-7系列XC7A100T開發平臺,米爾FPGA工業開發板

FPGA核心板上市!紫光同創Logos-2和Xilinx Artix-7系列

Xilinx fpga芯片系列有哪些

AMD Xilinx 7系列FPGA的Multiboot多bit配置

xilinx7系列FPGA新設計的IO專用FIFO解析

xilinx7系列FPGA新設計的IO專用FIFO解析

評論