xilinx FPGA IOB約束使用以及注意事項

一、什么是IOB約束

在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距離IO最近的寄存器,同時位置固定。當你輸入或者輸出采用了IOB約束,那么就可以保證從IO到達寄存器或者從寄存器到達IO之間的走線延遲最短,同時由于IO的位置是固定的,即存在于IO附近,所以每一次編譯都不會造成輸入或者輸出的時序發生改變。

二、為什么要使用IOB約束

考慮一個場景,當你用FPGA寫了一個spi模塊,將時鐘、片選和數據線綁定到FPGA的IO管腳,如果沒有加IOB約束的話,綜合工具在布局布線的時候直接將FPGA內部寄存器輸出連到IO上,但是這樣存在一定的問題,每次修改邏輯重新編譯的時候,輸出寄存器的位置有可能發生改變,那么從寄存器輸出到IO之間的布線長度就會發生變化,造成寄存器輸出到達IO之間的走線延遲發生改變,每一次編譯都會使得spi的輸出時序不確定。

為了解決這個問題,需要加入IOB約束,將模塊輸出端口的最后一級寄存器放在IOB上,這樣最后一級輸出的寄存器位置就固定下來了,每次編譯都不會造成輸出時序發生改變。

IOB約束使用方法如下:

1、在約束文件中加入下面約束:

set_property IOB true [get_ports {port_name}]

set_property IOB true [get_cells {cell_name}]

2、直接在代碼中加約束,在寄存器前加入下面約束,需要注意的是,對于輸入IOB約束,這里的寄存器是第一級寄存器,對于輸出IOB約束,這里的寄存器是最后一級寄存器,且寄存器輸出不能再作為組合邏輯輸入。

(* IOB = "true" *) reg O_data;

三、IOB約束使用注意事項

對于輸出IOB約束,在使用的時候有一些限制:

1、約束的端口必需是寄存器輸出,這點比較好理解,因為IOB約束本質上是約束最后一級寄存器的位置,將最后一級寄存器的位置放在IOB上,而不是增加一級寄存器。所以你必須要是寄存器輸出,才能進行IOB約束,這是前提。

2、最后一級寄存器的輸出不能再作為輸入反饋到內部邏輯中,必需是開路的。舉個例子,比如如下代碼:

always @ (posedge clk)

begin

if(cnt == 2'b1 || cnt == 2'b3)

spi_clk <= ~spi_clk;

else

spi_clk <= spi_clk;

end

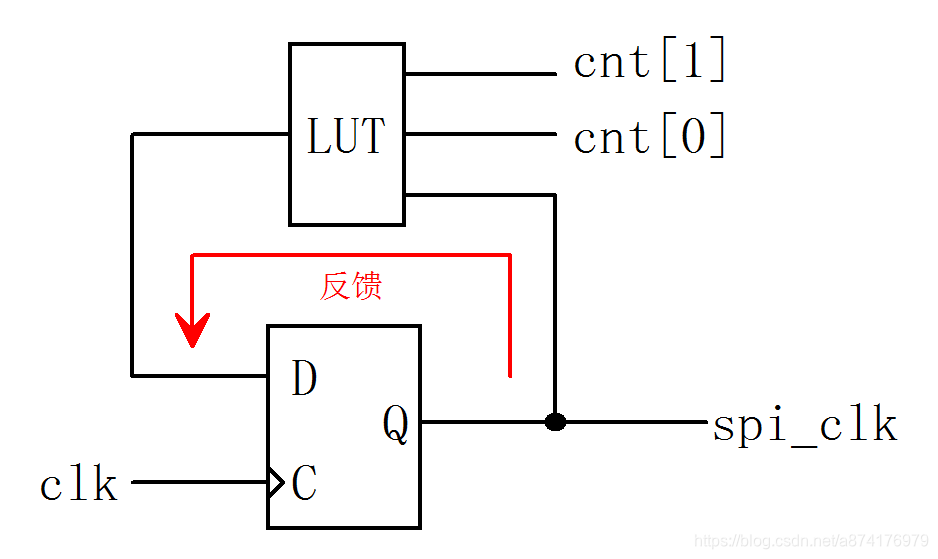

上面描述了一個分頻器,當計數器cnt為1和3的時候spi_clk翻轉,那這個時候spi_clk就是一個輸出又作為輸入反饋到內部的寄存器,得到的綜合結果如下圖:

由于需要將寄存器的輸出作為輸入其他邏輯的輸入,這種情況下是無法將spi_clk寄存器放到IOB上的,因為IOB的輸出直接對接IO,無法再作為輸入反饋到內部邏輯。

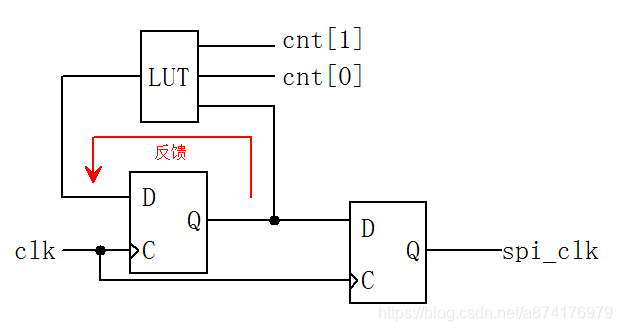

所以可以將spi_clk輸出再加一級寄存器,將加入的寄存器放到IOB上,相應的需要對時序做出一定的調整,和sip_clk有時序關系的都需要打一拍以保持同步。

-

FPGA

+關注

關注

1630文章

21783瀏覽量

605030 -

Xilinx

+關注

關注

71文章

2170瀏覽量

121875

原文標題:xilinx FPGA IOB約束使用以及注意事項

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA的高速接口應用注意事項

FPGA設計的注意事項

xilinx FPGA的IOB使用教程說明

FPGA管腳調整的注意事項

Xilinx FPGA的約束設置基礎

xilinx FPGA IOB約束使用以及注意事項

xilinx FPGA IOB約束使用以及注意事項

評論