本篇文章參考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global

在沒看這篇文章前,回想一下平時(shí)我們常用的復(fù)位方式:

① 首先,上電后肯定是要復(fù)位一下,不然仿真時(shí)會出現(xiàn)沒有初值的情況;

② 最好有個復(fù)位的按鍵,在調(diào)試時(shí)按一下復(fù)位鍵就可以全局復(fù)位了;

③ 也許是同步復(fù)位,也許是異步復(fù)位,不同的工程師可能有不同的方案。

但如果認(rèn)真看了Xilinx的White Paper,就會對復(fù)位有了新的認(rèn)識。

我們把White Paper的內(nèi)容總結(jié)為下面4個問題:

① 需不需要復(fù)位?

② 同步復(fù)位 or 異步復(fù)位?

③ 高復(fù)位 or 低復(fù)位?

④ 全局復(fù)位 or 局部復(fù)位?怎么用?

1. 需不需要復(fù)位?

看到這個問題,可能很多同學(xué)會有點(diǎn)懵,怎么可能不需要復(fù)位?其實(shí)Xilinx FPGA在系統(tǒng)上電配置時(shí),會有一個GSR(Global Set/Reset)的信號,這個信號有以下幾個特點(diǎn):

? 預(yù)布線

? 高扇出

? 可靠的

這個信號可初始化所有的cell,包括所有的Flip-Flop和BRAM。

如果我們在程序里用自己生成的復(fù)位信號,也只能復(fù)位Flip-Flop。

這個GSR信號我們可以在程序中通過實(shí)例化STARTUP直接調(diào)用,但Xilinx并不推薦這么使用。

主要原因是FPGA會把像系統(tǒng)復(fù)位這種高扇出的信號放到高速布線資源上,這比使用GSR要快,而且更容易進(jìn)行時(shí)序分析。

雖然有GSR,但這并不是說要避免使用復(fù)位信號,以下兩種情況就必須要加復(fù)位:

? 帶有反饋的模塊,比如IIR這種濾波器和狀態(tài)機(jī),當(dāng)狀態(tài)跑飛了,就需要復(fù)位一下

? 應(yīng)用過程中需要復(fù)位的寄存器

這個就具體看是什么應(yīng)用了,我們公司的很多寄存器都需要在調(diào)試過程中需要經(jīng)常復(fù)位,像這種復(fù)位就是必須的了。

所以,需不需要復(fù)位完全看設(shè)計(jì)。這里多提一點(diǎn),時(shí)序收斂也是一樣,主要看設(shè)計(jì),而不是約束。

2. 同步復(fù)位 or 異步復(fù)位?

在HDL中,如果敏感列表中不包含rst,會被綜合成同步復(fù)位:

always @ ( posedge clk )

begin

if(rst)

...

end

如果敏感列表中包含rst,則會被綜合成異步復(fù)位:

always @ ( posedge clk or posedge rst)

begin

...

end

同步復(fù)位的好處,不言而喻,有利于時(shí)序分析,降低亞穩(wěn)態(tài)的幾率,避免毛刺。

同步信號的缺點(diǎn):

? 復(fù)位信號有效電平持續(xù)時(shí)間必須大于時(shí)鐘周期,不然時(shí)鐘可能采不到復(fù)位

? 在沒有時(shí)鐘的時(shí)候無法復(fù)位

也有很多同學(xué)會說同步復(fù)位會需要額外的資源,但對于Xilinx的FPGA,是沒有這個問題的,具體原因后面講。

對于異步復(fù)位,好處就是同步復(fù)位的反方面:脈沖寬度沒有限制,沒有時(shí)鐘也可以復(fù)位。

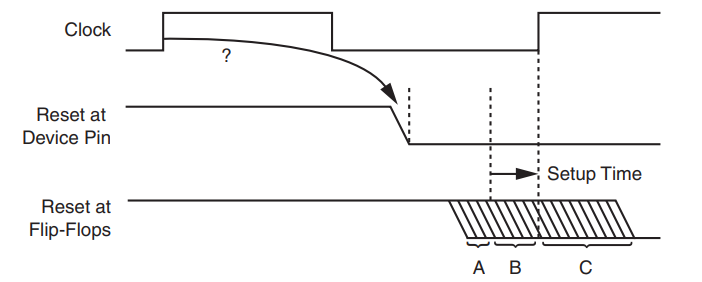

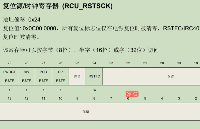

缺點(diǎn)就是異步電路,容易引起亞穩(wěn)態(tài),產(chǎn)生毛刺,不利于時(shí)序分析,而且不同觸發(fā)器的復(fù)位時(shí)間可能不同。下面這個圖中,在A時(shí)刻接收到復(fù)位信號拉低的FF可以在下一個時(shí)鐘上升沿時(shí)就釋放復(fù)位狀態(tài),但C時(shí)刻接收到復(fù)位信號拉低的FF則在下下個時(shí)鐘上升沿時(shí)才能釋放復(fù)位狀態(tài)。

按照White Paper上所講,99.99%的概率這種情況都不會發(fā)生,但如果你剛好碰到一次這種現(xiàn)象,那你就是那0.01%。

下面我們來舉一個例子來說明同步復(fù)位和異步復(fù)位,F(xiàn)PGA為V7,代碼如下:

module rst_demo(

input clk,

input rst1,

input rst2,

input in1,

input in2,

output reg out1,

output reg out2);

always @ ( posedge clk )

begin

if(rst1)

out1 <= 1'b0;

else

out1 <= in1;

end

always @ ( posedge clk or posedge rst2 )

begin

if(rst2)

out2 <= 1'b0;

else

out2 <= in2;

end

endmodule

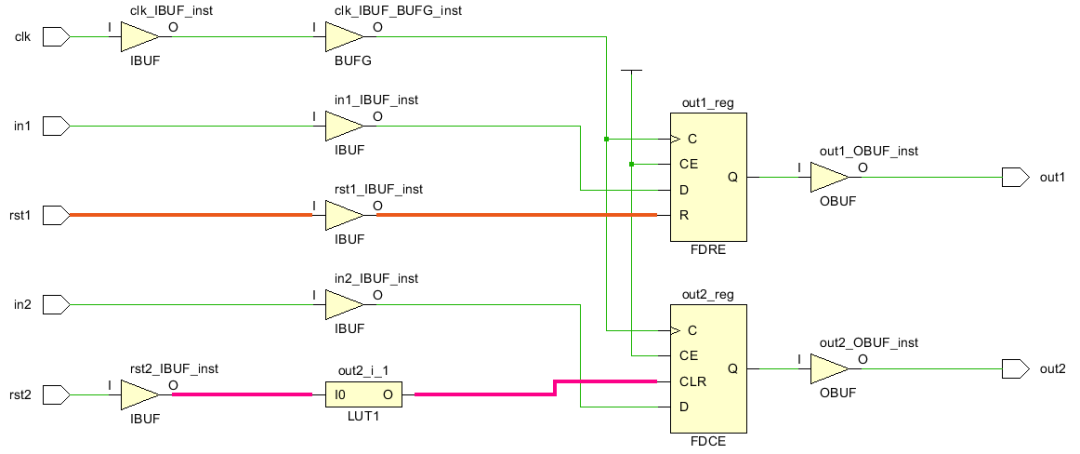

綜合后的schematic如下圖:

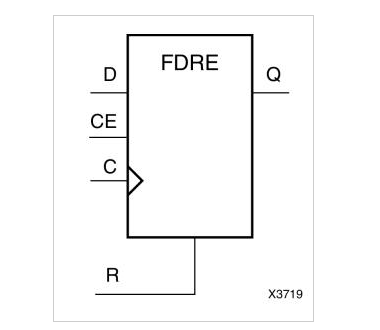

可以看出來,同步復(fù)位和異步復(fù)位都是占用一個Storage Element,我們在之前的一篇文章中講過Storage Element可以配置為Latch,同樣的,也可以配置為FDRE和FDCE,而且在7Series手冊中也并未提到配置成FDRE或FDCE時(shí)是否會占用更多資源(比如,7Series的FPGA中,一個Slice中有8個Storage Element,如果其中一個被配置成了Latch,那有4個Storage Element是不能用的),因此在Xilinx的FPGA中,同步復(fù)位和異步復(fù)位在資源占用上,并沒有區(qū)別。

3. 高復(fù)位 or 低復(fù)位?

很多處理器上的復(fù)位都是低復(fù)位,這也導(dǎo)致了很多同學(xué)在使用復(fù)位信號時(shí)也習(xí)慣使用低復(fù)位了。但從我們上一節(jié)所講中可以看出,無論是同步復(fù)位還是異步復(fù)位,復(fù)位信號都是高有效,如果采用低復(fù)位,還需要增加一個反相器。

如果接收到其他處理器發(fā)過來的低有效復(fù)位信號,我們最好在頂層模塊中翻轉(zhuǎn)復(fù)位信號的極性,這樣做可以將反相器放入IO Logic中,不會占用FPGA內(nèi)部的邏輯資源和布線資源。

這里多補(bǔ)充一點(diǎn),如果使用Zynq和Microblaze,則Reset模塊默認(rèn)是低復(fù)位,我們可以手動設(shè)置為高復(fù)位。

4. 全局復(fù)位 or 局部復(fù)位?怎么用?

我們對復(fù)位常用的做法是將系統(tǒng)中的每個FF都連接到某個復(fù)位信號,但這樣就造成了復(fù)位信號的高扇出,高扇出就容易導(dǎo)致時(shí)序的違規(guī)。而且全局復(fù)位占用的資源比我們想象中要高的多:

? 布線資源占用

? 其他網(wǎng)絡(luò)的布線空間就相應(yīng)減少

? 可能會降低系統(tǒng)性能

? 增加布線時(shí)間

? 邏輯資源占用

? 占用FF作為專門的復(fù)位電路

? 如果該復(fù)位信號還受其他信號控制,會導(dǎo)致FF的輸入前增加門電路

? 會增加整個設(shè)計(jì)的size

? 增加的邏輯資源會影響系統(tǒng)性能

? 增加布局布線時(shí)間

? 全局復(fù)位不會使用像SRL16E這種高效結(jié)構(gòu)

? 在LUT中SRL16E可當(dāng)作16個FF

? 這些Virtual FF不支持復(fù)位

? 增加設(shè)計(jì)的size,并降低系統(tǒng)性能

? 增加布局布線時(shí)間

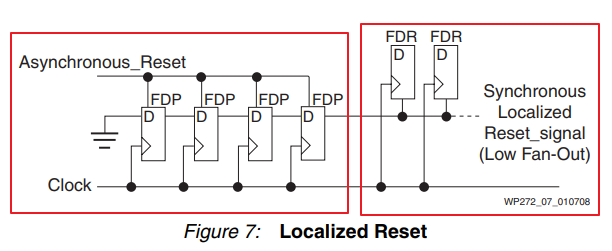

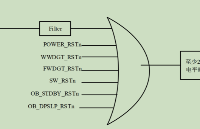

因此,Xilinx推薦盡量使用局部復(fù)位的方式,前面我們也講到然同步復(fù)位和異步復(fù)位都多多少少有些問題,那有沒有一種方式可以結(jié)合同步復(fù)位和異步復(fù)位的優(yōu)點(diǎn)?當(dāng)然有,就是異步復(fù)位,同步釋放。這種方法可以將兩者結(jié)合起來,取長補(bǔ)短。如下圖所示,所謂異步復(fù)位,就是輸入的復(fù)位信號仍然是異步的,這樣可以保證復(fù)位信號能夠起效;而同步釋放是指當(dāng)復(fù)位信號釋放時(shí),輸出的sys_rst并不是立即變化,而且被FF延遲了一個時(shí)鐘周期,這樣讓復(fù)位和時(shí)鐘同步起來。

圖中的Verilog代碼如下:

module rst_demo(

input clk,

input rst_async,

(* keep = "true" *)

output reg rst_module1 = 0,

(* keep = "true" *)

output reg rst_module2 = 0

);

reg sys_rst;

reg rst_r;

always @(posedge clk or posedge rst_async) begin

if (rst_async) begin

rst_r <= 1'b1;

end

else begin

rst_r <= 1'b0;

end

end

always @(posedge clk or posedge rst_async) begin

if (rst_async) begin

sys_rst <= 1'b1;

end

else begin

sys_rst <= rst_r;

end

end

always @ ( posedge clk ) begin

rst_module1 <= sys_rst;

rst_module2 <= sys_rst;

end

endmodule

綜合后的schematic如下圖:

異步復(fù)位模塊輸出的sys_rst通過n個D觸發(fā)器后輸出給n個模塊,當(dāng)做模塊的復(fù)位信號。

總結(jié)

在使用復(fù)位信號時(shí),考慮這個寄存器需不需要在運(yùn)行過程中進(jìn)行復(fù)位,如果只需要上電后復(fù)位一次,那只需在定義時(shí)寫上初值即可,無需使用其他復(fù)位信號;在Xilinx的FPGA中盡量使用高有效的復(fù)位信號,采用異步復(fù)位同步釋放的方式,并且要將復(fù)位信號局部化,避免使用高扇出的全局復(fù)位。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1630文章

21794瀏覽量

605128 -

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

120925 -

Xilinx

+關(guān)注

關(guān)注

71文章

2170瀏覽量

121906 -

復(fù)位信號

+關(guān)注

關(guān)注

0文章

54瀏覽量

6354

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA復(fù)位的8種技巧

復(fù)位電路的設(shè)計(jì)問題

復(fù)位電路介紹 復(fù)位電路的原理及作用

單片機(jī)異常復(fù)位的原因

STM32復(fù)位電路用復(fù)位芯片和阻容復(fù)位電路區(qū)別

解讀MIPI A-PHY與車載Serdes芯片技術(shù)與測試

FPGA同步復(fù)位和異步復(fù)位

示波器測量復(fù)位信號的原理和方法

向FPGA設(shè)計(jì)添加復(fù)位功能的注意事項(xiàng)

MCU復(fù)位RAM會保持嗎,如何實(shí)現(xiàn)復(fù)位時(shí)變量數(shù)據(jù)保持

ABB變頻器怎么復(fù)位 | 復(fù)位時(shí)可能會出現(xiàn)哪些問題?

復(fù)位電路的電阻電容分別有什么作用?

如何排查GD32 MCU復(fù)位是由哪個復(fù)位源導(dǎo)致的?

GD32 MCU電源復(fù)位和系統(tǒng)復(fù)位有什么區(qū)別

詳細(xì)解讀FPGA復(fù)位的重點(diǎn)

詳細(xì)解讀FPGA復(fù)位的重點(diǎn)

評論