一.高速串行傳輸兼容設計的三個基礎

作為與高速串行傳輸兼容的設計,可以抑制反射,減少傳輸損耗并抑制噪聲,

電路板的設計遵循以下三個基本準則:

1.差分布線的阻抗控制;

2.最小化差分布線長度;

3.盡可能使差分對內的布線長度匹配。

關于反射的抑制,不僅可以通過優化設計規格來控制上述布線,而且可以控制通孔(通孔)的阻抗,并且在數字消費設備中變得越來越流行。必須考慮安裝區域的影響來優化連接器,并充分了解電纜的實際特性。例如,如果連接器的安裝區域的圖案設計不正確,在許多情況下會存在額外的寄生電容,并且阻抗會下降和反射,這會惡化傳輸波形,因此必須對該區域進行優化。

此外,對于需要在高速串行傳輸中進行仿真的區域,我們認為它是5 Gbps或更高。這是因為5 Gbps PCI Express規范指出必須在模式設計階段使用仿真進行確認,而且在許多情況下,還會聽到實際問題。

二.高速串行傳輸的回波損耗標準

對于高速串行傳輸,可能會有一些標準,其中包含回波損耗和反射量的規范。

通用接口的典型示例是硬盤SSD串行ATA和廣播,安全性和醫學成像領域的SDI。

在這些情況下,半導體與外部I / O連接器之間的圖案設計將決定通過/失敗。這是需要PCB設計技術的領域。

例如,用于串行ATA的表面安裝連接器趨于具有較大的寄生電容,這會降低阻抗并降低性能。

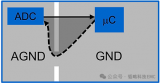

作為對策,通過部分地去除基板的表面層上的安裝焊盤下方的實心平面以減小寄生電容,可以使配線的特性阻抗相同并且改善特性。積累專門知識對于這種優化很重要,但是為了滿足廣泛的需求,也可以使用可以從電路板設計信息中高精度提取特征的軟件。

三.總結

為了支持高速串行傳輸,除了控制差分布線的阻抗,最小化差分布線長度并盡可能確保差分對內的布線長度的基本要素外,安裝位置的通孔和局部阻抗控制很重要。這在存在回波損耗標準的SDI接口中尤為明顯,并且使用仿真的電路板設計被認為是必不可少的。

-

電路板設計

+關注

關注

1文章

127瀏覽量

16546 -

PCB設計

+關注

關注

394文章

4697瀏覽量

86120 -

PCB布線

+關注

關注

21文章

463瀏覽量

42105 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4687

發布評論請先 登錄

相關推薦

FPI10015 PCIe連接器,連接更穩定,滿足高速率傳輸設備互連需求

PCIe數據傳輸協議詳解

深度解析高速串行信號的誤碼測試

淺談EMC設計準則

深度解析高速串行信號的誤碼測試|線上講堂

高速串行傳輸兼容設計的設計準則

高速串行傳輸兼容設計的設計準則

評論