歡迎各位朋友關注“郝旭帥電子設計團隊”公眾號,本公眾號會定時更新相關技術類資料、軟件等等,感興趣的朋友可以瀏覽一下本公眾號的其他“模塊”,希望各位朋友都能在本公眾號獲得一些自己想要的“東西”。

高速串行通信的“高速”一般比較高,基本至少都會上G。如果利用FPGA內部的LUT、觸發器和普通IO是無法滿足這樣高的輸入輸出速率的。

例:假設線速度需要跑到1G,那么我們FPGA內部邏輯就需要跑到1GHz,才可以對外發出1G的bit流(即使采用DDR的方式發出,也需要內部500MHz)。這么高的頻率,FPGA內部一般是無法達到的。

那么FPGA是如何實現這種高速輸出和輸入的呢?

FPGA內部除了LUT、觸發器和IOB以外,廠商還在FPGA內部加入了很多可配置的硬核電路,高速收發器就是其中之一(并不是所有的FPGA都有)。

那么這個高速收發器的電路怎么理解呢?

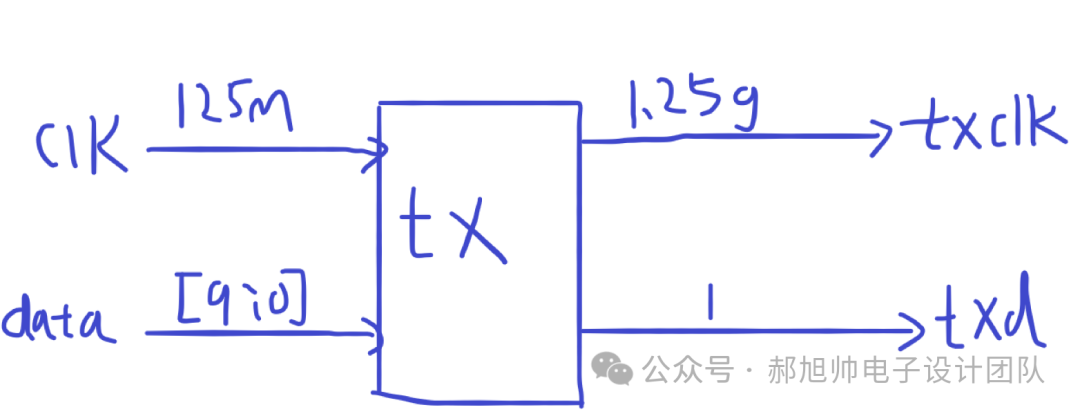

可以先這么認為,對于輸出來說它就是一個升頻降位寬的電路。

注:輸出不一定有時鐘輸出

例:輸入時鐘125MHz,數據并行10bit;經過高速發送器后,可以變為輸出速率為1.25GHz,數據為串行1bit;

此時FPGA內部只需要運行再一個相對較低的頻率,進行并行處理數據即可。

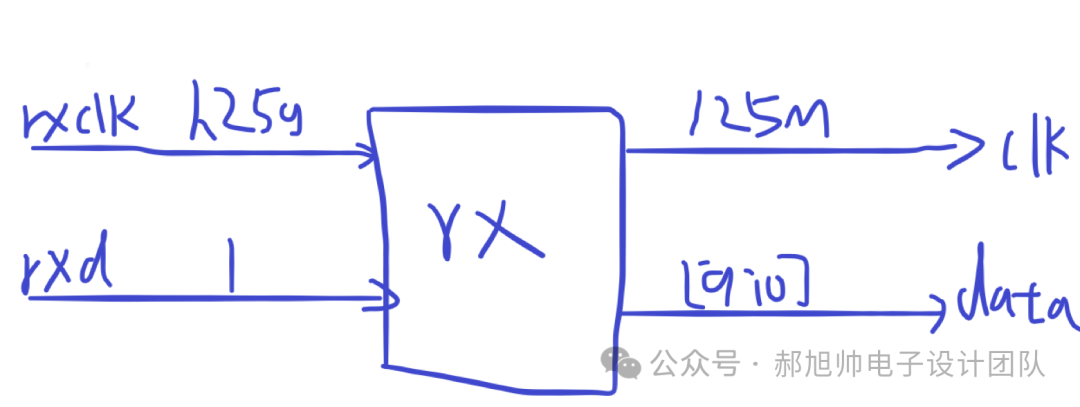

對于輸入來說它就是一個降頻增位寬的電路。

注:輸入不一定有時鐘輸入

例:輸入時鐘1.25GHz,數據串行1bit;經過高速接收器后,可以變為輸入速率為125MHz,數據為并行10bit;

此時FPGA內部只需要運行再一個相對較低的頻率,進行并行處理數據即可。

下面簡單介紹一下FPGA內部的高速收發器(主要以Xilinx的A7 FPGA為例,其他的“大概”大同小異)。

FPGA內部的高速收發器一般稱為GT(GT的意思是Gigabyte Transceiver),速度根據器件的不同能夠支持的速率也不相同。在Xilinx 7系列的FPGA中,按支持的最高線速率排序,GTP是最低的,GTZ是最高的。GTP被用于A7系列,GTZ被用于少數V7系列。從K7到V7,最常見的是GTX和GTH。GTH的最高線速率比GTX稍微高一點點。

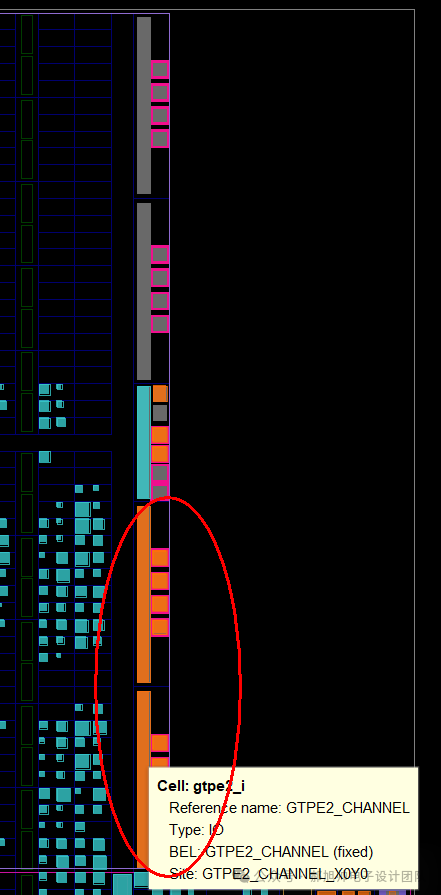

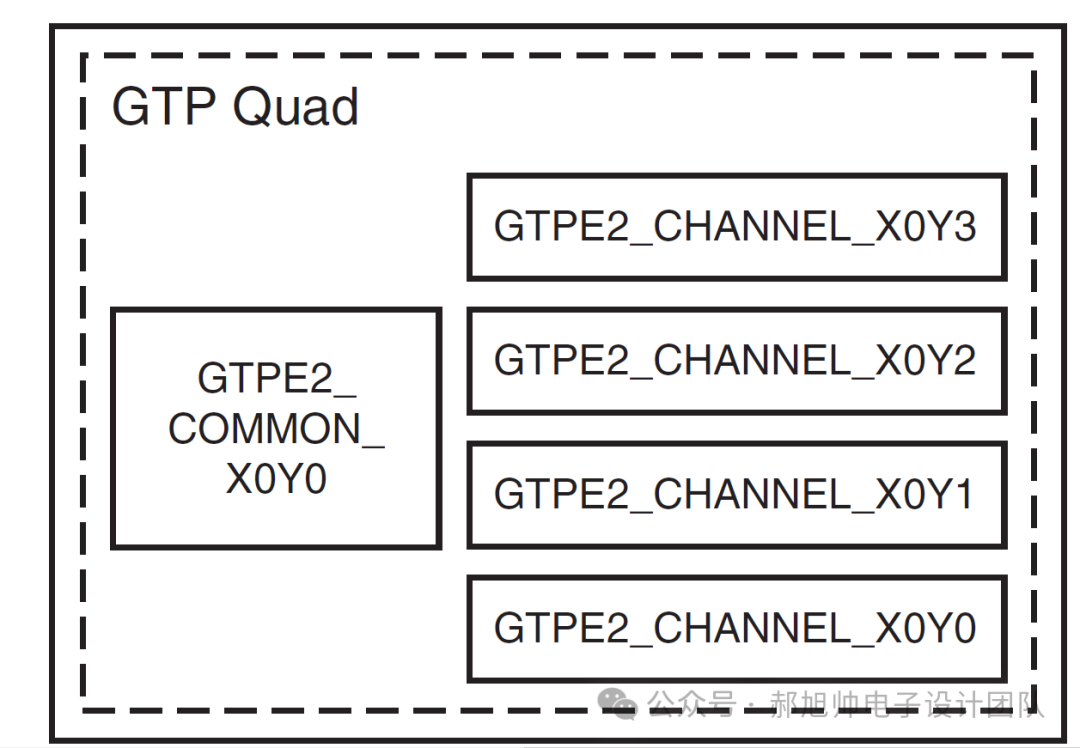

下圖是Xilinx A7 FPGA內部的高速收發器(GTP)。

GTP對外的管腳也不是普通的IO,必須得是專門的IO(單獨的bank)。

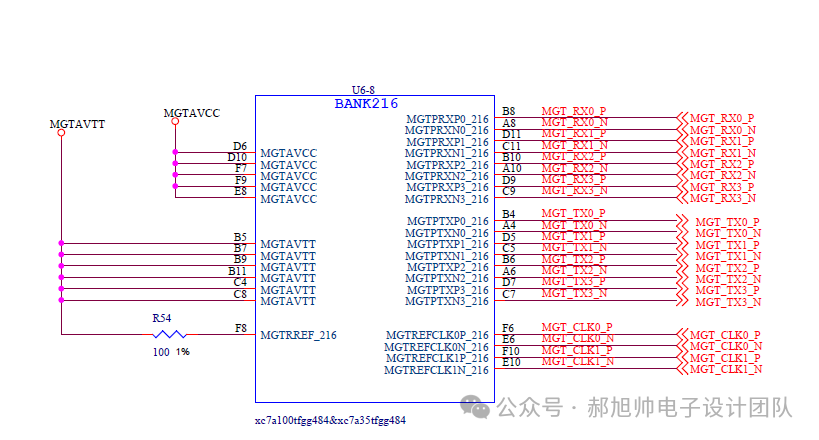

下圖為A7 FPGA 的支持GTP的bank(一般稱為MGT:Multi-Gigabit Transceiver bank)。

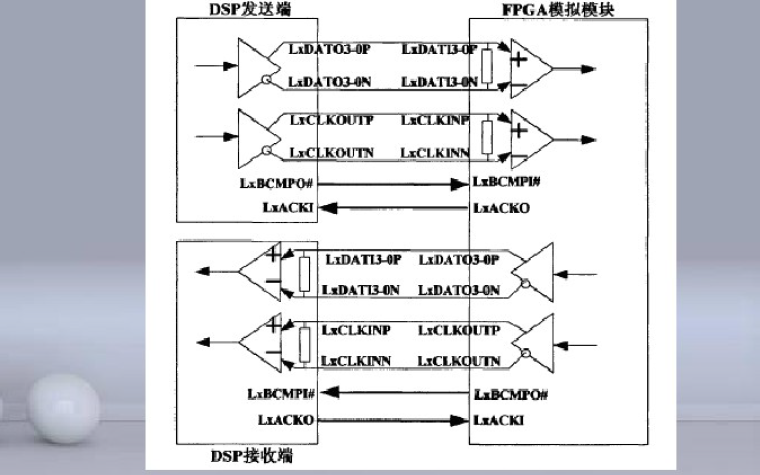

上述的電路圖中有四路收發器(一發一收稱為1路收發器,收發都是差分信號)。四路收發器被稱為一個 Quad GT。

每一路的收發器的內部如下:

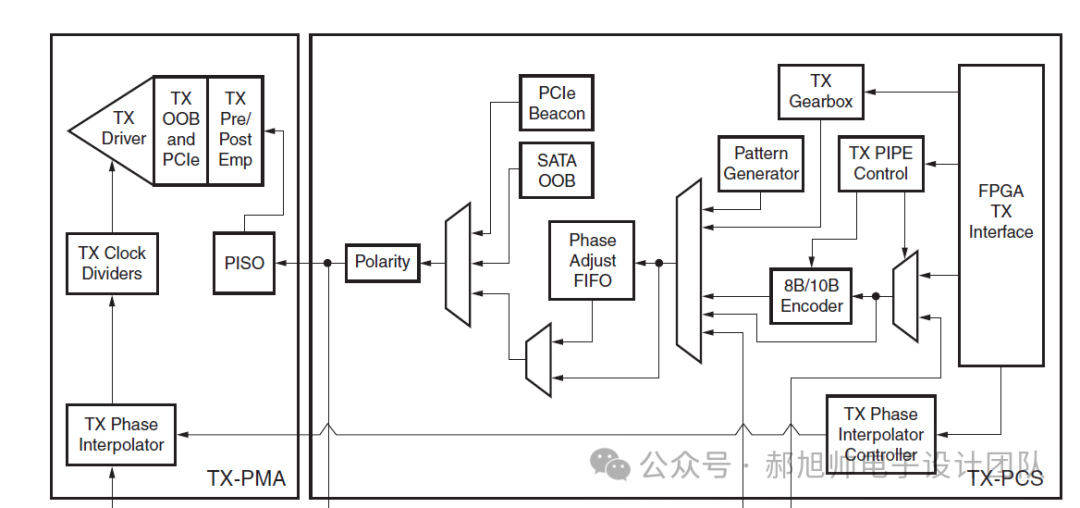

發送器:

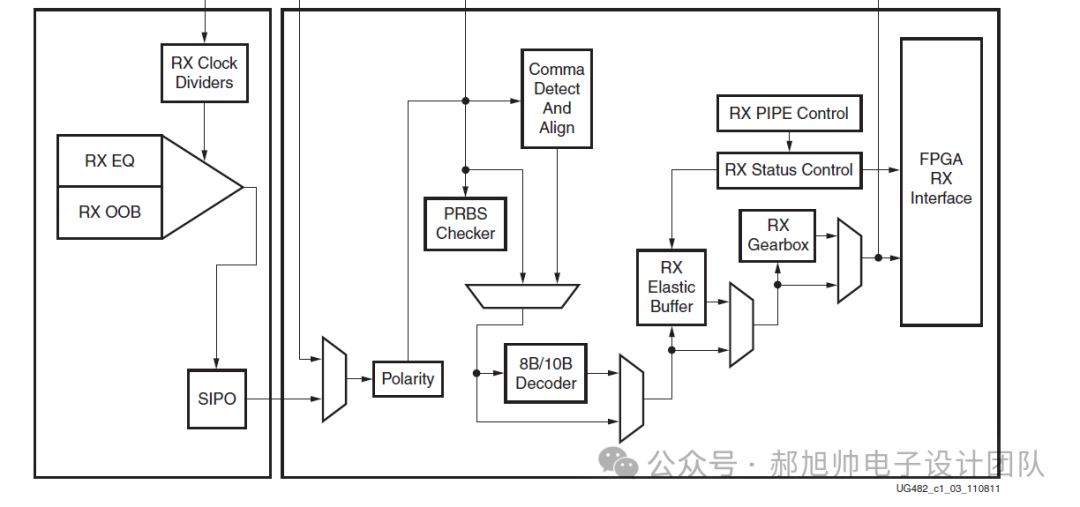

接收器:

在分析發送器和接收器之前,我們先了解幾個名詞。

PMA:

PMA是物理介質子層(Physical Medium Attachment),它負責管理電氣、時鐘和定時等物理層面的信號特性。PMA還處理高速數據傳輸所需的時序控制和信號重建,并確保信號能夠正確地傳輸到遠端接收器。

PCS:

PCS是物理編碼子層(Physical Coding Sublayer),它處理數據信號的編碼和解碼,以及錯誤檢測和校正。PCS負責將邏輯上的數據流轉換為物理層面上的數字信號,并通過使用8b/10b編碼或128b/130b編碼等技術來確保數據傳輸的可靠性和正確性。

發送器和接收器都是由PCS和PMA組成。相對簡化理解:PMA就是發送端并轉串,就是接收端串轉并。

那么此時我們就可以利用PMA來完成高速串行輸入輸出。那么PCS有什么作用呢?

在高速串行通信中,為了能夠使信號完整的發送到發送方、能夠使接收方可以進行CDR,需要對發送的數據進行編碼(如果不明白可以查看本公眾號文章“高速遠距離通信之bit同步和字節同步”)。除了基本的編碼外,我們還需要一些通信協議(PCIE、SATA等等)、多通道對齊等一些功能。此時PCS將可以為我們完成一部分。

在使用GT資源時,我們只需要將原碼(可能附帶一些協議規則)發送給PCS,PCS經過調整后,發送給PMA,PMA就會將數據發送到FPGA外部;外部高速信號進入PMA,PMA將數據交付給PCS,PCS經過調整交付為FPGA內部。此時就完成了高速數據的輸入和輸出的過程。

當然是用起來還是有一定的難度,后續慢慢的介紹相關內容。

-

FPGA

+關注

關注

1629文章

21750瀏覽量

604108 -

觸發器

+關注

關注

14文章

2000瀏覽量

61208 -

串行信號

+關注

關注

0文章

26瀏覽量

8513

原文標題:FPGA如何發出高速串行信號

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

求助FPGA高速串行收發器,輸出12.5Gbps的信號要用什么電平 ...

輕松實現高速串行I/O (FPGA應用設計者指南)

基于FPGA的串行接收模塊的設計

基于FPGA的高速串行傳輸接口研究與實現

通過FPGA實現多種主流高速串行交換模塊研究設計

介紹使用IBERT調試FPGA芯片高速串行接口性能的步驟

如何設計實現Xilinx FPGA高速串行接口

FPGA如何發出高速串行信號

FPGA如何發出高速串行信號

評論