引言

下一個抽象級別建立在事務級建模(TLM)基礎之上。創建TLM IP作為黃金源碼后,設計團隊可簡化IP創建和復用,在功能驗證上節省人力物力,并減少bug。設計迭代減少,原因是TLM驗證比RTL驗證快得多,且架構選擇在RTL驗證進行之前就能得到確定。此外,事務級模型可用于軟硬件協同驗證,并可組成用于早期軟件開發的虛擬平臺的一部分。所有這些優勢將大幅提升設計效率。

TLM通過函數調用而非信號或線路進行模塊間通信。它允許用戶分析讀或寫這些事務,而不用擔心底層邏輯的實現和時序。SystemC是開發可復用、可互用 TLM IP的最佳語言標準。此外,因為SystemC建立在C++基礎上,它還允許對C語言算術函數的完全復用。開放SystemC行動(OSCI)為TLM模型定義了若干抽象層,分別是程序員視角(無定時)模型、寬松定時模型和近似定時模型。

Cadence設計系統公司目前提供一種全面的SystemC TLM驅動式IP設計與驗證解決方案,包括方法學指南、高階綜合、有TLM感知的驗證以及客戶服務,推動用戶向TLM驅動設計與驗證流程轉變。

要求對RTL進行改變的關鍵難題

在RTL中,有限狀態機的結構要進行充分描述。這意味著,在編寫RTL時需關注微架構詳情,如存儲器結構、流水線、控制狀態或最終實現中使用的ALU等。 這一要求導致更長、可復用性更低的設計與驗證流程。

有時當TLM用于當前流程時,現有的基于RTL的流程需要進行兩次設計意圖手工輸入——一次在系統級、一次在RTL級。這種過程粗笨低效且易出錯。架構直至產生RTL后才能確定,而重新確定IP目標成本很高。一個真正的TLM驅動式設計與驗證流程將只需要一次設計意圖簡單的表達,并提供一條自動化的轉換方法。

從RTL開始查找和解決架構問題過程長,代價高

RTL驅動式設計方法學的一大問題是,一種架構是否能實現,直到建立了RTL并對其進行驗證后才能確認。由于RTL是架構的直接表示,大部分RTL設計師不得不同時探究功能正確性、架構和設計目標。這導致很長的周期,始于做出架構決定,終止于驗證功能性。通常,設計與驗證團隊會發現需要修改架構的功能性 bug,每次發現這樣的bug就需要重新開始整個周期。

在RTL上復用IP設計限制了架構靈活性

當今SoC中,可能有高達90%的IP模塊來自以前項目的復用。但是,當IP的黃金源碼為微架構級別時,復用是很困難的。重定RTL IP的微架構目標費力且容易出錯。目標系統應用可能差別很大,意味著不通過重新架構,僅通過簡單復用,新的SoC設計目標是不能達到的。例如,RTL設計師可能需要將設計重新分割成RTL塊、改變流水線級數、或創建新的存儲器架構,因為在原有IP中,這些微架構詳情都是固定和預先決定的。

RTL功能驗證時間比當前技術的最高吞吐量增加得更快

在很多SoC項目中,功能驗證已成為主要瓶頸。RTL功能驗證開始時,在系統級的大量驗證投入已然損失。雖然驗證規劃、指標驅動式驗證等方法使設計團隊尚能應付當前的大部分驗證難題,但時間限制和日益增多的門數正在使驗證變得難以為繼。RTL功能驗證所需時間可能隨設計的增大而呈指數式增長,因為相互作用的各種模式及該IP需要測試的許多軟硬件配置導致了各種極端情形,它們也需要進行驗證。

RTL是有精確時鐘周期的,涉及的代碼行遠多于TLM邏輯。對RTL模型進行仿真時,仿真器檢查所有事件或時鐘周期,即使在協議級上并未發生任何重大情況。仿真器要在微架構詳情上浪費大量機器周期,而這些需要在架構確定后才能確認。TLM仿真在更高抽象級別進行,能更早完成,并提供更高性能。

TLM正是需要的解決方案

TLM驅動的設計和驗證流程可實現在功能級別上描述IP,然后在快速仿真中驗證事務的功能行為。TLM流程的主要優點包括能更快創建設計;減少了黃金源碼中的代碼行;bug更少;表達設計意圖更容易,且僅需一次;更快的仿真和調試;功耗預估可更早進行;支持軟硬件協同驗證;可將模型納入虛擬平臺;RTL生成前可進行架構驗證;在RTL驗證中可復用TLM驗證IP;無需微架構重新設計即可進行IP復用;ECO模式下產生的RTL變化很小。

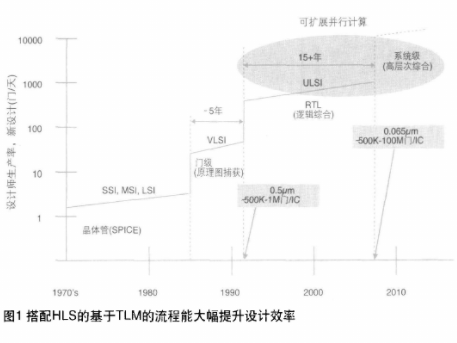

基于TLM的流程與高層次綜合(HLS)配合,可將抽象級別提高。這是大約15年前設計師轉向RTL后的又一次重大轉變,根據之前的經驗,這次轉變有可能使設計效率呈現數量級的提升(見圖1)。

下面幾部分描述了TLM驅動式設計和驗證流程的具體屬性和優勢。

創建TLM作為黃金源碼——更快的IP創建與設計IP復用

與RTL不同的是,TLM不描述最終實現的微架構詳情。不描述微架構詳情大幅提高了TLM設計在要求各不相同的多個項目間的可復用性,因為相同的TLM IP可重新定為不同微架構的RTL代碼。而且,得益于更高的抽象程度,正確地創建功能要容易得多。TLM模型具有的代碼行比對應的RTL模型要少得多,從而在最終設計中實現了編碼效率和品質的同步提高。

開發與維護作為IP模塊黃金源碼的TLM所需的綜合和驗證解決方案,需要產生有品質保證的結果并驗證其正確性,且無須編輯RTL或門級設計。這使設計團隊在TLM環境內就能做出所有決定,并可通過將TLM源碼復用于系統來約束完全不同的其他設計。

SystemC是描述事務級設計的最佳標準,并連接到實現,提供了最好的可復用機會。它可對硬件的并發特性進行建模,并針對進程、管腳、線程和控制邏輯描述定時或非定時的行為。TLM 1.0和2.0標準提供了創建可互用IP模型的能力。最終,需要有一個合格的可綜合TLM IP庫,及可綜合TLM標準(或事實上的)子集。

對TLM IP的功能驗證可應對驗證吞吐量的爆發

TLM IP驗證相對RTL驗證具有很多優勢。首先,仿真運行更快——相對RTL仿真有數量級的提升,從而允許驗證更多功能性實例。同時,在TLM抽象級別上進行的調試比RTL調試更容易、更快速。

通過在更高抽象級別上編碼,TLM IP需要的代碼行更少,bug也更少。功能性bug在設計早期就能被發現和解決。因而可大幅減少驗證工作的總體投入。

在TLM抽象級別上,定位和理解bug更容易,修正bug也更容易,原因是需要處理的詳情更少。TLM流程允許在最合適的抽象級別來驗證各關注重點,如TLM用來驗證功能、信號級驗證用于驗證接口等。

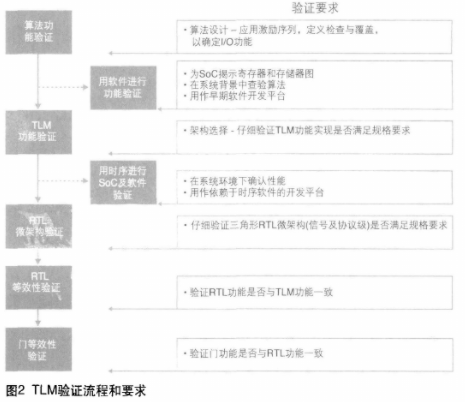

TLM驗證流程始自算法功能驗證,允許用軟件進行功能驗證,然后轉向TLM功能驗證(見圖2)。通過C-to-Silicon Compiler的編譯,用戶可轉向微架構RTL驗證和RTL到門級等效性檢查。除支持仿真很快的非定時建模外,TLM還允許用戶進行改進,逐漸包含微架構詳情,并改進時序精確性。

軟硬件協同驗證及早期軟件開發

TLM模型抽象級別高、執行快,足夠執行切實可行的軟硬件協同仿真。設計師能將嵌入式軟件與TLM硬件模型進行協同仿真,來檢查軟硬件依賴性,并對依賴于硬件的軟件進行早期調試。有可能將這些技術當做對軟硬件交互的隨機化激勵與覆蓋進行應用。

用于早期軟件開發和調試的虛擬平臺可能包含由SystemC TLM模型組成的子系統。得益于它們的快速執行,為創建硬件設計而開發的模型也可用來加速軟件設計。

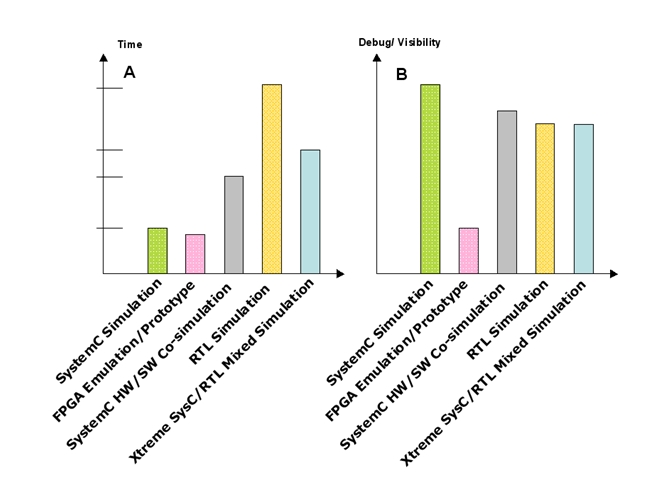

支持TLM和RTL混合驗證

在SoC級別需要TLM和RTL混合功能驗證,是因為有大量將被復用的遺留RTL IP,且仍有必要針對設計各部分進行詳細RTL功能驗證。某些驗證任務將只能在RTL上才能完成,包括針對存儲器存取順序或狀態遷移覆蓋等屬性的微架構結構驗證。

由于大部分驗證工具如驗證計劃(vPlan)、開放驗證方法學(OVM)驗證組件、testbench、序列、測試、檢查和覆蓋等在各種抽象級別都能復用,因此TLM/RTL混合信號驗證也變得更容易實現。功能驗證規劃與管理跨TLM與RTL兩個級別,允許團隊在混合級別設計中的各級別上對驗證進行跟蹤和控制,并在需要時對結果進行整合,確保了整體品質。

用于SystemVerilog的OVM已得到擴充,可支持包括e與SystemC在內的多種語言。OVM庫也支持TLM。目前,OVM方法學描述正在進行擴充,以顯示怎樣在一個綜合性回歸解決方案中整合TLM和RTL模型。這將有助于創建工作于多語言、TLM/RTL混合驗證環境的驗證IP(VIP)。

多級功能驗證testbench基于事務,當它連接到基于RTL的IP、總線或接口時,需要一個事務處理器在事務級域和管腳精確的RTL域之間進行轉換。類似地,需要事務處理器將TLM IP塊連接到RTL IP塊上的總線或接口。基于TLM的方法學必須考慮,這些事務處理器該怎樣工作,以獲得混合TLM/RTL驗證的最大收益。有些事務處理器可通過購買取得,而有些則是專有的,由項目團隊創建,并作為驗證庫組件進行管理。

很多項目實現TLM僅僅是為了新IP,從而逐漸建立起一個TLM IP庫,許多團隊針對新的IP采用了TLM的方法學,并且逐漸豐富TLM IP庫,而有些團隊在事關成敗的關鍵項目中采用了TLM方法學,用于所有重要的IP模塊。最終,SoC的所有IP黃金源碼都來自于TLM級。在這些情況下,品質、效率及容易調試的優點將比TLM/RTL混合項目中更加明顯。SoC TLM功能驗證,包括SoC級架構分析和優化,將可能實現。

從TLM到RTL驗證進行VIP復用

VIP復用現已成為主流,因為創建高質量驗證環境的時間經常超過創建設計IP本身的時間。標準協議的廣泛使用推動了商業VIP市場的快速發展。當前,大部分VIP是寄存器傳輸級的。由TLM得到的VIP也將有一定需求,但必須可復用于TLM/RTL混合功能驗證。

在RTL功能驗證中,使用約束隨機激勵生成的先進testbench占據了主導地位。由TLM得到的VIP在用于TLM、TLM/RTL混合及RTL功能驗證的testbench中應該都是可操作的。這樣的VIP需允許指標驅動式驗證的應用,因為客戶會在驗證抽象的所有級別上使用覆蓋指標。最后,對于和架構及軟件工程團隊工作密切相關的驗證團隊,輔助的嵌入式軟件和定向測試也是必需的。

從算法到微架構的漸進式設計改進

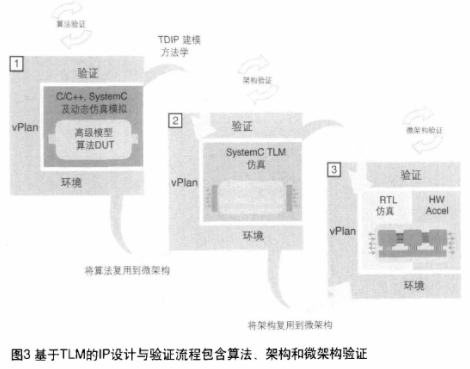

TLM IP設計和驗證流程有若干獨特的步驟:算法驗證、架構驗證、微架構驗證(見圖3)。第一步(算法驗證)可能涉及C++或Matlab或Simulink這樣的產品。用戶可為關鍵算法特性制定一個vPlan,驗證I/O的功能,并為關鍵實例應用激勵序列。

第二步(架構驗證),設計師使用TLM驅動式IP建模(TDIP)方法學來定義架構和接口協議。他們復用算法vPlan,并應用額外的激勵、檢查、斷言與覆蓋,還為關鍵架構和接口協議特性制定vPlan。在第三步(微架構驗證),設計師通過C-to-Silicon Compiler進行綜合,復用算法和架構vPlan,然后推廣至激勵、檢查、斷言與覆蓋中的微架構詳情。

Cadence TLM產品

Cadence TLM驅動式IP設計與驗證解決方案包含方法學指南、C-to-Silicon Compiler、Cadence Incisive功能驗證平臺以及TLM驅動式IP設計與驗證服務。

統一的TLM驅動式IP設計、驗證、復用方法學及編碼指南

Cadence將為TLM驅動式IP設計與驗證提供方法學指南,幫助設計團隊在最短時間內以最高效率啟動和完成他們初始的TLM項目,并避免采用新方法學的常見錯誤。從TLM IP設計編碼風格、建模指南及綜合子集開始,用戶能夠創建TLM IP,其架構利用了高層次綜合所提供的能力。在整個TLM驅動的IP方法學中都考慮了對設計和驗證IP的復用。

C-to-Silicon Compiler利用TLM黃金源碼創建高質量的RTL

C-to-Silicon Compiler是一個高層次綜合產品,它采用TLM SystemC IP描述和約束,并創建可用于標準RTL實現流程的RTL。為確保結果的質量,它利用Cadence Incisive RTL Compiler技術來創建邏輯,并提取該邏輯的時序與功耗信息來決定最終RTL的架構詳情。

C-to-Silicon Compiler GUI顯示了原始SystemC和根據它生成的RTL代碼行之間的對應關系。這種獨特的對照功能鼓勵系統設計師和RTL設計師之間的溝通,并有助于保持 SystemC TLM作為黃金源碼。它還將調試提升到更高的抽象水平,并使設計師可以評估SystemC源碼的變化對RTL產生的影響。

C-to-Silicon Compiler提供了增量綜合能力,可大幅簡化工程更改(ECO)過程并盡可能減少對RTL代碼的更改。其他大多數HLS工具都要求對整個算法進行重新綜合,意味著源代碼中的微小變化也會導致完全不同的RTL。在這些情形下,必須重做邏輯綜合和RTL驗證。因而很難將SystemC代碼保持為黃金源碼。相比之下,C-to-Silicon Compiler僅對算法的改變部分生成RTL代碼,而不修改設計的其他部分。

C-to-Silicon Compiler能通過應用新約束,生成新RTL,將TLM設計IP轉移到新的微架構目標。通過指定不同時序、面積和功耗約束或不同微架構指導如流水線級數,就能生成新的RTL。這樣,設計團隊就能重復利用IP,且人力投入更少,RTL質量更高,時間更少。通過嘗試不同微架構,設計師還可運行假設實驗。

最后,C-to-Silicon Compiler能自動生成周期準確的SystemC快速硬件模型(Fast Hardware Models, FHM),能以非定時TLM模型的80%~90%的速度執行。這些SystemC模型允許早期快速驗證和軟硬件協同開發。FHM配有來自Cadence Incisive環境的擴展,使變量和信號的顯示更加明顯,以方便分析和調試。

Incisive指標驅動式從TLM到收斂驗證解決方案

Cadence Incisive功能驗證平臺是完全集成化的多語言、多級別功能驗證解決方案。利用指標驅動式驗證、專注于硬件的定向測試、軟件定向測試或軟硬件協同驗證,Cadence Incisive Enterprise Simulator可完整驗證符合OSCI TLM 2.0的設計IP。

特別設計的事務級分析和統一的調試特性有助于TLM IP的創建和驗證,無論設計是完整的TLM IP或僅僅是遺留RTL SoC中的一個TLM IP模塊。Incisive Enterprise Simulator在其調試環境中自動識別TLM 2.0構件,可提供保存/重啟及重置功能,并針對SystemC/C++進行了擴展。該仿真器可推斷事務信息,并提供有可感知TLM控制、可見性和調試特性。通過事務級的控制和調試操作,用戶能夠調試SystemC TLM 2.0設計中的所有互動元素。

通過Cadence Incisive Software Extensions,設計師能夠運行嵌入式軟件的處理器模型和TLM硬件模型的協同仿真。Incisive Software Extensions使驗證testbench可使用在處理器模型下運行的軟件、并為軟硬件協同仿真提供了指標驅動式驗證、偽隨機測試生成、驗證覆蓋等功能。

Cadence Incisive Enterprise Manager提供了TLM、TLM/RTL與RTL功能驗證技術,以成功獲得收斂。對于具有大規模RTL遺留IP的SoC,使用Cadence Incisive Palladium或Cadence Incisive Xtreme,可用快速RTL檢驗對TLM仿真進行補充。這些硬件平臺所允許的周期精確驗證的運行速度,也能允許低階軟件驗證的運行。

幫助規劃和實施項目關鍵更改的服務

一次一個IP模塊地過渡到TLM驅動式設計與驗證,能降低一些風險和成本。但是,有些項目必須進一步減少風險,并借助豐富經驗的幫助,來規劃、執行并擴大最優方法驗證。Cadence在全球都可提供TLM驅動式設計和驗證的專家服務,以擴大成功機率,減少運行時間、人力投入和風險。

結語

TLM驅動式設計與驗證將最終使TLM取代RTL作為大多數設計組件的黃金源碼。其優勢是明顯的——快得多的設計與驗證時間、IP復用更容易、bug更少。工作效率將實現RTL設計出現以來的最大跨越。但這一過渡不可能一蹴而就。TLM驅動式設計和驗證方法在新IP被創建出來時,一次運行一個IP模塊。而有些設計組件直接以RTL形式設計將是最好的方式。因此,必然要有將新TLM IP與遺留的RTL IP在設計與驗證環境中進行合并的可能。

通過提供方法學指南、高層次綜合、有TLM感知的驗證和調試及采用服務,Cadence將提供幫助,使RTL到TLM驅動式設計和驗證方法學的過渡更容易。

責任編輯:gt

-

接口

+關注

關注

33文章

8685瀏覽量

151655 -

IP

+關注

關注

5文章

1715瀏覽量

149797 -

總線

+關注

關注

10文章

2899瀏覽量

88274

發布評論請先 登錄

相關推薦

如何在ModelSim下用SystemC的做驗證?

AMBA-PV TLM擴展用戶指南

用SystemC進行SoC的系統級設計與仿真

基于SystemC的系統驗證研究和應用

Cadence推出首個TLM驅動式設計與驗證解決方案

Cadence推出首個TLM驅動式設計與驗證解決方案提升基于

利用基于SystemC/TLM的方法學進行IP開發和FPGA

Cadence推出15種新驗證 IP(VIP)解決方案

新思科技設計、驗證和IP解決方案助力Arm全面計算戰略

思爾芯系統級驗證原型解決方案助力BLE Audio領域的IP/藍牙SoC快速設計

SystemC TLM中的接口

新思科技PCIe 7.0驗證IP(VIP)的特性

全面的SystemC TLM驅動式IP設計與驗證解決方案

全面的SystemC TLM驅動式IP設計與驗證解決方案

評論