目前在一些彈載設備中,由于采集的實時圖像數據量很大,因此在其與地面測試臺進行數據傳輸時需要很高的傳輸速率。傳統的圖像數據傳輸方法存在很大的局限性。比如,物理層接口無法滿足數據的傳輸速度;由于傳輸通道的增多引起傳輸導線數量的增加導致系統功耗、噪聲也隨之增大等。低電壓差分信號傳輸技術(LVDS)為解決這一問題提供了可能。

1 LVDS技術簡介

LVDS技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等特點,其傳輸介質可以是銅質的PCB連線,也可以是平衡電纜。LVDS在對信號完整性、低抖動及共模特性要求較高的系統中得到了越來越廣泛的應用。

圖1為LVDS器件單工通信基本原理框圖。它由一個驅動器、差分互連單元和一個接收器組成。驅動器和接收器主要完成信號電平和傳輸方式轉換,它不依賴于特定的供電電壓,很容易遷移到低壓供電的系統中去,而性能不變。互連單元包含電纜、PCB上差分導線對以及匹配電阻。

2 系統總體方案設計

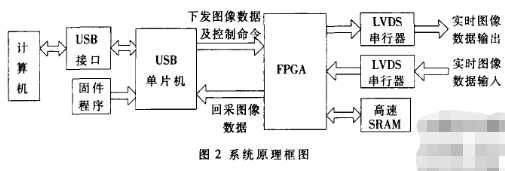

系統采用USB接口電路實現計算機與FPGA的數據傳輸,以LVDS串行器與解串器構建實時圖像的發送與接收電路。系統的原理框圖如圖2所示。

系統的工作原理為:計算機將控制命令及實時圖像數據經由USB接口發送給FPGA,FPGA將實時圖像數據部分存儲到高速SRAM,然后根據控制命令將SRAM中數據傳送給LVDS串行器;另外,FPGA還需將回讀的實時圖像數據以20 MB/s的速度經由USB接口發送給計算機進行處理。

3 系統結構組成及其實現

3.1 USB接口實現

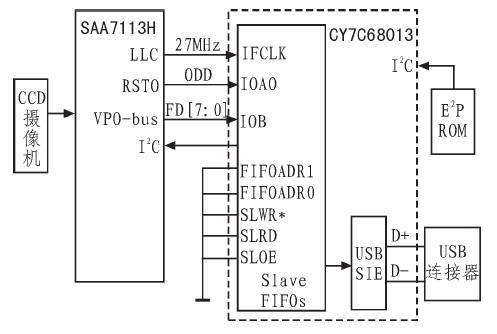

本系統所使用的USB單片機選用Cypress公司開發的EZ-USB FX2芯片CY7C68013。該芯片集成了51單片機內核、USB2.0收發器、串行接口引擎(SIE)、4 KBFIFO存儲器以及通用可編程接口等模塊,這些模塊則保證了CY7C68013可與外圍器件實現無縫的、高速的數據傳輸。用戶在使用該單片機與外圍設備進行數據傳輸時,只需直接利用GPIF接口來實現與外圍設備之間的邏輯連接,就可以進行高速數據的傳輸。CY7C68013的GPIF接口有16位數據線,6個RDY信號和6個CTL信號。其中RDY信號為等待信號,GPIF可連續采樣RDY信號。通常用來等待指定信號的某個狀態出現,以確定GPIF下一步動作。CTL信號為控制輸出信號。通常用作選通信號、非總線輸出信號以及產生簡單的脈沖信號。 CY7C68013在高速模式下,發送數據的碼率可達到480 Mb/s,因此可將20 MB/s的實時圖像數據實時地傳送給計算機。

本系統的USB傳輸部分主要實現將計算機發出的控制命令及實時圖像數據發送給FPGA,并將回讀的實時圖像數據發送給計算機。計算機發送的命令信號通過CY7C68013的PE端口傳送給FPGA,實時圖像數據通過CY7C68013的GPIF接口發送給FPGA或上傳給計算機。由于USB與FPGA的傳輸速度不一致,所以還應在FPGA中設置兩個軟FIFO,分別用于圖像數據的上傳與下發。

3.2 LVDS數據發送與接收部分

本系統采用美國TI公司的10位總線型LVDS芯片SN65LV1023A和SN65LV1224A實現實時圖像的高速數據傳輸和回采。兩者發送和接收10 bit并行數據的速率在10 MHz~60 MHz之間。由于數據在并串轉換時,SN65LV1023A會自動加上1位起始位和1位停止位,則串行數據發送的實際速率為120 Mb/s~792 Mb/s之間。LVDS串行器和解串器都需一個外部時鐘。只有這兩個外部時鐘頻率同步時,串行器和解串器才能正常通信。利用FPGA內部時序邏輯,完全能夠解決工作時鐘頻率同步的問題。[page]

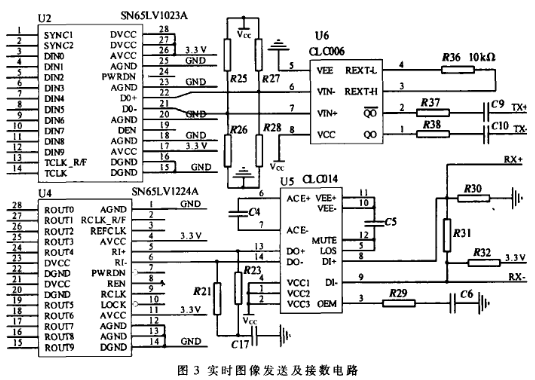

實時圖像發送及接收電路如圖3所示。FPGA根據計算機控制命令先從高速SRAM中讀取1 B的數據,然后的將該字節外加兩位的識別位共10位的并行實時圖像數據輸出到SN65LV1023A,再將轉化后的高速串行差分信號經高速電纜驅動器CLC006驅動后遠程傳輸。CLC006能在最高400 Mb/s數據速率下驅動75 Ω傳輸線,還具有可控的輸出信號上升沿和下降沿時間,能使傳輸引入的抖動最小。通過調整R25/R27和R26/R28的阻值為驅動器提供正常輸入信號。其值大小參考芯片資料接口連接部分選擇,它隨其輸入電平類型及阻抗傳輸線而改變。驅動器的信號輸出幅度隨著Rext-H與Rext-L間電阻值的增大而增大。為了實現信號的最優化傳輸,將Rext-H與Rext-L之間電阻R36接為10 k?贅的可調電阻,根據實際情況調節R36阻值實現輸出信號幅度范圍的調整。

由于傳輸線對信號有損耗,而且容易產生信號失真、畸變和碼元串擾等,本系統采用了自適應電纜均衡器CLC014對遠程傳輸后接收到的數據進行均衡。CLC014具有同軸電纜和雙絞線的自動均衡、載波檢測與輸出靜音功能,適用數據速率范圍為50 Mb/s~650 Mb/s,且具有極低的抖動性能。

LVDS接收器在內部雖然提供了針對輸入懸空、輸入短路以及輸入不匹配等情況下的可靠性設計,但是當驅動器三態或LVDS接收器沒有連接到驅動器上時,連接電纜會產生天線效應,此時LVDS接收器就有可能開關或振蕩。為避免此種情況的發生,傳輸電纜采用雙絞屏蔽電纜;另外在電路設計上外加上拉和下拉電阻來提高LVDS接收器的噪聲容限。圖3中的R31為100 Ω的匹配電阻,R32和R30分別為提高噪聲容限的上拉和下拉電阻,阻值為1.5 kΩ。

FPGA主要通過控制LVDS串行器的TCLK、TCLK_R/F引腳以及LVDS解串器的RCLK、RCLK_R/F引腳實現數據的發送與接收。具體實現方法為:TCLK、RCLK引腳由FPGA分配同一時鐘(時鐘頻率為20 MHz),在時鐘的上升沿,FPGA先將從高速SRAM中讀取的1 B的數據發送出去,另外在FPGA接收到1 B的數據后,先將其存入內部FIFO中,當FIFO中的數據達到512 B后通知USB單片機讀取數據,然后發送到計算機。

4 實驗結果

圖4與圖5分別為系統以20 MB/s的速度發送和接收的一幀512×512 B(每字節表示一個像素點)圖像數據,分析結果表明發送與接收的圖像數據完全一致,滿足系統的設計要求。

采用LVDS技術與FPGA相結合的方法,實現了彈載圖像采集設備與地面測試臺之間高速數據傳輸,系統的傳輸速率可達到20 MB/s,并且提高了系統的可靠性和集成度。另外,整個系統的時序均由FPGA控制實現,具有很強的重構性。本設計已成功應用于某CCD圖像采集設備的測試中,系統工作性能穩定。

責任編輯:gt

-

芯片

+關注

關注

456文章

51121瀏覽量

426016 -

接收器

+關注

關注

14文章

2478瀏覽量

72082 -

lvds

+關注

關注

2文章

1045瀏覽量

65931

發布評論請先 登錄

相關推薦

如何采用CY7C68013芯片設計圖像采集系統

CY7C68013 與labview通信錯誤

哪個CY7C68013的芯片方便與GPIF接觸?

cy7c68013開發包及驅動

基于CY7C68013的USB數據采集系統

基于CY7C68013的CCD圖像傳輸系統

基于CY7C68013的高速數據通信接口設計

CY7C68013的固件程序開發方法

基于CY7C68013芯片和LVDS技術實現圖像采集系統的設計

基于CY7C68013芯片和LVDS技術實現圖像采集系統的設計

評論