第一代半導體材料一般是指硅(Si)元素和鍺(Ge)元素,其奠定了20 世紀電子工業的基礎。第二代半導體材料主要指化合物半導體材料,如砷化鎵(GaAs)、磷化銦(InP)、磷化鎵(GaP)、砷化銦(InAs)、砷化鋁(AlAs)及其合金化合物等,其奠定了20 世紀信息光電產業的基礎。第三代寬禁帶半導體材料一般是指氮化鎵(GaN)、碳化硅(SiC)、氮化鋁(AlN)、金剛石等材料,其具有禁帶寬度大、抗輻射能力強、擊穿電場強度好、耐高溫等特點,可以克服傳統半導體的劣勢,能夠使設備在極端惡劣的條件下正常工作。因此,寬禁帶半導體的材料可以在微電子領域發揮重要的作用,具有廣闊的應用市場。

禁帶寬度是半導體的一個重要特性參數,根據半導體材料的能帶結構不同,可將半導體材料分成兩種類型:寬禁帶和窄禁帶。若半導體材料的帶隙寬度小于2.3eV,則稱為窄帶隙半導體,代表性材料有GaAs、Si、Ge 和InP ;若半導體材料的帶隙寬度大于或等于2.3eV,則稱為寬帶隙半導體,代表性材料有GaN、SiC、AlN 和氮化鋁鎵(AlGaN)等。半導體材料的禁帶寬度越大,意味著其電子躍遷到導帶所需的能量越大,從而材料能承受的溫度和電壓越高,即越不容易成為導體。

寬禁帶半導體材料非常適合于制作抗輻射、高頻、大功率和高密度集成的電子器件,其具有良好的抗輻射能力及化學穩定性、較高的飽和電子漂移速度及導熱率、優異的電性能等特點。近年來,迅速發展起來的以GaN、SiC 為代表的寬禁帶半導體材料是固態光源和電力電子、微波射頻器件的“核芯”,在半導體照明、新一代移動通信、智能電網、高速軌道交通、新能源汽車、消費類電子等領域具有廣闊的應用前景,可望成為支撐信息、能源、交通、國防等產業發展的重點新材料,進行寬禁帶半導體材料的相關技術研發正在成為全球半導體產業新的戰略高地。SiC 與GaN 是第三代寬禁帶半導體材料中發展比較成熟的材料,本文主要研究這兩類材料。

SiC材料及其制備工藝

SiC 具有獨特的物理和電學特性,其可以通過熱氧化工藝制備出SiO2,同時在氧化過程中使C 元素以氣體的形式釋放,制備出高質量的SiO2,進而可利用SiC 制作性能優良的金屬– 氧化物– 半導體(Metal-Oxide-Semiconductor,MOS)晶體管。

(一)SiC 材料結構及特性

SiC 為Ⅳ主族中Si 元素和C 元素組成的化合物,C 原子和Si 原子以共價鍵的形式連接。SiC 的基本結構單元是硅碳四面體,其相互連接形成各種緊密堆積的結構。Si—C 雙原子層的堆積順序不同,導致SiC具有多種晶體結構。其中,SiC 的同態多晶型主要有閃鋅礦(Zincblende)結構、纖鋅礦(Wurtzite)結構和菱形(Diamond)結構。SiC 的纖鋅礦結構為α-SiC,SiC 的立方閃鋅礦結構為β-SiC,根據晶體堆疊的不同呈現出多型結構,其中β-SiC(3C-SiC)和α-SiC(2H-SiC、4H-SiC、6H-SiC、15R-SiC)比較具有代表性,對于不同的晶體結構,其禁帶寬度也有所差異,如圖1 所示。

圖1 SiC材料的常見多型結構(a)SiC材料的晶體結構;(b)對應的禁帶寬度

在SiC 的各種晶體類型中,3C-SiC 鍵能最低,晶格自由能最高且易成核,但其處于亞穩態,具有較低的穩定性及易發生固相轉移的特點。在接近平衡態的條件下,當退火溫度分別為1200℃和2000℃時,3C-SiC 會發生相變,部分轉變為6H-SiC 和4H-SiC,其中3 種晶型的鍵能大小順序為3C-SiC<6H-SiC< 4H-SiC,鍵能越小越不穩定,在外界條件影響下越容易發生相變。所以,通過改變外界條件,3C-SiC 可以發生相轉變,變成其他晶型。目前,應用較多的是4H-SiC 材料,其禁帶寬度為3.2eV,是Si 禁帶寬度的3 倍左右,且熱導率高,故多用于高溫大功率的微電子器件領域。

(二)SiC 晶體的制備

圖2(a)為SiC 相圖,可以看出,在大氣氛圍中SiC 在2830℃下會分解為C 和含C 量為13% 的Si 熔液,因此無法從Si-C熔融體中進行晶體生長。在過去的30 年中,工業界已研發出采用升華的方式制備SiC 襯底的技術,使SiC 材料在低壓惰性環境中升華,Si、SiC2、Si2C 等分子沿溫度梯度遷移,并按照設計取向在單晶SiC 種子層上沉積而重新結晶成SiC 晶體,如圖2(b)所示。采用新的物理氣相傳輸(PVT)技術能夠將晶體制備溫度控制在1900~2400℃范圍內。

圖2 SiC的相圖(a)和制備SiC的物理氣相傳輸(PVT)技術(b)

SiC 存在各種多型體(結晶多系),它們的物性值也各不相同。SiC 晶體中存在多種缺陷,這些缺陷會降低其自身的質量。常見的晶體缺陷類型有微管、位錯、層錯、夾雜、多型共生等,如圖3 所示。晶體缺陷給SiC 器件的應用造成了很大的阻礙。在這些缺陷當中,微管缺陷帶來的后果最嚴重,SiC 器件的工作區域中任一微管缺陷都可能會導致器件的失效。

圖3 常見的SiC晶體缺陷類型

雖然一些電子元器件能夠在不使用外延層的情況下直接在襯底材料上制備,但高品質的SiC 器件仍然需要利用高品質的外延材料制備有源區。因此,低缺陷的SiC 外延生長技術對SiC器件質量有著重要的影響。隨著SiC 功率器件制造要求和耐壓等級的不斷提高,其外延材料不斷向低缺陷、厚外延方向發展。目前,批量生產SiC 外延材料的產業化公司有美國的CREE、Dow Corning,日本昭和電工(Showa Denko)等。

GaN材料及其制備工藝

在理論上,GaN 材料的擊穿電場強度(約3×106V/cm)與SiC 材料接近,但受半導體工藝、材料晶格失配等因素影響,GaN 器件的電壓耐受能力通常在1000V 左右,安全使用電壓通常在650V 以下。隨著各項技術難點的攻克和先進工藝的開發,GaN 必將作為新一代高效電源器件的制備材料。

(一)GaN 材料結構及特性

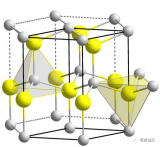

GaN 是Ⅲ-V 族直接帶隙寬禁帶半導體,室溫下纖鋅礦結構的禁帶寬度為3.26eV。GaN 有3 種晶體結構形式,分別為纖鋅礦結構、閃鋅礦結構和巖鹽礦(Rocksalt)結構。其中,纖鋅礦結構是Ⅲ族氮化物中最穩定的晶體結構,閃鋅礦結構以亞穩相形式存在,而巖鹽礦結構是在高壓條件下產生的。纖鋅礦結構的GaN 材料具有其他半導體所不具備的優異物理性能,如耐化學穩定性、超強硬度、超高熔點等,所以,GaN 基半導體器件具有優異的耐壓、耐熱、耐腐蝕特性。圖4 為GaN 的六方纖鋅礦結構和GaN 單晶。

圖4 GaN的六方纖鋅礦結構(a)與GaN單晶(b)

(二)GaN 晶體的制備

GaN 的共價鍵鍵能較大(E=876.9kJ/mol),在2500℃熔點下,分解壓大約為4.5GPa, 當分解壓低于4.5GPa 時,GaN 不熔化直接分解。所以一些典型的平衡方法(如提拉法和布里奇曼定向凝固法等),不再適用于GaN 單晶的生長。目前,只能采用一些特殊的方法來制備單晶,主要包括升華法、高溫高壓法、熔融結晶法和氫化物氣相外延法。其中,前3 種方法對設備和工藝都有嚴格要求,難以實現大規模的單晶生產,不能滿足商業化的要求,而氫化物氣相外延(Hydride Vapor-phaseEpitaxy,HVPE)方法是目前研究的主流。大多數可以商業化方式提供GaN 的均勻襯底都是通過這種方法生產的。該技術具有設備簡單、成本低、發展速度快等優點。利用金屬有機化合物化學氣相沉淀(Metal-organic Chemical Vapor Deposition,MOCVD)技術可以生長出均勻、大尺寸的厚膜作為襯底。目前,該技術已經成為制備外延厚膜最有效的方法,并且生長的厚膜可以通過拋光或激光剝離襯底,作為同質外延生長器件結構的襯底。

氫化物氣相外延層的位錯密度隨外延層厚度的增加而減小,因此,只要外延層的厚度達到一定值,就可以提高晶體質量。通過HVPE 和空隙輔助分離法(Void-assisted Separation,VAS)可以制備具有高晶體質量和良好再現性的大直徑獨立GaN 晶片,如圖5所示。采用表面覆蓋氮化鈦(TiN )納米網的多孔GaN 模板,通過HVPE 生長了厚GaN 層,在 HVPE 生長過程中,這種生長技術在 GaN層和模板之間產生了許多小空隙,當GaN層在生長以后容易與模板分開,并且獲得獨立的GaN 晶片,這些晶片直徑較大,表面呈鏡面狀,無裂縫,位錯密度低。

圖5 HVPE+VAS法制備具有高晶體質量和大直徑獨立的GaN 晶片

此外,可以采用MOCVD-GaN / 藍寶石襯底預處理工藝來制備GaN 厚膜。主要過程為采用等離子體化學氣相沉積法在MOCVD-GaN/ 藍寶石襯底上沉積一層厚度約500nm 的SiO2,然后用電子蒸氣機在襯底上蒸鍍和鍛造一層厚度約20nm 的Ti。退火后在SiO2 表面形成自組裝的Ni 納米團簇,作為光刻掩模。光刻后,將基體置于熱HNO3 和氧化腐蝕劑中。去除Ti 和SiO2 后,通過反應離子刻蝕技術沉積一層SiO2,去除表面的SiO2,形成一層SiO2 包裹在邊緣的GaN 納米柱。最后用HVPE 法在表面生長GaN,在冷卻過程中,GaN 發生自剝離。圖6 為HVPE 和納米簇自剝離技術制備GaN 單晶的過程示意圖。

圖6 HVPE+納米簇自剝離技術制備GaN單晶

上述方法不僅可以實現襯底的自剝離,而且可以形成一種特殊的結構,可以緩沖晶體的生長速度,從而提高晶體的質量,減少內部缺陷。但這些預處理方法相對復雜,會浪費大量時間,并且增加GaN 單晶的成本。

(三)GaN 異質襯底外延技術

由于GaN 在高溫生長時N 的離解壓很高,很難得到大尺寸的GaN 單晶材料,因此,制備異質襯底上的外延GaN 膜已成為研究GaN 材料和器件的主要手段。目前,GaN的外延生長方法有:HVPE、分子束外延(MBE)、原子束外延(ALE)和MOCVD。其中,MOCVD 是最廣泛使用的方法之一。

當前,大多數商業器件是基于異質外延的,主要襯底是藍寶石、AlN、SiC 和Si。但是,這些基板和材料之間的晶格失配和熱失配非常大。因此,外延材料中存在較大的應力和較高的位錯密度,不利于器件性能的提高。圖7 為襯底材料的晶格失配和熱失配關系示意圖。

圖7 襯底材料的晶格失配和熱失配關系

1. SiC 襯底上GaN 基異質結構的外延生長

由于SiC 的熱導率遠遠高于GaN、Si和藍寶石,所以SiC 與GaN 的晶格失配很小。SiC 襯底可以改善器件的散熱特性,降低器件的結溫。但GaN 和SiC 的潤濕性較差,在SiC 襯底上直接生長GaN 很難獲得光滑的膜。AlN 在SiC 基體上的遷移活性小,與SiC 基體的潤濕性好。因此,通常在SiC 基板上用AlN 作為GaN 外延薄膜的成核層,如圖8 所示。許多研究表明,通過優化AlN 成核層的生長條件可以改善CaN 薄膜的晶體質量。但生長在GaN 成核層上的GaN 薄膜仍然存在較大的位錯密度和殘余應力。AlN的熱膨脹系數遠大于GaN,在AlN 上生長的GaN 薄膜在冷卻過程中存在較大的殘余拉應力。拉伸應力會在一定程度上積累,并以裂紋的形式釋放應力。另外,AlN 的遷移活性較低,難以形成連續的膜,導致在AlN 上生長的GaN 薄膜位錯密度較大。GaN 薄膜中的裂紋和位錯會導致器件性能下降甚至失效。由于晶格失配較小,一旦潤濕層和裂紋問題得到解決,SiC 襯底上的GaN 晶體質量要優于Si 和藍寶石襯底上的GaN晶體,因此,SiC 襯底上的GaN 異質結構2DEG 的輸運性能更好。

圖8 AlN作為過渡層的微觀形貌

2. Si 襯底上GaN 基異質結構的外延生長

目前,GaN 基電力電子器件的成本與Si 器件相比仍然非常昂貴。解決成本問題的唯一途徑是利用Si 襯底外延制備GaN 基異質結構,然后利用互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor,CMOS)技術制備GaN 基器件,使器件的性價比超過Si 器件。但與SiC 和藍寶石襯底相比,Si 襯底外延GaN 要難得多。GaN(0001)與Si(111)的晶格失配率高達16.9%,熱膨脹系數失配(熱失配)高達56%。因此,Si 襯底上GaN 的外延生長及其異質結構在應力控制和缺陷控制方面面臨著嚴峻的挑戰。

外延層材料的晶格常數差異,會導致Si 和GaN 外延層界面處的高密度位錯缺陷。在外延生長過程中,大多數位錯會穿透外延層,嚴重影響著外延層的晶體質量。但由于兩層熱膨脹系數不一致,高溫生長后冷卻過程中整個外延層的內應力積累很大,發生翹曲并導致外延層開裂。隨著襯底尺寸的增大,這種翹曲和開裂現象會越來越明顯。

目前,插入層和緩沖層被廣泛應用于解決Si 襯底上GaN 異質外延的應力問題,目前主流的3 種應力調節方案如圖9 所示。

圖9 目前主流的3種應力調節方案(a)低溫AlN插入層結構;(b)GaN/AlN超晶格結構;(c)AlGaN緩沖層結構

插入層技術是引入一個或多個薄層插入層來調節外延層的內應力狀態,平衡在冷卻過程中由熱失配和晶格失配引起的外延層的拉應力,目前采用低溫AlN 作為插入層來調節應力狀態,如圖9(a)所示。

緩沖層技術提供了壓縮應力來調整外延膜中的應力平衡,目前常用的是AlGaN 梯度緩沖和AlN/(Al)GaN 超晶格緩沖,如圖9(b)、(c) 所示。上述方法都能提供壓應力來平衡Si 基GaN 的拉應力,使整個系統趨于應力平衡。當然,這些方法不能完全解決應力問題。緩沖層的應力調節機制尚不明確,有待于進一步探索和優化。

另外,還有報道采用表面活化鍵合(SAB)的低溫鍵合工藝將GaN 層轉移到SiC 和Si 襯底上,在室溫下直接鍵合制備GaN-on-Si 結構和GaN-on-SiC 結構, 通過氬(Ar)離子束源對晶圓表面進行活化。在表面活化后,兩片晶圓將被結合在一起。與Al2O3(藍寶石)和SiC 襯底上生長的異質外延層的質量相比,Si 襯底上GaN 基異質結構的質量和電性能仍有很大差異。特別是Si 襯底上GaN 外延層存在殘余應力和局域陷阱態。這些應力和缺陷控制問題沒有從根本上得到解決,導致材料和器件的可靠性問題尤為突出。因此,如何在高質量的Si 襯底上制備GaN 基異質結構仍是該領域的核心問題之一。

結束語

高頻、大功率、抗輻射、高密度集成寬禁帶半導體電子器件的研制,需要優良的材料作基礎支撐。高品質的SiC和GaN 器件需要利用外延材料制備有源區,因此,低缺陷襯底和高質量外延層對器件性能起著至關重要的作用。近年來,SiC 和GaN功率器件的制造要求和耐壓等級不斷提高,對襯底和異質結構(GaN-on-SiC、GaN-on-Si)的缺陷密度及外延薄膜內部的應力平衡狀態都提出了更高的要求,目前通過利用AlN 作為過渡層、超晶格緩沖層等提供壓應力,進而調節外延層的內部應力以平衡狀態,未來對應力調控尚有大量的工作需要進行探索和優化。

-

半導體

+關注

關注

334文章

27644瀏覽量

221211 -

SiC

+關注

關注

29文章

2868瀏覽量

62815 -

GaN

+關注

關注

19文章

1956瀏覽量

73896

發布評論請先 登錄

相關推薦

第三代半導體對防震基座需求前景?

第三代半導體和半導體區別

什么是SiC功率器件?它有哪些應用?

德高化成第三代半導體GaN倒裝芯片LED封裝制造擴產項目正式開工

一、二、三代半導體的區別

第三代寬禁帶半導體材料SiC和GaN研究

第三代寬禁帶半導體材料SiC和GaN研究

評論