米爾XCZU3EG系列開發板MYD-CZU3EG以超高性能著稱,下面用這款板子做一個演示。

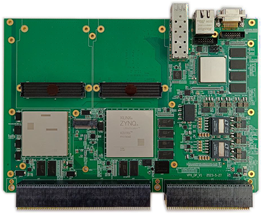

開發環境:vivado 2017.4,開發板型號:米爾MYD-CZU3EG, 主芯片XCZU3EG-1SFVC784。這個系列板子還有4EV,5EV等版本,手里的3EG版本不支持SFP,因此板上相應接口(白色部分)是空貼的。

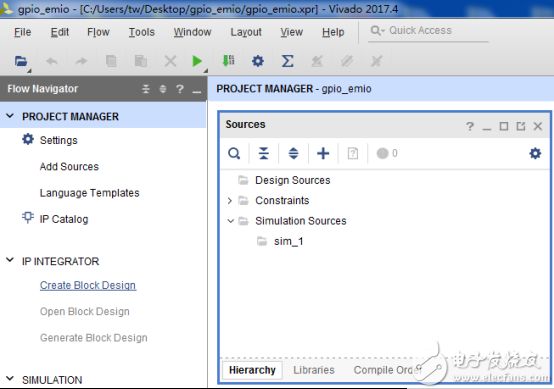

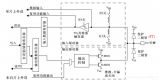

生成的vivado工程(如果不知道如何生成可以參考前面的工程)

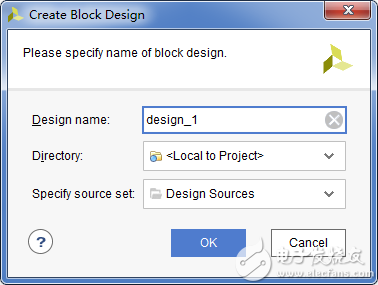

Step1新建Block Design

點擊OK

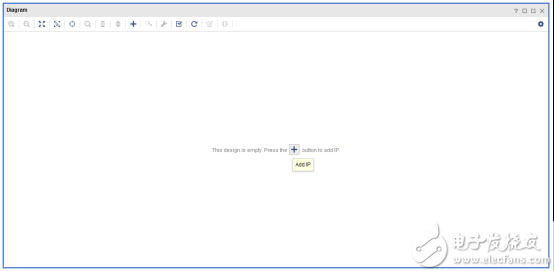

Step2添加PS的IP核并配置

點擊這個Add IP添加IP核

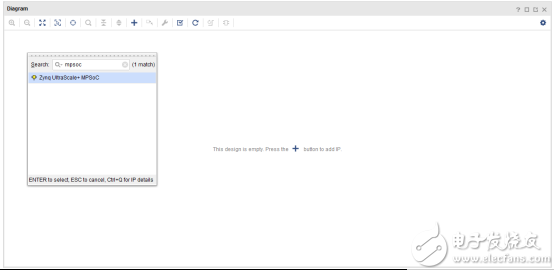

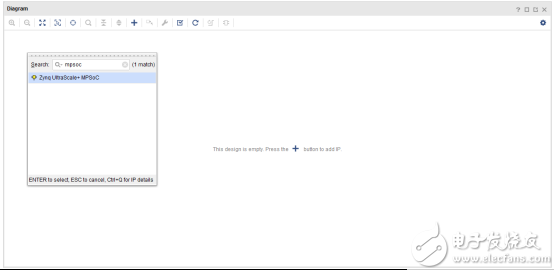

輸入mpsoc,然后雙擊Zynq UltraScale+MPSoC添加mpsoc核

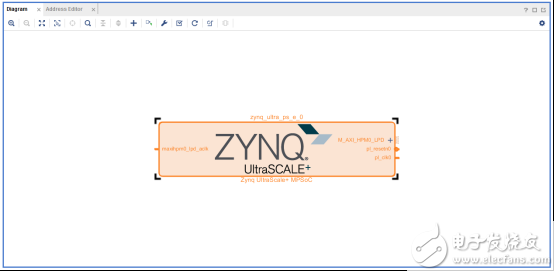

zynq mpsoc核如下圖所示

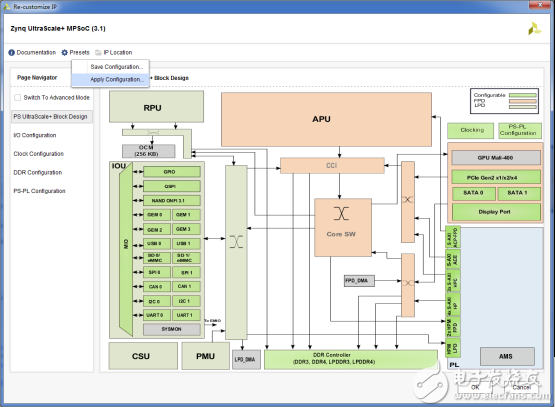

雙擊zynq mpsoc核導入配置文件

Presets-->Apply Configuration

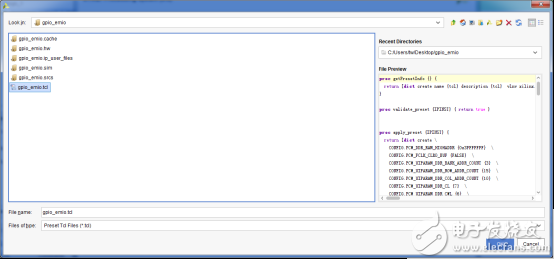

這里導入的是gpio_emio.tcl配置文件

配置完成后,如下圖所示

在gpio管腳上右擊選擇Make External,引出的gpio管腳如下圖所示

……

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

發布評論請先 登錄

相關推薦

高速圖像處理卡設計原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

C6678信號處理板 , FPGA 信號處理 , FPGA開發平臺 , XC7Z045板卡 , XCZU15EG板卡

DAC38J84EVM SYNC信號無法通過FMC-LHC接口輸入到FPGA,怎么解決?

我在使用一塊第三方的alinx xczu9eg ultrascale+mpsoc開發板進行基于JESD204B的DA開發.

我現在使用的FMC子板是DAC38J84EVM , 其中DAC芯片的同步

發表于 11-26 06:43

SOC GPIO操作

sapphire Soc提供了兩個GPIO組每組有4個GPIO,定義為GPIO[3:0],其中只有GPIO[1:0]可以支持中斷。中斷在程序

全志模塊設備開發之GPIO編程基礎介紹

編號為從N到N+ngpio-1

” label”屬性,用于判斷控制器,并不總是唯一的

9.3 IMX6ULL開發板GPIO編號的確定

? 每個芯片可以有N組GPIO,每組GPIO最多有

發表于 08-05 13:33

學習資料:520-基于ZU15EG 適配AWR2243的雷達驗證底板 高速信號處理板 AWR2243毫米波板

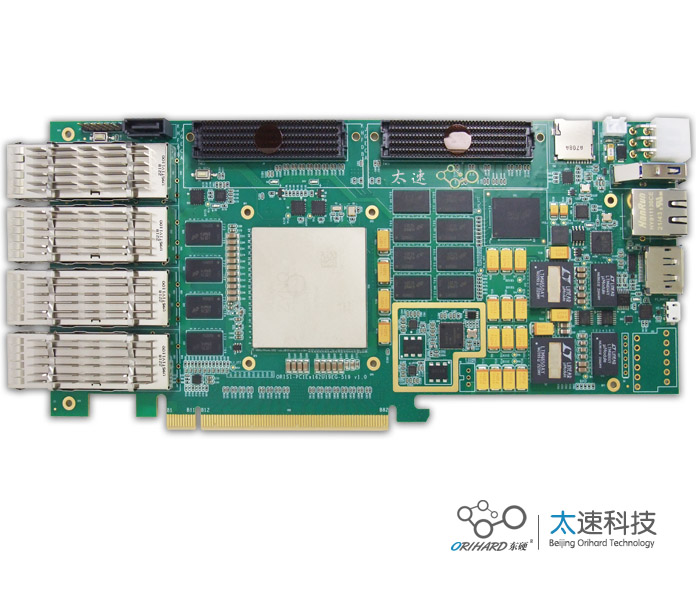

本板卡系太速科技自主研發,基于MPSOC系列SOC?XCZU15EG-FFVB1156架構,搭載兩組64-bit?DDR4,每組容量32Gb,最高可穩定運行在2400MT/s。

米爾基于NXP iMX.93開發板的M33處理器應用開發筆記

資源MYD-LMX9X開發板(米爾基于NXPiMX.93開發板)3.軟件資源Windows7及以上版本軟件:IAREmbeddedWorkbench4.板載固件調試

產品原理圖:619-基于雙FMC接口 ZU19EG 的6U VPX采集存儲計算處理卡

該板卡是采集、存儲、計算、管理一體的高集成度、加固型的信號處理平臺,北京太速科技本板卡基于Xilinx公司Zynq?UltraScale+ MPSOC系列SOC?XCZU19EG-FFVC1760架構,其中,ARM端搭載一組64-bit DDR4,總容量達4GB,可穩定運行在2400MT/s。

什么是GPIO?GPIO組成原理

GPIO全拼叫General Purpose Input Output(通用輸入輸出)簡稱IO口也叫總線擴展器,GPIO口是由引腳,功能寄存器組成,不同的架構中的GPIO封裝不同,所使用的引腳數與寄存器數不同,具體可以參考芯片手

發表于 04-28 12:30

?7251次閱讀

XCZU15EG設計原理圖:523(ZCU102E的pin兼容替代卡) 基于 XCZU15EG的雙 FMC通用信號處理板

本板卡基于Xilinx Zynq Ultrascale+ MPSOC系列SOC XCZU15EG-FFVB1156架構,PS端搭載一組64-bit DDR4,容量32Gb,北京太速科技板卡,最高可

KU115+ZU19EG+DSP6678的雙FMC 6U VPX處理板

和 1 片 Zynq UltraScale+ MPSoC 家族的 XCZU19EG-2FFVC1760I 以及 1 片 TI 公司的 DSP 芯片 TMS320C6678ACYPA。

請問有XCZU9CG-FFVC900的原理圖庫嗎?

有大佬分享一下XCZU6CG-FFVC900、XCZU9CG-FFVC900、XCZU15EG-FFVC900的原理圖庫?

發表于 04-01 15:43

XCZU3EG開發筆記之gpio_emio?

XCZU3EG開發筆記之gpio_emio?

評論