從平面器件到finFET的轉(zhuǎn)變使得芯片制造商能夠?qū)⒐に嚭推骷?6nm/14nm向更密集的方向發(fā)展,但是行業(yè)在每個節(jié)點處都面臨諸多挑戰(zhàn)。

成本問題和技術(shù)問題都是明顯的挑戰(zhàn)。此外,cycle time也在逐漸增加,這是芯片尺寸縮小公式中的一個關(guān)鍵但很少宣傳的因素,這為芯片制造商和客戶帶來了更多的擔(dān)憂。事實上,成本、技術(shù)障礙和cycle time都是摩爾定律持續(xù)放緩的原因。

cycle time是晶圓廠從開始加工一個晶圓批次到該批次加工完成所花費的時間。通常,晶圓批次由25個芯片組成,它在晶圓廠的各種工藝步驟之間移動。先進的邏輯工藝可以有600到1000個步驟,甚至更多。

查看cycle time的一個簡單方法是在晶圓廠中應(yīng)用稱為Little's Law(利特爾法則)的概率理論。在這種情況下,根據(jù)KLA-Tencor公司的理論,cycle time等于起始速率上的在制品(WIP)。例如,根據(jù)KLA-Tencor的數(shù)據(jù),如果晶圓廠有12000個批次,每月處理4000個批次,則總cycle time為3個月。

圖1:何為cycle time?(來源:KLA-Tencor)

這聽起來很簡單,但在現(xiàn)實世界中并不奏效。例如,與平面器件相比,3D NAND和finFET具有更多層的復(fù)雜3D結(jié)構(gòu)。處理它們需要更多的步驟,這會增加晶圓廠的cycle time。

為了防止cycle time的增加,芯片制造商需要更快的設(shè)備,曝光工具成為了重中之重。作為回應(yīng),設(shè)備供應(yīng)商正在制造具有更高生產(chǎn)能力的工具。這些工具還可以處理更先進和更微小的結(jié)構(gòu)。

盡管生產(chǎn)能力有了提升,但是隨著更多的多重曝光步驟和其他工藝的轉(zhuǎn)變,cycle time仍然在增加。加州大學(xué)伯克利分校工業(yè)工程與運營研究教授Robert Leachman說:“我們的流程和產(chǎn)品的復(fù)雜性比工具的生產(chǎn)率提升的速度更快。雖然我們更擅長運營工廠,工具也變得好很多,但是制造芯片仍然需要花費更長時間。”

通常,制造廠中最常用的cycle time量度是“每層掩膜的天數(shù)”。平均來說,制造廠需要1到1.5天的時間來處理一層。最好的晶圓廠是0.8天,Leachman表示。

28nm器件有40至50個掩膜層。相比之下,14nm/10nm器件有60層,預(yù)計7nm可以增長到80到85層,5nm可能有100層。因此,使用今天的平版印刷技術(shù),28nm的cycle time大約為40天,14nm/10nm為60天,7nm則增加到80到85天。如果5nm仍使用今天的技術(shù),不用極紫外光刻的話,則會達(dá)到100天。

為了使事情復(fù)雜化,晶圓廠的cycle time在一項工藝的初期會增加,但隨著技術(shù)的成熟而下降。在此過程中,cycle time可能會受晶圓廠中可變因素的影響。最大的問題涉及到處理各個工藝步驟之間的等待時間。

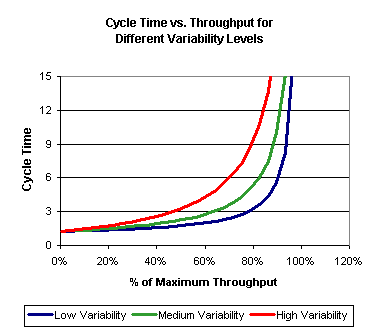

圖2:可變因素對生產(chǎn)能力和cycle time的影響。(來源: Fabtime)

考慮到這些問題,芯片制造商可能會遇到延遲給定工藝過程的問題。隨著復(fù)雜性的增加,延遲發(fā)生的概率會更高。潛在的延遲可能會增加晶圓廠成本以及影響芯片客戶的產(chǎn)品上市時間。這很難轉(zhuǎn)化為成本,但這意味著雙方的收入都會蒙受損失。

總而言之,雖然解決的問題越來越大,但是cycle time不斷增加并不奇怪。Leachman說:“每個存儲單元或晶體管的成本仍然下降。隨著我們走向摩爾定律最后階段,成本下降的速度可能要比以前慢很多。但是我們得到它們的速度不會下降。它正在加速。這是一個很大的挑戰(zhàn)。它價值連城,非常困難,我們做得并不好。”

cycle time不限于晶圓廠。同時也是掩膜部門和其他IC流程的一個問題。總而言之,客戶將需要更好地處理cycle time問題,以便對設(shè)計日程有更切合實際的期望。

掩膜部門的問題

涉及cycle time的問題始于掩膜部門。在流程中,芯片制造商設(shè)計一個IC,然后將其轉(zhuǎn)換為文件格式。然后基于該文件格式開發(fā)光掩膜。

光掩膜是IC設(shè)計的主模板。掩膜開發(fā)后,將其運送到晶圓廠并放置在光刻機中。光刻機投射光線透過掩膜,將圖像曝光在芯片上。

所以掩膜和光刻被綁定在了一起。今天,芯片制造商使用193nm波長光刻技術(shù)在芯片上打印微小的特征。實際上,193nm光刻在80nm半節(jié)距處達(dá)到了它的極限。

為了擴展193nm光刻,芯片制造商使用稱為光學(xué)鄰近校正(OPC)的掩膜版增強技術(shù)(RET)。OPC充分利用微小的形狀,以及次解析度輔助特性(SRAF)。SRAF放置在掩膜上,修改掩膜圖案以改善芯片上的可印刷性。然而,在20nm處,SRAF在掩膜上變得太密集,難以在芯片上打印可辨別的特征。

為了解決這個問題,邏輯廠商將目光轉(zhuǎn)移到多重曝光。MentorGraphics高級物理驗證方法的項目經(jīng)理David Abercrombie在一篇博客中解釋說:“對于多重曝光,原始的掩膜形狀在兩個或更多個掩膜之間被劃分,使得每個形狀都具有足夠的空間,以便OPC操作使其可打印。然后單獨打印每個掩膜,最終將整套原始形狀的圖像成像到芯片上。”

多重曝光使行業(yè)能夠縮小IC尺寸,但對掩膜有一些影響。SRAF正在變得越來越小,越來越復(fù)雜。D2S首席執(zhí)行官Aki Fujimura表示:“除此之外,多重曝光還需要更多的掩膜。每個掩膜的倍增需要更長的時間才能產(chǎn)生,并且需要更多的掩膜,這會在給客戶返回樣片時引起問題。”

復(fù)雜性影響光掩膜生產(chǎn)的cycle time。掩膜制造商使用術(shù)語“周轉(zhuǎn)時間(turnaround time,TAT)”,而不是cycle time,TAT是指制作和發(fā)布掩膜的時間。

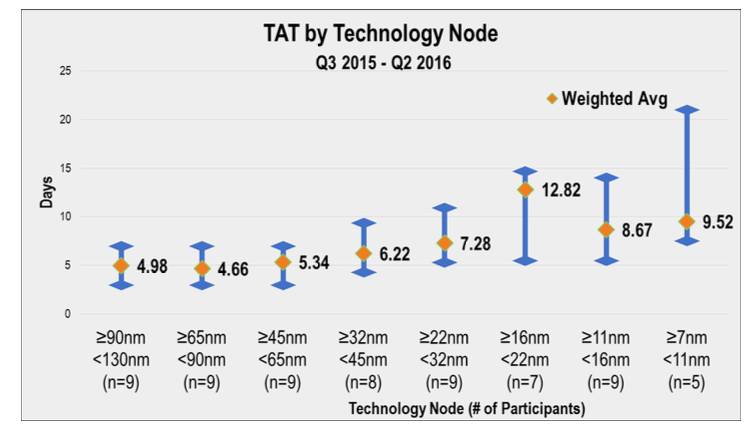

根據(jù)Beam Initiative的“掩膜制造商調(diào)查”,28nm掩膜的TAT約為7.28天。對于16nm/20nm掩膜,TAT增加到了12.82天。雖然在調(diào)查中沒有分析增加的原因,但一種可能性是多重曝光的來臨。

根據(jù)調(diào)查,14nm掩膜的TAT下降到8.67天。雖然也沒有分析其原因,但這可能是由芯片制造商積累了更多的多重曝光經(jīng)驗所導(dǎo)致的。在10nm/7nm處,TAT預(yù)計將增加到9.52天。

圖3:TAT再次上升(來源:eBeam Initiative)

Dai Nippon Printing(DNP)的研究員Naoya Hayashi說:“TAT更長的原因是寫入時間、檢查時間和驗證時間。”

寫入時間是罪魁禍?zhǔn)住H缟纤觯琁C設(shè)計要轉(zhuǎn)換為文件格式。該格式被轉(zhuǎn)換成電子束掩膜寫入器的一組指令。這個過程稱為掩膜數(shù)據(jù)準(zhǔn)備(MDP)。

然后,電子束掩膜寫入器將指令和圖案微小的特征寫入掩膜。但隨著掩膜復(fù)雜性的增加,電子束需要更長的時間來寫入它們。

幸運的是,我們有解決方案。最近,IMS Nanofabrication引入了一個多光束掩膜寫入器。它配備262,144個光束,系統(tǒng)可以在10小時內(nèi)寫完一個光學(xué)掩膜,而傳統(tǒng)工具要寫30小時。

NuFlare正在開發(fā)一個類似的系統(tǒng)。“多光束寫入有助于TAT,因為寫入時間與形狀的數(shù)量和復(fù)雜性無關(guān)。”D2S的Fujimura說。

還有其他問題。Fujimura說:“掩膜形狀需要更小、更復(fù)雜,以滿足所需的晶圓加工余量、劑量控制和實現(xiàn)線性校正所需的形狀校正。這需要增加數(shù)據(jù)準(zhǔn)備的處理時間。”

一方面,D2S開發(fā)了可以加快MDP和其他流程的平臺。但距離掩膜部門的要求還有差距,該行業(yè)希望有更快的過程控制工具和其他系統(tǒng)。

晶圓廠內(nèi)部

一旦掩膜完成,便被運送到晶圓廠。根據(jù)加州大學(xué)伯克利分校的理論,晶圓廠每月有50,000個晶圓開始制造,晶圓廠可能需要以下設(shè)備:

?50臺掃描式/步進式光刻機加上晶圓軌道;

?10臺大電流和8個中等電流離子注入機;

?40臺刻蝕機

?30種CVD工具

晶圓廠還需要清潔系統(tǒng)和過程控制工具。

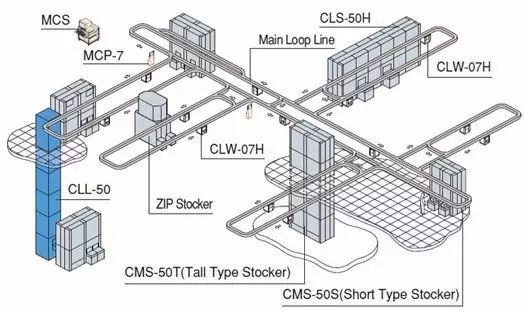

晶圓廠是使用自動化材料處理系統(tǒng)(AMHS)的自動化工廠。為此,芯片在一種稱為前端開啟式晶圓傳送盒(FOUP)的封閉容器中進行加工和運輸。使用高架式芯片運輸車(OHT)系統(tǒng)將FOUP從一組設(shè)備運送到另一組。據(jù)Daifuku說,在大型晶圓廠中,OHT軌道可以長達(dá)10公里,可容納數(shù)百輛汽車。

圖4:統(tǒng)一的晶圓廠運輸系統(tǒng)(來源:Daifuku)

為了讓所有工作一齊進行,晶圓廠使用了各種工廠自動化技術(shù)。 供應(yīng)商還使用WIP流程技術(shù)(如實時分發(fā)和調(diào)度)來協(xié)調(diào)制造流程。

除物流外,晶圓廠管理者也在關(guān)注其他事宜。KLA-Tencor全球客戶組織高級總監(jiān)Robert Cappel表示:“管理者關(guān)心成本、cycle time和可預(yù)測的收益。芯片制造商的目標(biāo)是用可接受的成本來制造可靠的器件。cycle time也是關(guān)鍵。我每天都在晶圓廠中,cycle time的增加會花費我更多的錢。”

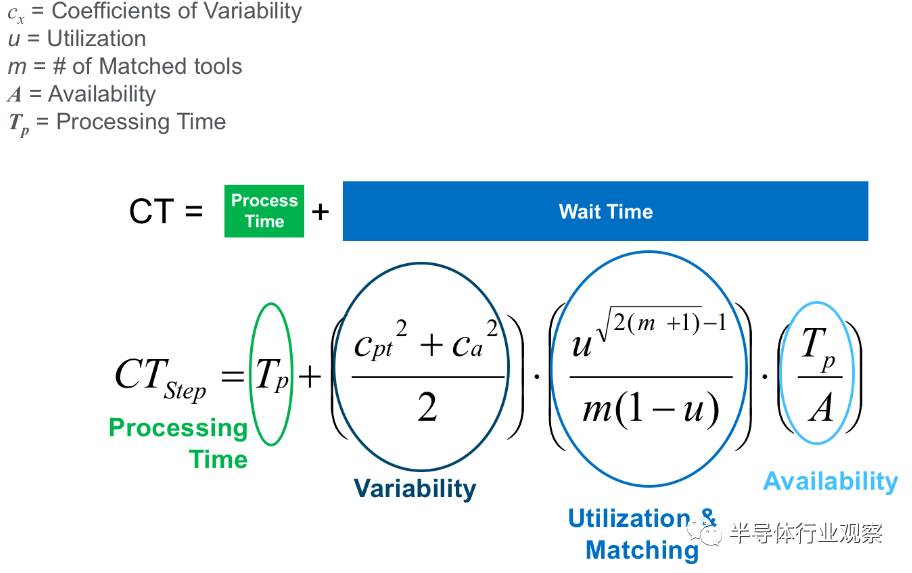

然而,控制cycle time是具有挑戰(zhàn)性的。例如,晶圓廠工具具有一定的生產(chǎn)能力規(guī)格,相當(dāng)于確定的cycle time。Cappel說:“這就像是工作在完美的世界中,但cycle time中有更多的組分。有處理時間,然后有等待使用工具的排隊時間。”

事實上,cycle time的最大組分是等待時間。可變因素、操作員延遲、設(shè)備安裝錯誤,以及設(shè)備停機也是等式的一部分。此外,晶圓廠的利用率也是組合的一部分。ASML產(chǎn)品營銷總監(jiān)Michael Lercel說:“如果以很低的利用率運營晶圓廠,您的加工時間會非常原始。但是,如果以更高的利用率運營晶圓廠,排隊時間就會變得更長。”

如果這還不夠,則還有其他問題。三星半導(dǎo)體研發(fā)中心的技術(shù)人員Han Jin Lim表示:“隨著器件的復(fù)雜性日益增加,晶圓廠工具的生產(chǎn)率下降了。”

考慮到這一點,芯片制造商需要更快的工具。但不是所有的流程步驟都需要更高的生產(chǎn)能力工具,特別是對于一些非關(guān)鍵層。

AppliedMaterials副總裁兼圖案和封裝部門總經(jīng)理Prabu Raja說:“有些工具需要cycle time和生產(chǎn)能力的顯著改善。”

總而言之,cycle time是一個復(fù)雜的問題,它有許多變量。以下是公式:

圖5:Cycle time的組分(來源:KLA-Tencor)

Cycle time的瓶頸

顯然,芯片制造商希望在四個主要領(lǐng)域保持一定的cycle time。它們是:圖案形成、前段工程(FEOL),后段工程(BEOL)和不增值作業(yè)。FEOL是在晶圓廠形成晶體管的地方,而BEOL是制造銅互連的地方。不增值作業(yè)包括計量和檢驗。

finFET制造工藝從圖案形成開始,這是cycle time最大的瓶頸。三星的Lim表示:“隨著圖案復(fù)雜性的增加,晶圓廠工具的cycle time也將增加,包括從FEOL到BEOL的所有步驟。”

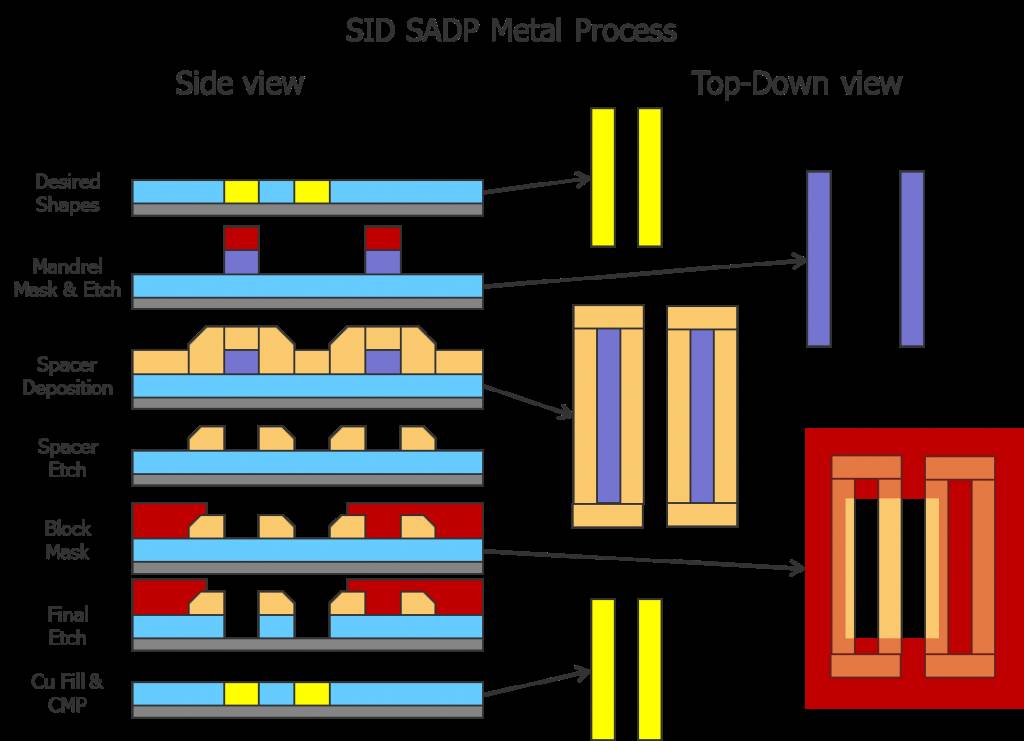

在今天的多重曝光流程中,芯片制造商實施了兩步加工——畫線和切割。首先,使用一種稱為自對準(zhǔn)二重/四重圖案(SADP/SAQP)的技術(shù)在器件上畫細(xì)線。 SADP/SAQP使用一個光刻步驟以及額外的沉積和蝕刻步驟。

圖6:SADP金屬工藝,其中的間隔物是電介質(zhì)(來源:Mentor Graphics)

對于切割,芯片制造商使用SADP/SAQP,或雙重曝光工藝。雙重曝光有時被稱為曝光-刻蝕-曝光-刻蝕(LELE)。三重曝光包括LELELE。

對于多重曝光中,7nm工藝所進行沉積、蝕刻和清潔步驟是16nm/14nm的兩倍。 Coventor首席技術(shù)官David Fried表示:“隨著我們從簡單的一次曝光,到大多數(shù)28nm工藝所采用的多重曝光,步驟數(shù)增加得很快。現(xiàn)在,有三個切割級別的SAQP流程可能有60步操作,如沉積、蝕刻、清潔、旋轉(zhuǎn)和曝光。”

在SADP流程中,可以使用抗蝕劑來繪制圖層。然后在抗蝕劑上沉積一層,再次蝕刻,直到沉積物留在抗蝕劑線的兩側(cè)。然后去除掉抗蝕劑。專家指出,SADP無需兩個完整的光刻循環(huán),因此不會增加循環(huán)時間。

然后就是LELE。如果進行兩次完整的光刻/蝕刻循環(huán)來創(chuàng)建雙重曝光,那么循環(huán)時間會增加。據(jù)專家介紹,如果您的工藝有25個光刻層,其中有5層需要雙重曝光,那么您將會有30個光刻循環(huán)。

“這是看待問題的另一種方法,對于LELE雙重曝光,層的cycle time可能會加倍,因為您必須重復(fù)照相/蝕刻/去膠過程,三重曝光會增加三倍的cycle time,依此類推。”Mentor的Abercrombie說。

還有其他因素,如定位誤差(overlay)和整體設(shè)備效率(OEE)。定位誤差涉及到光刻機將各種掩膜層精確對準(zhǔn)的能力。根據(jù)加州大學(xué)伯克利分校的理論,OEE是指完成的工作量除以總時間。

加州大學(xué)伯克利分校的Leachman表示:“將所有這些都加起來。如果你在某些層上做三重曝光,你會有50到60層,這需要很長時間。你要面對這些步驟所有的等待時間。減少cycle time的真正戰(zhàn)斗在于減少等待時間。一個晶圓必須等待所有晶圓都通過了流水線才會離開。即使每個芯片通過光刻機只需1分鐘,從這個批次開始到機器人將它運走仍會花費45分鐘的時間。”

有解決方案嗎?

同時,每家芯片制造商都有給定工藝過程的設(shè)定cycle time。為每個工藝過程指定cycle time非常困難,但很顯然,cycle time正在增加。

那么解決方案有哪些?可以肯定的是,工具廠商正在進行改進。不久前,193nm光刻機每小時處理量為100片。ASML的Lercel說:“現(xiàn)在,光刻機每小時處理275個晶圓,而且精度更高。”

如果行業(yè)采用EUV,情況可能會不同。他表示,例如,在7nm工藝中使用EUV,cycle time至少減少一個月。

沉積和蝕刻工具的供應(yīng)商也在進行改進。Lam Research全球產(chǎn)品集團首席技術(shù)官Yang Pan說:“最終,這事關(guān)良品的數(shù)目,而且想得到良品有許多因素需要考慮。這包括:在沉積過程中降低薄膜應(yīng)力,滿足finFET特性的苛刻要求,特征從頂部一直到底部的蝕刻,減少可變因素,等等”

多重曝光還需要使用一種稱為原子層沉積(ALD)的緩慢工藝制造的薄膜。為了加快這個過程,有些廠商提供了多晶圓系統(tǒng)。Pan說:“我們已經(jīng)證明,更多地利用(多晶圓)工藝架構(gòu)固有的生產(chǎn)力優(yōu)勢對于厚膜沉積堆疊至關(guān)重要。”

的確,這需要一個整體的方法。Applied Materials公司蝕刻和圖案策略和市場營銷副總裁Uday Mitra說:“我們與客戶合作,簡化了多重曝光中使用的工藝流程,從而減少了工藝步驟和成本,同時降低了cycle time和工藝引起的變化。這可以通過在隔膜、硬掩膜、間隙填充,和高選擇性蝕刻能力的過程中使用新型薄膜來實現(xiàn)。”

在另一種方法中,業(yè)界繼續(xù)開發(fā)新的集群工具。 AppliedMaterials的Raja說:“現(xiàn)在有更多的集成工具,例如沉積和蝕刻。現(xiàn)在,我們可以把沉積和蝕刻放在一起,把外延和時刻放在一起,把CVD和PVD放在一起。這些類型的集成系統(tǒng)消除了排隊時間。”

另一個策略是早日解決問題。為此,芯片制造商應(yīng)該加強他們的計量和檢查工作。發(fā)現(xiàn)缺陷,或檢測線路中的可變因素可以解決一些問題。“過程控制可以幫助您縮短cycle time,把cycle time做到最好的人有更多的過程控制程序。”KLA-Tencor的Cappel說。

-

芯片

+關(guān)注

關(guān)注

456文章

51121瀏覽量

426023 -

晶圓廠

+關(guān)注

關(guān)注

7文章

624瀏覽量

37931 -

光刻機

+關(guān)注

關(guān)注

31文章

1156瀏覽量

47515

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于晶圓廠的cycle time的分析和應(yīng)用

關(guān)于晶圓廠的cycle time的分析和應(yīng)用

評論