4月18日,在臺積電召開第一季度財報會議中,臺積電指出3nm技術已經進入全面開發的階段。5月15日,三星在Foundry Forum活動中,發布了公司第一款3nm工藝的產品設計套件。由此看來,在英特爾還在糾結10nm如何向前發展之際。先進工藝的戰火已經在臺積電和三星的推動下,燃燒到了3nm。

去年,三星的Foundry Forum活動中強調了先進封裝的重要性;今年,三星的Foundry Forum則將重點放在了先進制程的進度上。就此,我們也能夠很明顯地感受到,三星與臺積電之間的競爭越發激烈。

戰略部署:3nm何時到來?

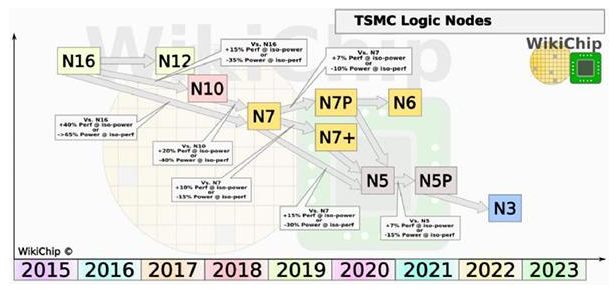

在先進制程方面,臺積電和三星的關系可以說是針尖對麥芒,兩者之間的龍爭虎斗也著實精彩。2015~2016年,三星Foundry先進制程能力的逐步成熟,從臺積電那里奪得了不少大客戶訂單。2016~2017年,臺積電先進制程的進一步成熟,并憑借InFO技術獨攬蘋果大單。2017年,三星又宣布將晶圓代工部分獨立,擴大純晶圓代工業務份額,直接對標臺積電。至此以后,兩者之間關于先進制程的搶灘戰越來越激烈。

就目前公開的消息來看,臺積電和三星都已經透露了一些關于3nm工藝節點上的進展。目前來看,5nm、3nm節點主要面向FPGA等高性能計算領域,智能處理器和5G芯片。而2019年被視為是5G商用元年,在接下來的兩三年中,5G將會被大規模使用。或許,這也是兩大晶圓代工龍頭紛紛選擇透露3nm進程的誘因之一。

2018年12月,據***媒體報道稱,臺積電的3nm晶圓廠方案已經獲得***主管部門批準,選址***南部科技園區。據悉,臺積電3nm工廠建設預計會花費超過200億美元,同時有望帶動相關供應商跟進建廠。依照臺積電規劃藍圖,3nm應可在2021年試產、2022年量產,成為全球第一家提供晶圓代工服務,同時解決很多AI人工智能芯片功效更強大的晶圓代工廠。

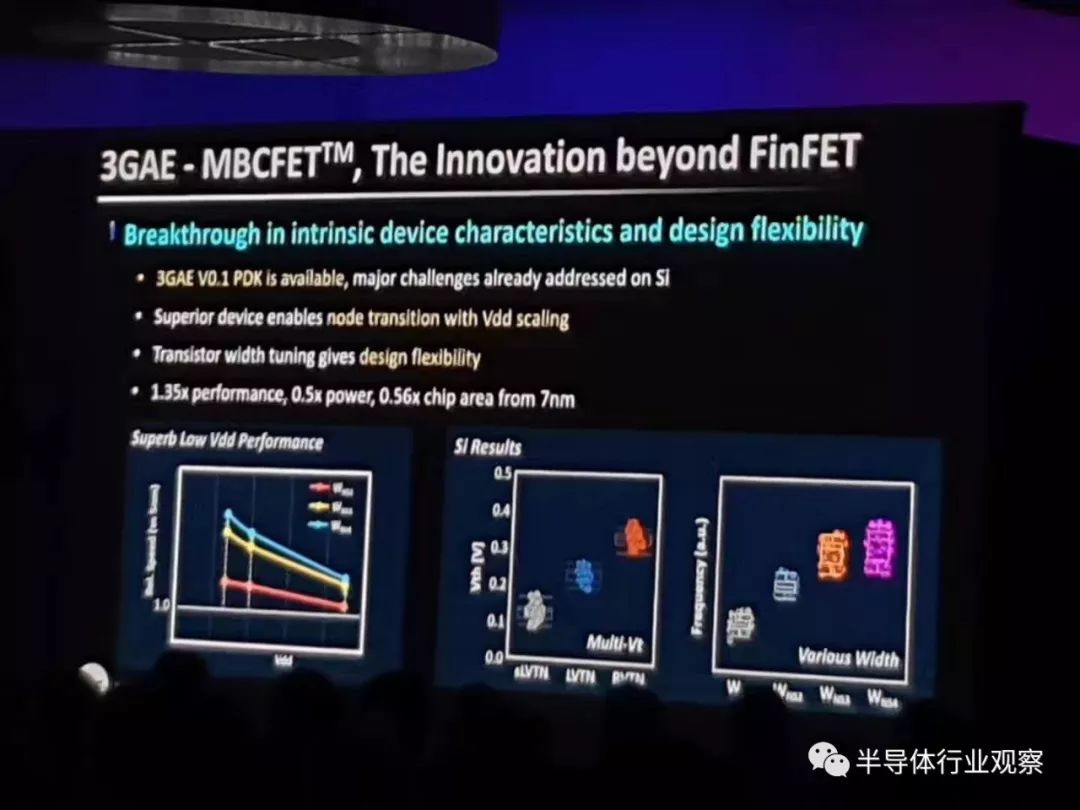

前不久,三星也公布了未來的制程工藝路線圖,公司計劃今年推出7nm EUV工藝,明年有5/4nm EUV工藝,2020年則會推出3nm EUV工藝,同時晶體管類型也會從FinFET轉向GAA結構。據悉,三星3GAE工藝中還在開發當中,不過他們4月份就發布了3GAE工藝的PDK 1.0工藝設計套件,旨在幫助客戶盡早開始設計工作,提高設計競爭力,同時縮短周轉時間(TAT)。

基于GAA的工藝節點有望在下一代應用中廣泛采用,例如移動、網絡通訊、汽車電子、人工智能(AI)和IoT物聯網等。三星還透露,通過使用全新的晶體管結構可使性能提升35%、功耗降低50%,芯片面積縮小45%。不過,三星官方沒有明確3GAE工藝量產時間,但根據市場猜測,三星3nm在2021年實現量產是大概率事件。

而就以上消息來看,三星將早于臺積電一年推出3nm工藝。誰能更快地推出可靠的新工藝,誰就有可能掌握在該制程上的最大話語權。為了能夠贏得3nm這場搶灘戰的勝利,都需要哪些技術來助攻?

助攻一:晶體管結構

目前,先進制程多數采用立體結構,即"FinFET"(鰭式場效晶體管),此結構的通道是豎起來而被閘極給包圍起來的,因為形狀像魚類的鰭而得名,如此一來閘極偏壓便能有效調控通道電位,因而改良開關特性。但是FinFET在經歷14/16nm、7/10nm階段后,不斷拉高的深寬比(aspect ratio)讓前段制程已逼近物理極限,再繼續微縮的話,先不提電性是否還能有效提升,就結構而言就已有許多問題。

為了擴展,通道和柵極之間的接觸面積需要增加,Gate-All-Around(GAA)設計被提了出來。GAA調整了晶體管的尺寸,以確保柵極也位于通道下方,而不僅僅在頂部和側面。這允許GAA設計垂直堆疊晶體管,而不是橫向堆疊晶體管。

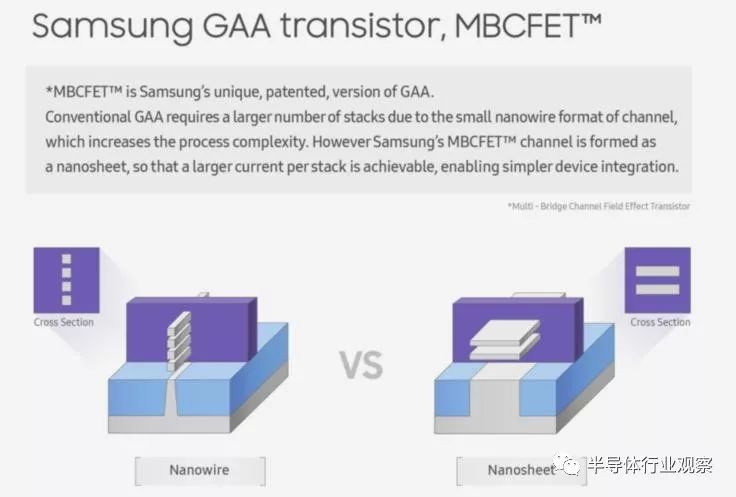

三星方面,據公開消息整理,三星與IBM合作開發了GAAFET(Gate-All-Around)工藝節點,同時,三星也已宣布對早期工藝進行定制。三星Foundry市場副總裁Ryan Sanghyun Lee稱,自2002年以來,三星一直在開發其GAA技術的專有實現,稱為多橋通道FET(MBCFET)。該公司指出,其MBCFET技術使用納米片器件來增強柵極控制,這可以顯著改善晶體管的性能。據悉,它可以通過用納米片代替Gate All Around的納米線來實現每堆更大的電流。取代增加了傳導面積,允許增加更多的柵極而不增加橫向足跡。三星聲稱MBCFET的設計將改善工藝的開關行為,并允許處理器將工作電壓降至0.75V以下。MBCFET的關鍵點在于該工藝與FinFET設計完全兼容,不需要任何新的制造工具。

在前不久三星舉行的Foundry Forum上,三星稱3nm工藝時代不再使用FinFET晶體管,而是使用全新的晶體管結構——GAA(Gate-All-Around環繞柵極)晶體管,通過使用納米片設備制造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代FinFET晶體管技術。

在臺積電方面,官方公布有關于3nm技術方面的消息較少。據芯科技消息稱,臺積電3nm制程技術已進入實驗階段,業內人士更透露,3nm制程在"Gate All Around(GAA) "、環繞式閘極技術上已有新突破。業內人士進一步表示,臺積電已經做出環繞式閘極的結構,外型就像類圓形般,但因為尺寸比前一代縮小30%,也必須導入新材料InAsGe nanowire and Silicon nanowire,因此制程技術上相當困難,尤其是在蝕刻部分是大挑戰,不過以優勢來說,環繞式閘極的結構將可以改善ESD靜電放電、且優化尖端放電的問題,材料廠的高管也認為,環繞式閘極的結構得以繼續微縮柵長尺寸。

由此可見,GAA架構將成為3nm工藝上不可缺少的技術。

助攻二:EUV

在上文三星所提到的先進制程路線圖時,我們不止一次看到了EUV的身影。同時,我們也通過臺積電在今年來的動作上,發現了EUV對于先進制程能夠得到進一步發展的重要性——前不久,臺積電宣布已完成其5納米工藝節點的基礎設施設計,該節點將利用該公司的第二代極紫外(EUV)以及深紫外(DUV)光刻技術。

據Techshop消息稱,從3月底開始,臺積電準備開始使用極紫外光刻技術批量生產7nm晶圓。ASML已經為臺積電在2019年計劃的30個系統中分配了18個。接下來,臺積電的7nm EUV產量將全面運行,該公司的5nm工藝將轉向風險生產狀態。EUV將繼續用于5nm,預計可行至3nm。到2019年底,臺積電將在5nm節點上進行芯片設計,預計到2020年初量產。據悉,2018年,7nm EUV僅占臺積電銷售額的9%。今年,新工藝有望占其總銷售額的四分之一。

在三星方面,去年 10 月,三星就宣布了準備初步生產 7nm 工藝,這是三星首個采用 EUV 光刻技術的工藝節點。據悉,三星已提供業界首批基于EUV的新產品的商業樣品,并于今年年初開始量產 7nm 工藝。與其前身的10nm FinFET相比,三星的7LPP技術不僅大大降低了工藝復雜性,而且層數更少,產量更高,而且面積效率提高了40%,性能提高了20%,功耗降低了50%。到2020年,三星希望通過新的EUV系列為需要大批量生產下一代芯片設計的客戶提供額外的容量。作為EUV的先驅,三星還開發了專有功能,例如獨特的掩模檢測工具,可在EUV掩模中執行早期缺陷檢測,從而可以在制造周期的早期消除這些缺陷。據悉,三星位于韓國華成的S3生產線正在生產基于EUV的工藝的芯片產品。此外,三星還在華城部署了新的EUV生產線,該生產線預計將在2019年下半年完成,并從明年開始增產。

助攻三:封裝

除此之外,先進封裝也是各大代工廠的主攻方向。

此前有媒體報道稱,臺積電完成全球首顆3D IC封裝,預計將于2021年量產。臺積電此次揭露3D IC封裝技術成功,正揭開半導體制程的新世代。目前業界認為,此技術主要為是為了應用在 5 納米以下先進制程,并為客制化異質芯片鋪路,當然也更加鞏固蘋果訂單。Digitimes的研究也指出,為了搭配先進制程微縮及異質芯片整合趨勢,臺積電研發整合的10nm邏輯芯片及DRAM的整合扇出層疊封裝(InFO-PoP),以及12nm系統單芯片與8層HBM2存儲器的CoWoS封裝等均進入量產,并推出整合多顆單芯片的整合扇出型基板封裝(InFO-oS)、整合扇出存儲器基板封裝(InFO-MS)、整合扇出天線封裝(InFO-AIP)等新技術。

三星推出了可與臺積電晶圓級扇出型封裝(InFO)抗衡的FOPLP-PoP封裝,其目標2019年前為新制程建立量產系統,藉此贏回蘋果供應訂單。但DIGITIMES認為,FOPLP 仍面臨不小的挑戰,以目前 FOPLP 剛起步的狀況來看,經濟規模將是技術普及的最大挑戰,在初期良率還不夠好的狀態下,FOPLP 產能要達到理想的成本優勢,短期內恐不易達成。在其他先進封裝上,針對2.5D封裝,三星推出了可與臺積電CoWoS封裝制程相抗衡的I-Cube封裝制程,在2019年三星晶圓代工論壇上,該公司的FD-SOI(FDS)流程和eMRAM的擴展以及一系列最先進的封裝解決方案也在今年的Foundry論壇上亮相。據悉,三星今年將完成28FDS工藝,18FDS和1Gb容量eMRAM的繼任者的開發。

投資規模

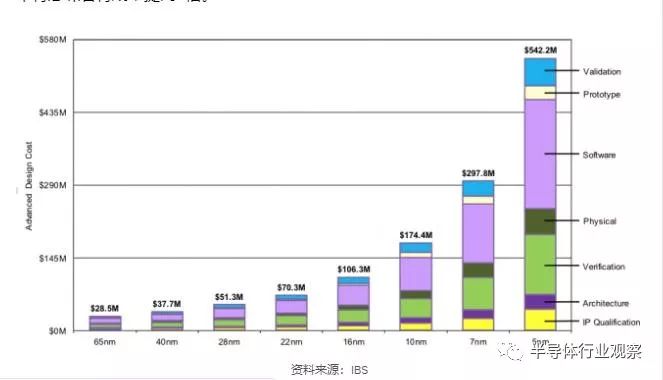

無論是晶體管架構,還是EUV,亦或是先進封裝,都是先進制程在向前發展的過程中不可缺少的技術。但每一項技術,都需要大量的資金來做支持。

國際商業戰略(IBS)首席執行官漢德爾?瓊斯(Handel Jones)曾表示,“該行業需要大幅增加功能,并小幅增加晶體管成本,以證明使用3納米。3nm工藝開發成本將達到40億至50億美元,而每月40,000片晶圓的晶圓廠成本將達到150億至200億美元。”

為此,三星電子于4月24日宣布,三星電子將在2030年投資1150億美元用于系統半導體領域的研發和生產技術。根據已批準的未來12年計劃,這1150億美元中,將投資73萬億韓元(634億美元)用于韓國的研發(這可能意味著芯片研發和工藝技術的研發),60萬億韓元(521億美元)將投資于用于制造邏輯芯片的生產設施和基礎設施為各種客戶。

臺積電方面,根據臺積電14日董事會消息稱,臺積電通過了1,217.81億元資本預算,除升級先進制程產能外,也用于轉換部分邏輯制程產能為特殊制程產能。臺積電預定今年度資本支出金額約100億美元至110億美元,其中80%經費將用于3 納米、5納米及7納米先進制程技術。臺積電預期,今年7納米與第二代7納米制程將貢獻約25%業績。另外有10%經費用于先進封裝與光罩,10%用于特殊制程。

三星與臺積電除了在3nm制程上爭奪激烈,在其他先進制程方面的碰撞也不少。自2019年以來,臺積電接連發布了6nm、5nm、5nm+的發展路線。三星方面,雖在7nm的進度上稍顯遜色,但其EUV技術卻不容小覷。另外,從本次三星積極布局3nm的動作上來看,也許,三星正在企圖利用3nm技術來反超臺積電。

-

芯片

+關注

關注

456文章

51155瀏覽量

426318 -

功耗

+關注

關注

1文章

828瀏覽量

32022

發布評論請先 登錄

相關推薦

回顧臺積電與三星的3nm爭斗

回顧臺積電與三星的3nm爭斗

評論