半導體技術的未來通常通過光刻設備的鏡頭來看待,盡管幾乎無休止地存在極具挑戰性的技術問題,但光刻設備繼續為未來的工藝節點提供更好的分辨率。

多年來,光刻技術一直被視為與制造相關的主要門控因素,阻礙了器件持續到7nm工藝節點的晶圓廠吞吐量。這些問題已經得到解決,但許多新的問題即將出現,以及一些重要的改進。

來自設計、光刻、測試和測量以及封裝界的行業專家齊聚今年的 SEMICON West 和 DAC,討論極紫外 (EUV) 和即將推出的高數值孔徑 EUV(高數值孔徑 EUV)的產品路線圖,包括最新的研發工作,以及推進光刻創新和擴展密度的障礙。討論的領域包括提高功率和工藝效率,增強計量技術,以及探索新的解決方案,如曲線掩膜和光刻膠的新化學物質。然而,在這些進步中,始終專注于實現更高的產量、更高的吞吐量和更低的每片芯片成本。

高數值孔徑EUV 今年的大部分討論都集中在EUV的下一步發展以及高數值孔徑EUV的時間表和技術要求上。ASML戰略營銷高級總監Michael Lercel表示,其目標是提高EUV的能源效率,以及下一代高數值孔徑EUV工具的發展狀況。

“EUV工具不是最節能的,但我們正在盡一切努力提高能源效率和工具本身,從而顯著提高制造每個晶圓所需的能量,”Lercel說,并強調了數值孔徑(NA)在這些工具的發展中的作用。雖然每次曝光的總能耗遠高于 193i 光刻,但支持高密度器件的單一圖案化的能力意味著需要更少的曝光。這反過來又減少了整體能量輸出和循環時間。

High-NA將數值孔徑從0.33增加到0.55,將分辨率從約26至30納米間距提高到16納米間距。通過增加數值孔徑,分辨率會提高,但光學元件必須變得更大。這需要一臺更大的機器,這帶來了額外的好處。更大的工具旨在提高可維護性,以保持高生產率水平,并縮短維修后恢復生產的時間。新的高數值孔徑系統也更加模塊化,使服務團隊更容易更換單個模塊。

Lercel透露,第一個完全組裝的系統已經建成,但由于沒有最終的光學元件,因此尚未投入使用。他預計這些系統將在今年晚些時候首次出現。

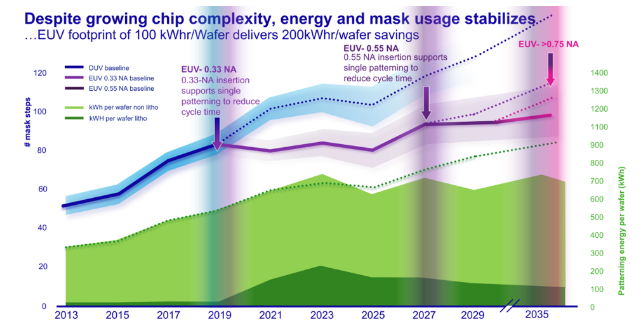

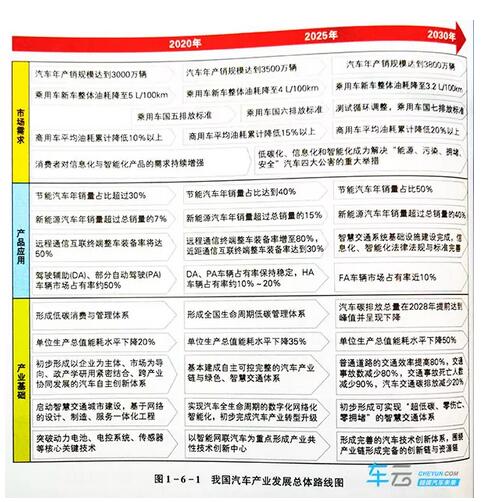

“我們預計未來幾年將出現0.55的插入,并預計客戶將在2025年開始將其投入生產,”他說(見圖1)。“在那之后,我們正在探索具有0.75數值孔徑的hyper-NA,我們預計這將在大約十年內出現。

圖1:ASML預計0.55將在四年內投產,0.75 Hyper EUV將在大約十年內投產。資料來源:ASML/SEMICON West

電子束計量

使用較高的數值孔徑進行曝光意味著光線以較小的角度(稱為入射角)照射到晶圓上。因此,晶圓上特征的垂直結構或“縱橫比”變得更具挑戰性,難以準確觀察和測量。應用材料公司高級總監Ofer Adan討論了對更先進的計量工具來支持高數值孔徑工藝的需求。在 2nm 及以上的節點,使用傳統電子束技術的成像能力,缺陷變得更加難以檢測。

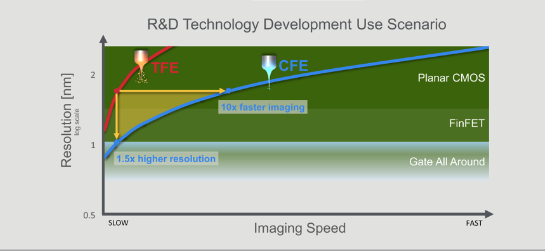

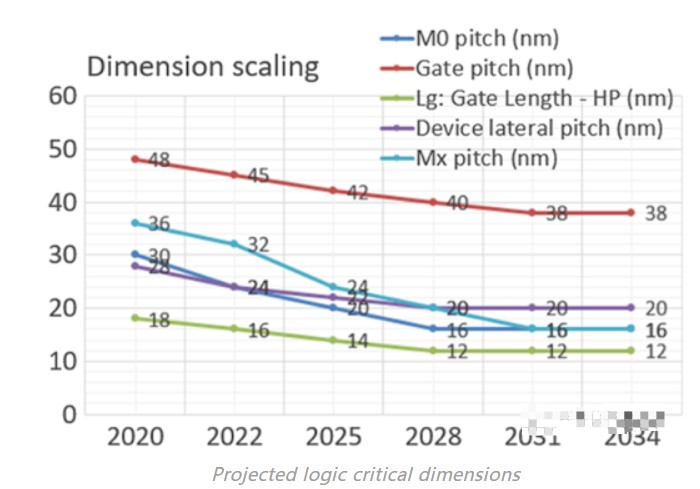

Adan指出,冷場發射(CFE)技術的最新發展是滿足高數值孔徑計量需求的一種可能解決方案。CFE 是一種在較低溫度下工作的電子束源,與傳統的熱離子源相比具有多項優勢,包括提高空間分辨率、更好的光束穩定性和減少球面像差。與傳統的熱場發射 (TFE) 技術相比,CFE 在室溫下工作,從而產生更窄、更高能量的電子束,從而產生更高的分辨率和更快的成像速度(見圖 2)。該技術的較高亮度有助于提供更高分辨率的成像和測量,但較小的光斑尺寸意味著吞吐量會受到顯著影響。

“CFE存在熱場曲線,這是成像速度和分辨率之間的權衡,”Adan說。“您可以降低分辨率并獲得更快的吞吐量,也可以保持相同的速度并獲得更高的分辨率。CFE 的速度比 TFE 快 10 倍。

圖 2:CFE 在相同分辨率下提供 10 倍的成像速度。資料來源:Applied Materials/SEMICON West。

直到最近,CFE的使用僅限于實驗室環境,因為電子束柱的穩定性不足以滿足大批量半導體制造的嚴格要求。Adan提到了兩項創新,它們解決了穩定性挑戰。一種是色譜柱內部的極高真空,第二種是周期性自清潔過程,可連續去除 CFE 源中的污染物,從而實現穩定和可重復的性能。

高數值孔徑

的新工藝技術 TEL蝕刻業務部總監Angélique Raley指出了塑造EUV未來的兩個重要趨勢。首先是從 2D 結構到 3D 結構的轉變,特別是從 finFET 到全柵極 (GAA) 器件的過渡,這對芯片制造所需的工藝產生了重大影響。第二個問題圍繞著EUV的持續臨界縮放,特別是當它涉及將金屬間距降低到低至12 nm時。

Raley表示:“隨著我們從GAA轉向堆疊通道FET(CFET),我們面臨著更高的縱橫比要求。“這一發展再次強調了高度可控的各向同性和定向蝕刻工藝的重要性。”

全柵極 (GAA) 器件將由涉及多層的外延 (epi) 沉積來定義,要求對該沉積過程進行無可挑剔的控制。半導體制造商將需要設計高度受控的各向同性蝕刻,以選擇性地同時在各個方向上蝕刻材料。

等離子體蝕刻仍然是必不可少的,特別是對于高縱橫比蝕刻。例如,接觸式蝕刻是一種復雜的氧化物蝕刻工藝,需要高度的控制。

隨著高數值孔徑EUV的推出,制造商將不得不決定是使用化學放大的光刻膠還是基于金屬氧化物的光刻膠。這種轉變,加上焦深的降低,將需要更薄的光刻膠,因此需要高精度的蝕刻工藝控制。更薄的光刻膠也意味著硬掩模的更廣泛使用,因為光刻膠本身在蝕刻化學中侵蝕得更快。

干式光刻膠 高數值孔徑光刻膠問題的

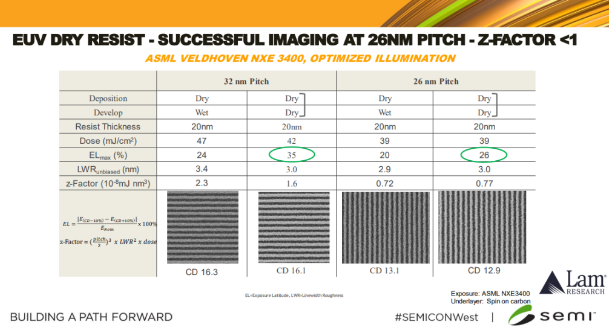

一種解決方案是干式光刻膠。Lam Research的EUV干式光刻膠營銷高級總監Benjamin Eynon表示,與傳統的化學放大(CAR)光刻膠工藝相比,干式光刻膠使用氣體前驅體工藝,涉及干式光刻膠材料和干式顯影工藝。它的分子尺寸比CAR小六倍,可以打印出更精細的細節(見圖3)。它還通過消除液體來簡化流程,從而減少了圖案塌陷的可能性。Eynon 指出,干式光刻膠還可以減少 5 倍到 10 倍的浪費,使其成為更環保的選擇。

圖3:干式光刻膠成像可以對16nm和13nm的線和空間進行圖案設計,線寬粗糙度為3nm。資料來源:Lam Research/SEMICON West

“干式光刻膠可以產生更一致和可預測的結構,同時減少浪費,”Eynon說。“我們在高數值孔徑方面也有分辨率優勢,CAR在35nm間距以下掙扎,我們看到的結果遠低于這個水平。”

他解釋說,與傳統的CAR相比,使用干式光刻膠更改光刻膠厚度要簡單得多。“過去,如果我不得不向光刻膠供應商索要一種紡絲更薄的光刻膠,我將不得不等待六個月才能進行所有測試。現在我們可以改變配方并放下它。

干式光刻膠在加工窗口和缺陷性方面具有優勢,可以忽略不計,但仍有障礙需要克服。降低高數值孔徑的劑量會導致粗糙度增加,因此需要做更多的工作來平衡劑量減少與其他因素,如線寬粗糙度 (LWR)。

imec高級圖案、工藝和材料高級副總裁Steven Scheer也強調了金屬氧化物抗蝕劑相對于CAR在高數值孔徑提供的較小間距下進行線和空間成像的局限性的優勢。但他補充說,需要進一步的研究來減少劑量并改善缺陷率。EUV掃描儀的劑量越低,通量就越高。

Imec和ASML目前正在荷蘭費爾德霍芬的ASML園區內建設一條高NA試驗線。該項目將于 2024 年上半年開放,用于合作研究、測試和開發高數值孔徑 EUV 光刻的工具和工藝。

“高數值孔徑EUV與其說是一場革命,不如說是一種進化,”Scheer說。“我們必須壓縮時間,在大約兩年內生產出這些新技術。Scheer預計,高數值孔徑的理想插入點將是14埃(1.4納米)節點。

高數值孔徑EUV的另一個挑戰涉及計量學,特別是在非常薄的材料成像方面。Scheer列舉了在CD SEM中測量微弱信號回波的困難。優化著陸能量、不同材料和機器學習算法以進行去噪、對比度提取或自動缺陷分類是潛在的解決方案。

掩模創新是Scheer認為是高數值孔徑EUV演進過程的另一個關鍵領域。

“在掩模和成像方面,重要的關鍵因素之一是我們探索低n掩模,以提高整體對比度,”Scheer說。“當你開始達到24納米間距或更低時,除非你真的實現了低n掩模,否則你就會開始失去對比度。因此,我們認為這是一項需要開發的重要技術。

用于曲線設計的

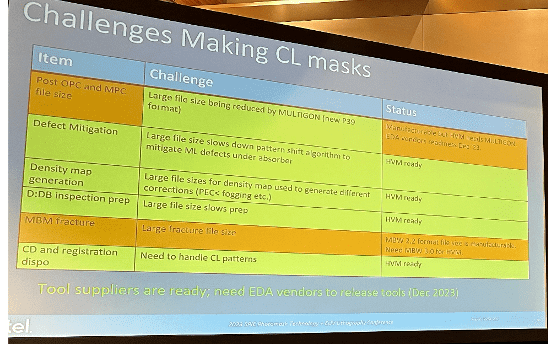

曲線掩模 三十年來,半導體掩模技術基本保持不變,掩模的制作是在可變成型機上進行的,這些機器將可變元件限制在 45 度角。隨著特征的縮小和變得更加復雜,電子束和多波束掩模寫入器提供了設計的靈活性。現在,幾乎 100% 的掩模都是使用多光束技術制作的,這為在高數值孔徑系統上進行更復雜、更高效的設計帶來了新的機會。

在DAC的小組演講中,D2S首席執行官Aki Fujimura討論了曲線制造的出現,以及其在提高良率、減小芯片尺寸、使用更少功率以及提高性能和可靠性方面的潛力。

“現在,任何形狀都可以在相同的時間內以相同的精度進行投影,”Fujimura說。“蒙版寫入時間不再是你試圖呈現的形狀的函數,因此無論你投射的形狀如何,蒙版成本都是恒定的。”

高數值孔徑EUV的一個關鍵目標是降低復雜性,減少晶圓制造的整體周轉時間和成本,而曲線掩模有望在這些領域取得重大改進。

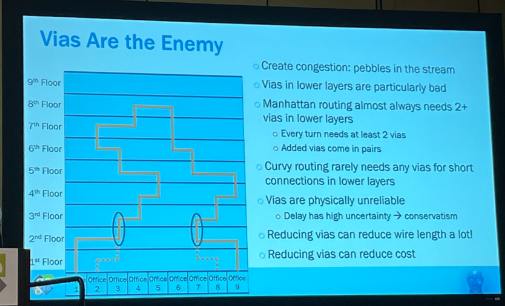

Perceive 首席執行官 Steve Teig 演示了曲線設計如何將芯片設計中的通孔數量減少多達 50%,將布線減少 30%,并將制造成本降低多達 30%(見圖 4)。“減少通孔的數量可以比你想象的更短地減少導線長度,”他說。“可以大大減少通孔的數量,使芯片更小、更快、更便宜,層數更少。這就是曲線路線的承諾。

圖 4:Perceive 的 Teig 在 DAC 2023 的 Curvy Design Panel 上解釋了為什么通孔不是您的朋友。來源: Semiconductor Engineering / Susan Rambo

曲線設計還解決了較低節點的許多隨機問題。Teig將當前的光刻工藝比作用弓箭射向目標,瞄準外緣而不是靶心。“如果你打印的是香腸形的線材而不是方形的線材,你可以瞄準中心,隨機和線邊緣粗糙度問題就變得不那么成問題了,”他說。

變化帶來了另一個挑戰。“九十度角實際上不可能在晶圓上生產,”Fujimura補充道。“我們知道這一點,但這是我們的設計,所以我們試圖盡可能地接近。在制造業中,最重要的是變化——不僅僅是你想在平均數上做到這一點,而且你希望使平均值的標準差盡可能小。

PDF Solutions總裁兼首席執行官John Kibarian強調,曲線設計有望帶來創新的未來,特別是在集成領域,從系統設計到原子重排。其獨特的優勢,例如在保持孔隙率和穩定性的同時降低軌道高度,對于未來的擴展至關重要。

然而,向曲線制造的轉變并非沒有挑戰。這種創新設計方法的廣泛采用需要對電子設計自動化 (EDA) 軟件、組織動態以及測試和測量協議進行重大更改。然而,曲線設計為半導體制造提供的增加良率、減小芯片尺寸、降低功耗以及增強性能和可靠性的承諾遠遠超過了這些障礙。

“作為集成商,未來將更多地關注創新,”Kibarian說。“如果你看看我們的行業對未來十年的看法,那就是從系統設計到光刻、計量學,再到能夠改進工藝的新材料,都是關于堆棧上下的集成。任何能讓你在保持穩定性的同時減小尺寸、降低功耗和降低成本的東西都會進入這個過程,這是曲線設計最大的潛在好處之一。

結論

光刻技術的發展是半導體縮放的基石,使電路圖案不斷小型化,電路密度和性能也相應提高。隨著更節能的EUV工具的引入、高數值孔徑工具的發展以及提高分辨率和控制尺寸的整體集成創新方法,光刻的未來看起來很有希望。

雖然當今的行業在將新材料集成到生態系統中方面取得了一些成功,但高數值孔徑器件提供的視場尺寸減小給光刻膠、計量、掩模制造和工藝控制帶來了新的挑戰。不過,如果說過去 40 年證明了什么,那就是該行業總能找到前進的道路。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論