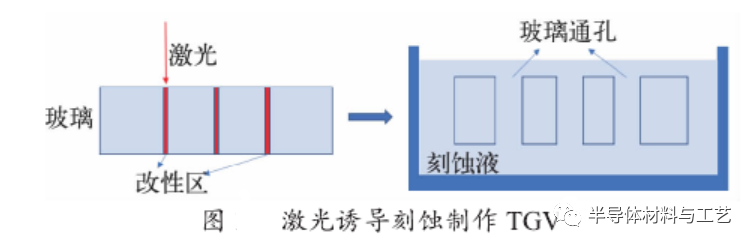

玻璃誘導刻蝕法如下:

1)?使用皮秒激光在玻璃上產生變性區域;2)將激光處理過的玻璃放在氫氟酸溶液中進行刻蝕。

1.2玻璃穿孔填孔技術

類似硅通孔的金屬填充方案也可以應用在TGV上。

另外一個將TGV填實的方案是將金屬導電膠進行TGV填實。利用金屬導電膠的優點是固化后導電通孔的熱膨脹系數可以調節,使其接近基材,避免了因CTE不匹配造成的失效。

???????除了TGV電鍍填實外,TGV也可以采用通孔內電鍍薄層方案實現電學連接。

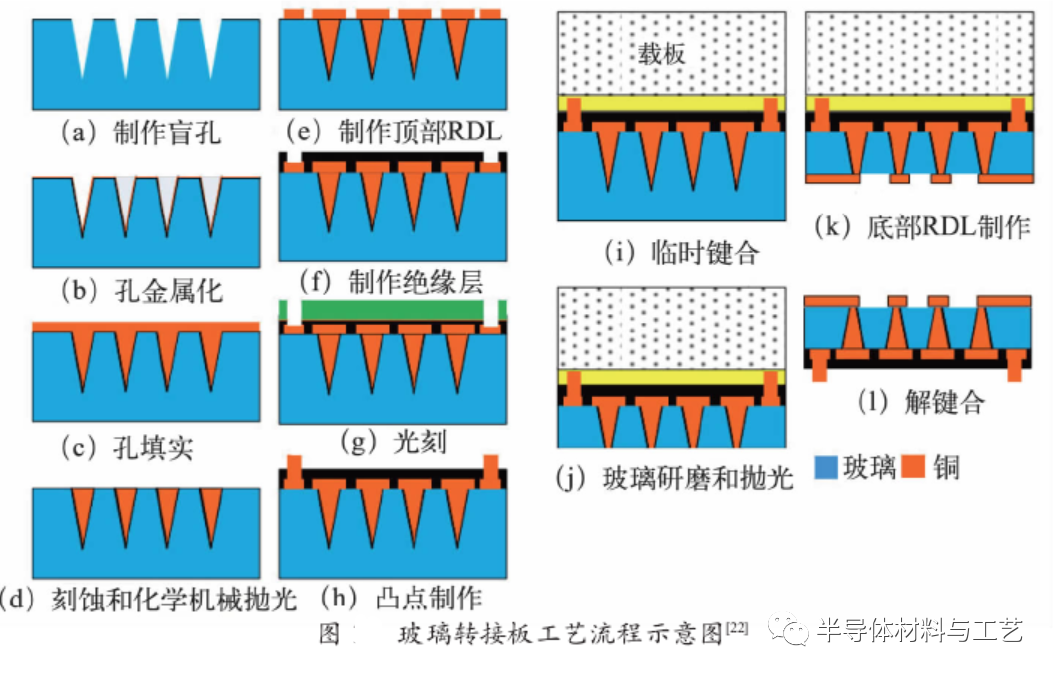

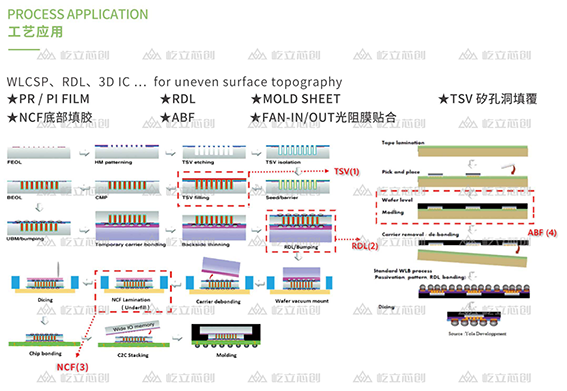

? ?1.3玻璃通孔高密度布線

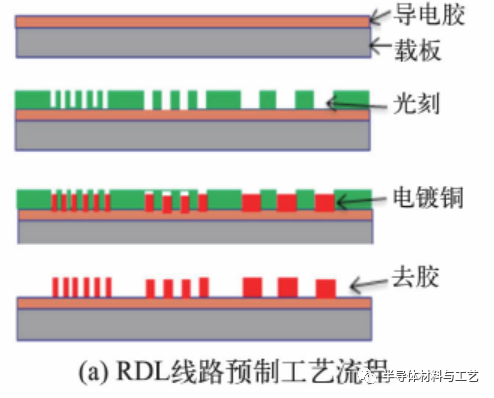

? ? ? ?線路轉移(CTT)和光敏介質嵌入法,是比較常用的方式。CTT主要包括兩個過程。一是精細RDL線預制,每一RDL層可以在可移動載體上單獨制造一層薄導電層,并在轉移到基板上之前測試或檢查細線成品率。精細線路的形成采用細線光刻和電解鍍銅的方法,并且以薄銅箔作為鍍層的種子層。工藝流程如下:

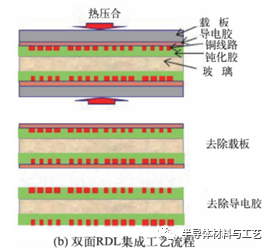

第二步就是將RDL層集成到基板上。RDL層被制造出來后,他們再使用熱壓合的同時被轉移到核心層的兩邊。步驟如下:

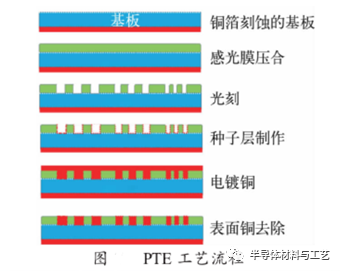

? ? ?PTE工藝可分為兩個不同的步驟,一是在光敏介質層總形成精細的溝槽;二是金屬化,包括種子層沉積、電鍍和表面除銅。工藝流程如下:

2、?國內外研究現狀

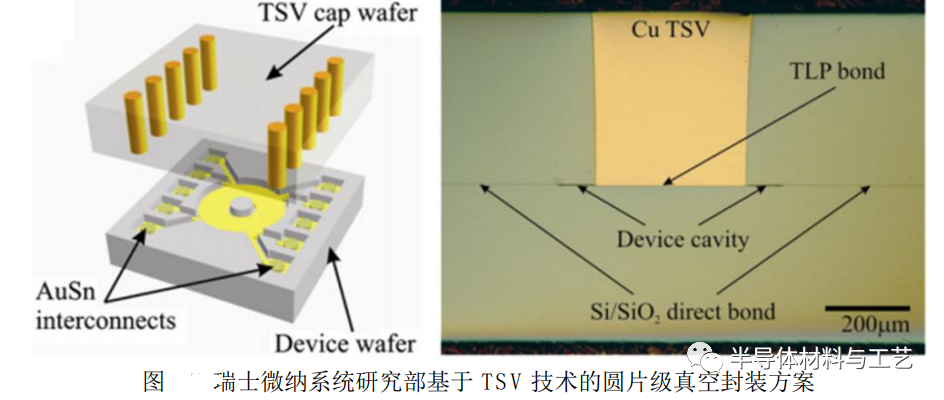

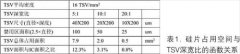

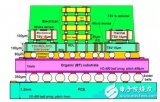

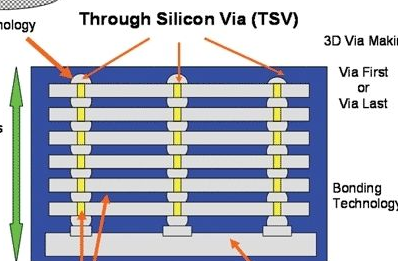

2011年,瑞士的微納系統研究部提出了如下圖所示的基于TSV技術圓片級真空封裝方案。該方案由TSV封帽與器件層兩部分構成,TSV封帽垂直導通柱是填充在硅通孔中的銅柱。器件層上制作有金錫電極與銅柱相連,從而把電信號從空腔內部的引到空腔外部,最后通過硅-硅直接鍵合實現密封。該方案氣密性很好,但是TSV封帽制作工藝復雜,熱應力大(銅柱與硅熱失配大),且硅硅鍵合對鍵合表面要求質量很高,一般加工過的硅片很難達到此要求。

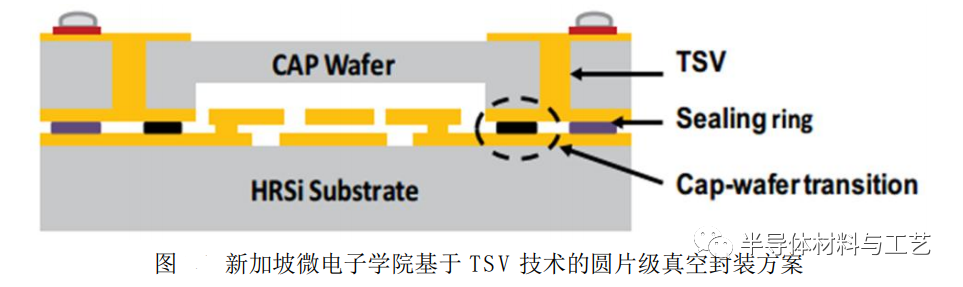

? ? ? ?2013年,新加坡微電子學院提出如下圖所示基于TSV技術的圓片級真空封裝方案。該方案由TSV封帽、硅器件層組成,TSV封帽也是由硅通孔里的銅柱做垂直導通柱,硅器件層上制作有射頻結構及金屬電極,最后使用AuSn焊料鍵合實現氣密封裝。此方案雖然也存在TSV封帽制作工藝復雜,熱應力大的問題,但采用焊料鍵合方式封裝,盡管犧牲一定的密封性,但大大降低對TSV鍵合表面質量的要求,其工業應用范圍更廣。

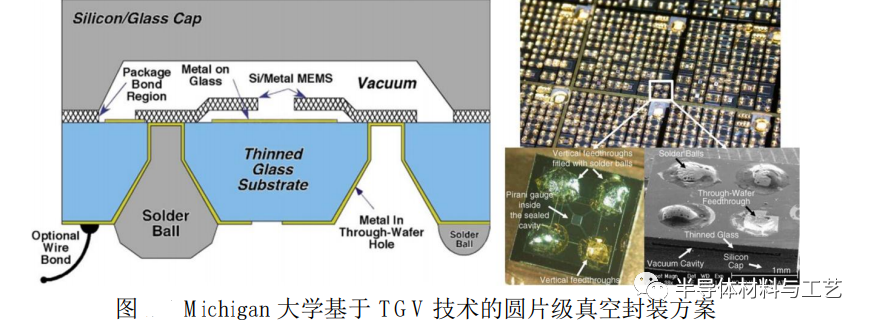

? ? ? ?從以上兩個TSV例子可以看出,TSV存在工藝復雜,熱應力過大的缺點。為解決這些問題,更好實現真空封裝,又提出了TGV技術。2008年,美國Michigan大學提出了的一種基于常規工藝TGV技術的圓片級真空封裝方案,如下圖所示。該方案由封帽,器件層以及基于常規工藝TGV技術襯底三部分構成。封帽可以為硅或玻璃,制作有空腔;器件層是硅結構層。

基于常規工藝TGV技術襯底是在玻璃片上制作電極和通孔,通孔表面沉積有金屬層,有的通孔填充焊錫球,用以形成垂直導通柱,把電信號由密封腔中引出。最后通過陽極鍵合把器件層與TGV襯底鍵合在一起,形成密封。該方案優點是通過陽極鍵合形成密封,陽極鍵合密封性好、熱失配小、污染小且一般硅片能達到陽極鍵合對表面質量的要求。

2010年,挪威的Sensonor Technologies AS提出了結構如下圖所示的一種基于玻璃回流TGV技術圓片級真空封裝方案封裝蝶翼式硅微陀螺。為減少結構應力,提高陀螺儀靈敏度,采用三層對稱結構設計,上下兩層均為TGV襯底,中間夾硅結構層。基于玻璃回流TGV襯底,是通過高溫玻璃回流,然后雙面CMP加工制成的。

TGV襯底垂直導通柱即為由回流玻璃隔離出來的硅柱,襯底上不制作金屬電極,直接用硅做電極。硅結構層采用Silicon-on-Insulator (SOI)材料和干法刻蝕制作而成,空腔制作在硅可動結構層上,通過硅-玻璃將三者陽極鍵合在一起,分別有兩次,形成密封環境。該封裝方案優勢凸出,不僅封裝應力低,而且TGV襯底工藝簡單,密封性好,熱適配小,寄生電容小。

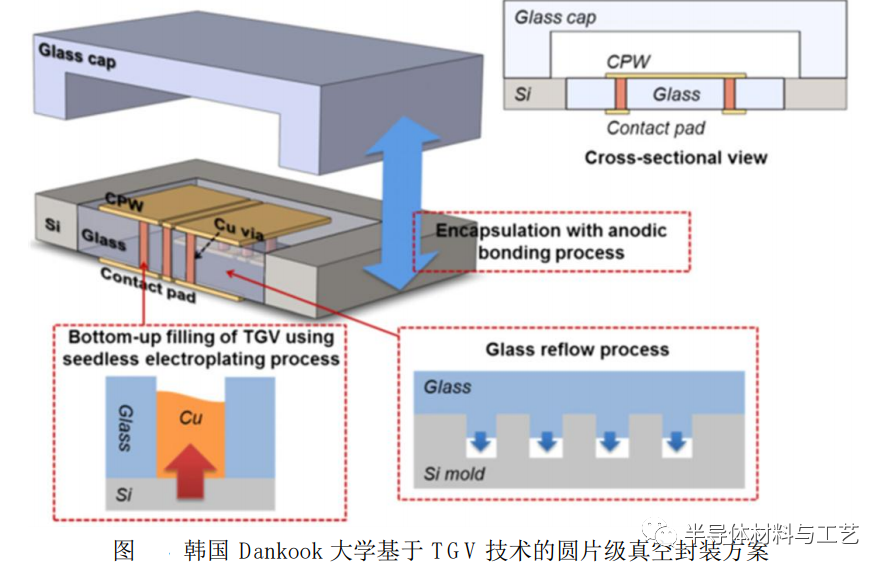

2013年,韓國Dankook大學開發出結構如圖所示的TGV技術圓片級真空封裝方案。該方案包括玻璃封帽、CPW器件層以及TGV襯底,腔體制作在玻璃封帽上。其TGV襯底與眾不同,先后采用玻璃回流工藝與電鍍銅工藝制作。簡而言之,為先利用玻璃回流工藝制作硅導通柱,然后去除硅導通柱,用電鍍銅作導通柱。CPW器件層制作在襯底密封環范圍內,最后封帽與襯底通過硅-玻璃陽極鍵合形成密封腔,并制作外部的金屬焊盤完成引線及封裝。該方案電學性能優良,但工藝復雜。

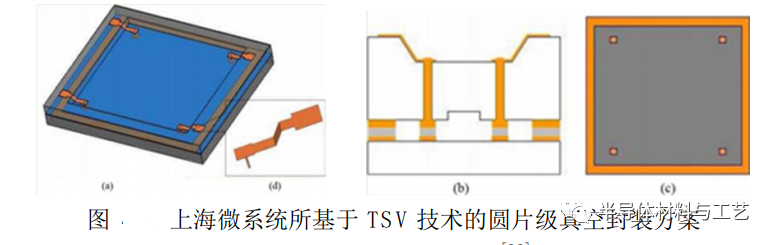

2009年,上海微系統所提出了一種結構如圖所示基于TSV技術的圓片級真空封裝方案。該方案由TSV封帽與硅襯底兩部分組成:TSV封帽采用濕法和干法刻蝕出通孔,通孔中填充銅作為導通柱,導通柱與硅通過隔離層隔離,腔體制作在TSV封帽上。硅襯底上制作有結構,通過Cu-Sn焊料鍵合與TSV封帽實現密封封裝。該方案簡單易行,但焊料鍵合用在圓片級真空封裝上會顯得鍵合密封性不夠,污染過大。

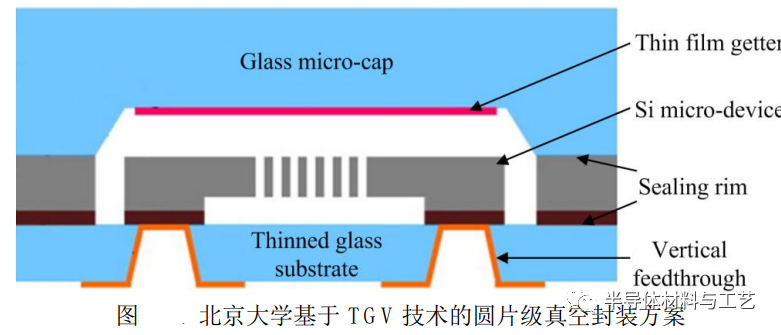

2012年,北京大學提出了結構如圖所示一種基于常規工藝TGV技術的圓片級真空封裝方案。該方案是典型的三明治式架構,由玻璃封帽、硅可動結構層、TGV襯底三層組成。硅可動結構采用干法刻蝕出可動結構;基于常規工藝TGV襯底采用濕法腐蝕出通孔與金屬沉積導通柱等工藝制作而成;空腔制作在封帽上,空腔頂部沉積有吸氣劑,保持腔體真空度。最后玻璃封帽、硅可動結構層、TGV襯底通過兩次硅-玻璃陽極鍵合封裝在一起。

3、?TGV技術的應用

? 3.1玻璃基板的三維集成無源元件

玻璃基板具有優異的高頻電學性能,因此被廣泛的應用于集成無源器件(IPD)之中。2010年,喬治亞理工的封裝中心率先完成了基于TGV的濾波器設計與制造,并與相同的硅基電感對比,展現了更好的電學特性。2017年,日月光集團在玻璃基板上實現了面板級的IPD制作工藝。該方案板材翹曲可控制在1mm以內,并且無明顯結構剝落分層現象。

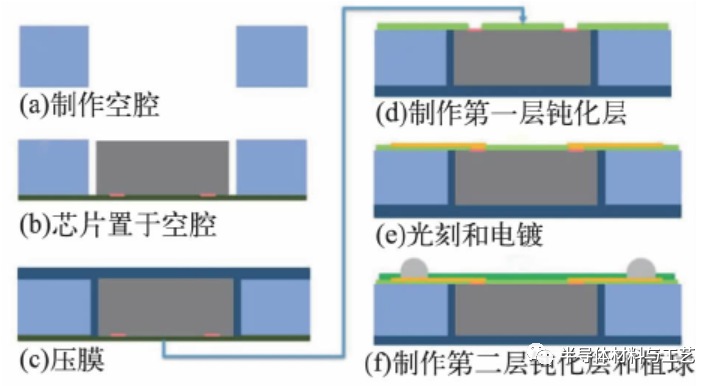

? ? ?玻璃通孔還可以在玻璃上制作空腔,進而為芯片的封裝提供一種嵌入式玻璃扇出(eGFO)的新方案。2017年喬治亞理工率先實現了用于高I/O密度和高頻多芯片集成的玻璃面板扇出封裝。該技術在70um厚、大小為300mm*300mm的玻璃面板上完成了26個芯片的扇出封裝,并有效的控制芯片的偏移和翹曲。2020年云天半導體采用嵌入式玻璃扇出技術開了77GHz汽車雷達芯片的封裝,并在此基礎上提出了一種高性能的天線封裝(AiP)方案。工藝流程如圖所示:

在厚度為180um的玻璃晶片中,先采用激光誘導玻璃變性和化學腐蝕工藝形成玻璃空腔,然后將175um高的芯片放入玻璃空腔總。通過復合材料將芯片和玻璃之間的縫隙填壓而不產生空隙,同時保護芯片的背面。對晶圓的頂面進行剝離,形成銅RDL,最后進行后續線路制作、球柵陣列(BGA)制作以及晶圓切片。

? 3.3基于玻璃通孔的MEMS封裝

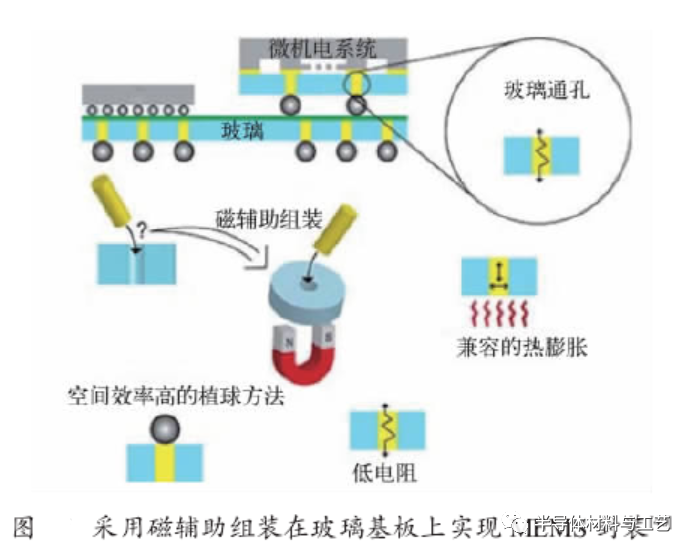

???? 2013年,LEE等利用玻璃穿孔技術實現射頻MEMS器件的晶圓級封裝,采用電鍍方案實現通孔的完全填充,通過該方案制作的射頻MEMS器件在20GHz時具有0.197dB的低插入損耗和20.032dB的高返回損耗。2018年,LAAKSO等創造性地使用磁輔助組裝的方式來填充玻璃通孔,并用于MEMS器件的封裝中。

? ? ??3.4基于TGV的集成天線

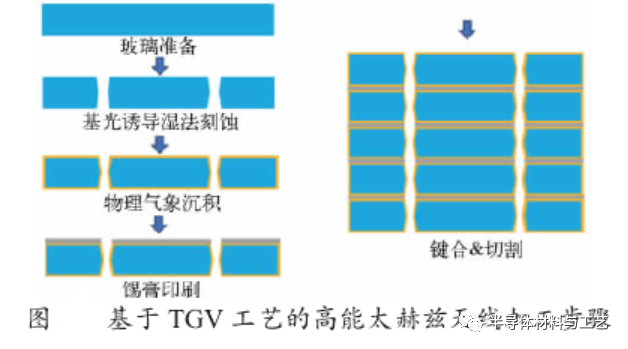

? ? ? 廈門大學的張淼創造性的引入TGV加工波導縫隙天線。首先采用激光誘導刻蝕制備波導縫隙陣列天線玻璃襯底,通過激光在玻璃上誘導產生連續性的變性區,后將變性后的玻璃在稀釋氫氟酸總進行刻蝕,由于激光作用處的玻璃氫氟酸中刻蝕速率較快,所以玻璃會成塊脫落從而形成目標通孔結構。最終刻蝕后的玻璃穿孔精度為±5μm,遠遠高于傳統機加工的精度。其次,采用物理氣相沉積對每層波導縫隙陣列天線玻璃襯底濺射銅層,經過氧等離子體清洗以徹底清除焊盤表面的有機物等顆粒,并使晶圓表面產生一定的粗糙度,為種子層的良好附著創造條件。清洗后的晶圓在烤箱150℃下烘烤60min徹底去除水汽。然后在磁控濺射設備中,晶圓表面濺射一層厚度約為5μm的銅層。最后,采用技術焊料鍵合技術將5片晶圓鍵合。用刮刀以及絲網將10μm厚度的錫焊料印刷到晶圓表面,然后在鍵合機的真空腔室中以240℃的溫度加熱,以40N的壓力壓合5min使焊料融化或相互擴散以達到鍵合的目的。工藝流程度如圖:

? ?3.5多層玻璃基板

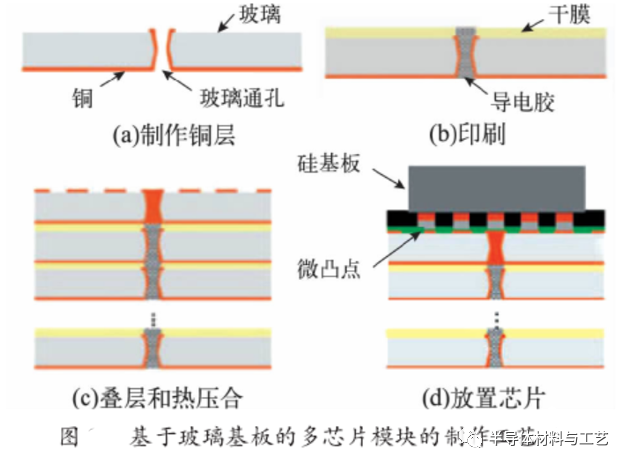

? ? ? 2018年IWAI等使用導電膠填充玻璃通孔,從而實現多層玻璃基板堆疊,在回流過程中,通過該方案制作的多層玻璃基板的翹曲比傳統有機基板要小,通過該技術可以實現高密度布線,同時具有較高的可靠性。2019年,IWAI等在多層玻璃基板的技術基礎上,完成了一個多芯片封裝的結構。其工藝流程如圖:

五、目前主要廠商的先進封裝進展

目前,國內外主要的代工廠和封測廠都有布局相應的先進封裝產能,國外的代工廠和封測廠在技術實力上處于領先地位,在2.5D/3D先進封裝的細分領域,在TSV工藝上,臺積電和英特爾處于領先地位,在TGV工藝上,領先的是康寧和德國LPTK。國內的封測廠商如長電、華天、通富微都有相關技術的研究儲備。半導體各細分子行業中,國內企業在封測領域與國際巨頭的差距相對較小,同時,國內新建的晶圓廠逐漸進入量產階段,產能較大幅度地提升將成為國內封測企業步入快速發展通道的有效驅動力,從國內幾家領先封測企業的擴產來看,預計國內先進封測企業的高端先進封裝將進一步擴大量產規模。同時,經過多年的技術和經驗積累,封測行業進入門檻逐漸提升,領先企業迎發展黃金期。

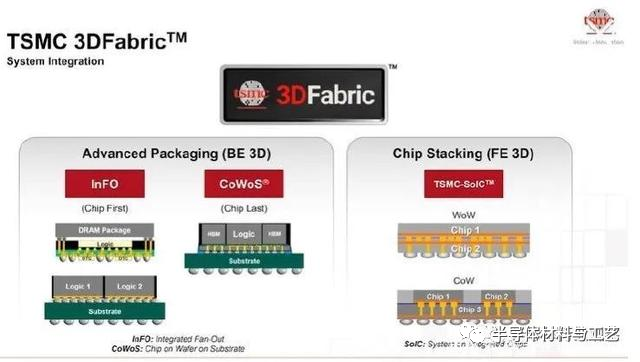

1、?臺積電

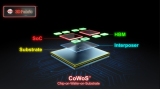

2012 年,TSMC 與 Xilinx 一起推出了當時最大的 FPGA,它由四個相同的 28 nm FPGA 芯片并排安裝在中間層上。他們還開發了硅通孔(TSV),微凸點和再分布層(re-distribution-layer:RDL),以將這些組件連接在一起。臺電基于其構造,封裝這種封裝解決方案,稱為CooS(Chip-on-Wafer-Substrate)。支持的封裝技術已成為高和高功率設計的實際行業標準。

臺積電于2017年推出了InFO(Integrated FanOut technology)技術。它使用聚酰胺薄膜代替了CoWoS中的中間層,從而降低了單體成本和高度,這也是臺積電成功應用的重要標準。貨了海量用于智能手機的InFO設計。

臺積電于2019年又推出了集成芯片系統(SoIC)技術。?借助前端(國外工廠)設備,臺積電可以非常合理的壓地,然后使用大量的吸塑的銅吸附進行焊(壓焊)設計,以更小的形狀因數,裝扮和能力。這兩種技術就逐漸演成了今天的 3D Fabric。

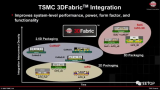

臺積電將他們的 2.5D 和 3D 封裝產品合并為一個單一的、全面的品牌3DFabric。

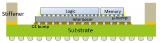

其中,2.5D封裝技術CoWoS可分為 CoWoS 和 InFO 系列。首先看CoWoS技術,可以分為以下幾種:

1)、CoWoS-S

用于die到die再分布層 (redistribution layer:RDL) 連接的帶有硅中介層的“傳統”基板上晶圓上芯片(chip-on-wafer-on-substrate with silicon interposer )正在慶祝其大批量制造的第 10 年。

2)、CoWoS-R

CoWoS-R 選項用有機基板中介層取代了跨越 2.5D die放置區域范圍的(昂貴的)硅中介層。CoWoS-R 的折衷是 RDL 互連的線間距較小——例如,與 CoWoS-S 的亞微米間距相比,有機上的間距為 4 微米。

3)、CoWoS-L

在硅 –S 和有機 –R 中介層選項之間,TSMC CoWoS 系列包括一個更新的產品,具有用于相鄰die邊緣之間(超短距離)互連的“本地”硅橋。這些硅片嵌入有機基板中,提供高密度 USR 連接(具有緊密的 L/S 間距)以及有機基板上(厚)導線和平面的互連和功率分配功能。

再看2.5D封裝技術InFO。

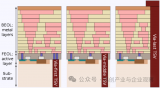

據介紹,InFO 在載體上使用(單個或多個)裸片,隨后將這些裸片嵌入molding compound的重構晶圓中。隨后在晶圓上制造 RDL 互連和介電層,這是“chip first”的工藝流程。單die InFO 提供了高凸點數選項,RDL 線從芯片區域向外延伸——即“扇出”拓撲。如下圖所示,多die InFO 技術選項包括:

InFO-PoP:“package-on-package”

InFO-oS:“InFO assembly-on-substrate”

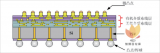

? ? ? 臺積電的3D封裝技術則是SoIC。據臺積電介紹,公司的3D 封裝與 SoIC 平臺相關聯,該平臺使用堆疊芯片和直接焊盤鍵合,面對面或面對背方向 -表示為 SoIC 晶圓上芯片(chip on wafer)。硅通孔 (TSV) 通過 3D 堆棧中的die提供連接。SoIC 開發路線圖如下所示——例如,N7-on-N7 芯片配置將在 21 年第四季度獲得認證。

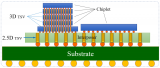

2、英特爾

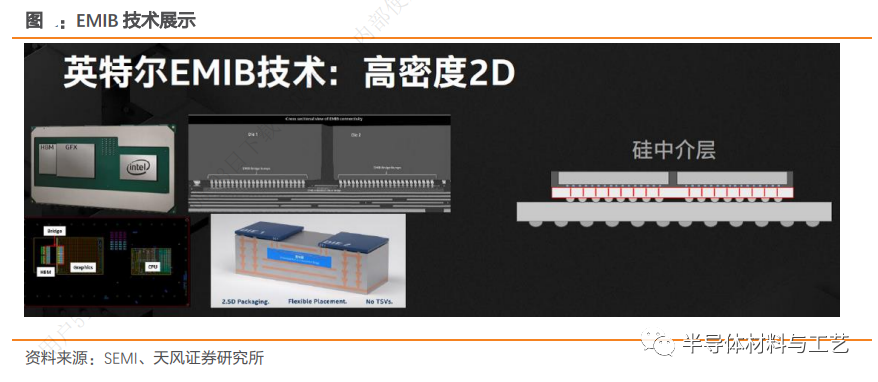

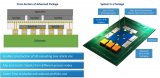

? ? ?在2D的平面多芯片封裝,英特爾獨有的競爭優勢是嵌入式多芯片互連橋接(EMIB)技術,可以實現更好的導線密度。在硅中介層硅通孔上放不同的裸片連接到整個基板,只需在局部進行高密度布線,而不必在全部的芯片上進行高密度布線,使成本大幅降低同時性能也得到優化。

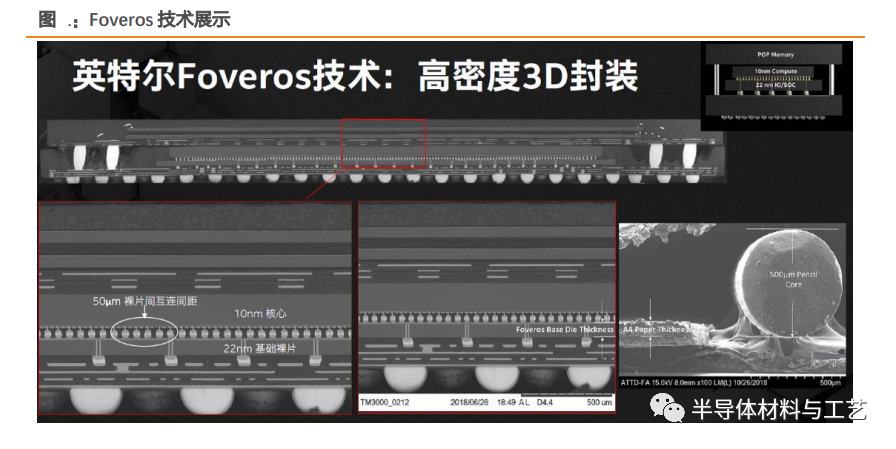

而在3D高密度微縮方面,英特爾的Foveros技術將多個單片連接到基礎裸片,然后進行底層填充實現中間互連并進行注塑來保護整個芯片,使用焊接的技術已經可以做到20-30微米,而通過無焊料銅與銅的接口互連可突破20微米的瓶頸。

而在未來,封測技術相比較于現有的Foveros技術會更進一步。相比較于現有的技術,未來的凸塊間距將會由50um縮小至10um,電路將更小更簡潔,能耗也會更低。

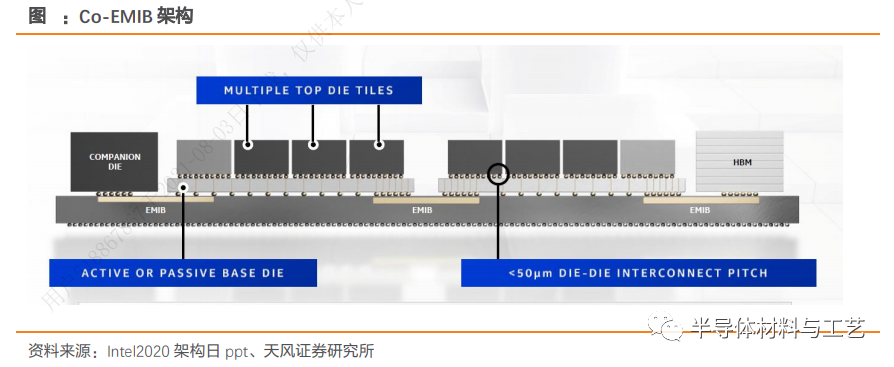

Foveros技術與EMIB集成產生了Co-EMIB(通過EMIB和Foveros兩個技術之間的集成把2D和3D芯片進行融合)。Co-EMIB可以把超過兩個不同的裸片進行水平和垂直方向疊加,以實現更好的靈活度。

?

? ? ? ?全方位互連(ODI)改變了常規疊加方式下基礎裸片尺寸必須大于上面疊加所有小芯片總和的限制。ODI的架構通過傳統的硅通孔技術,使頂層小芯片可以與下方的芯片互連,這樣就可以通過底層封裝直接對上方小芯片進行供電,并保持上、下方裸片間直接互連。Adel Elsherbini介紹,通過這種并排互連形式延遲可下降2.5倍,功耗可以降低15%,帶寬可以提高3倍。根據英特爾對先進封裝的路線預測,在未來凸塊間距將縮小至10um級別,密度將達到10000每平方毫米,能耗也會降低至0.05pj/bit。而ODI和CO-EMIB技術的應用,也會使先進封測進一步擴展應用范圍。

先進封裝的制程演進同先進制造工藝的制程呈現出同步趨勢。在臺積電等半導體制造廠制程逐漸進入5nm以下之際,先進封裝的凸塊間距也會逐漸進入10-20um區間。

3、?康寧

康寧公司是全球頂尖材料科學創新公司之一,在逾160年間提出多項玻璃解決方案,包括用于電子應用方面的液晶顯示器(LCD)基板,以及用于電視機、智慧型手機和平板電腦等消費性電子裝置,極為耐用的保護玻璃。

熔融制程為康寧的專利創新技術核心。這項高度精準且自動化的熔融下拉制程,生產出表面極為純凈光滑又平坦,且尺寸穩定的玻璃基板——這剛好是3DIC基板所要求的特性。

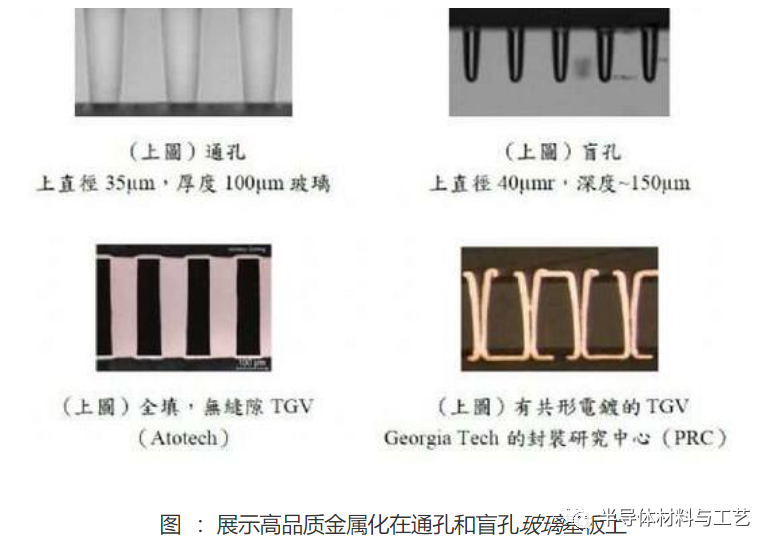

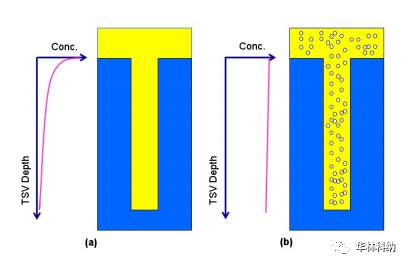

能夠利用現有晶圓和面板設備制程是非常重要的一件事,盲孔填滿金屬化是最適用于現行以晶圓為基礎的設備,而通孔金屬化則最適合用于許多以面板為基礎的制程。康寧已開發出制作高品質孔洞的先進制程,能在薄型(像是100μm)和厚型(例如700μm)玻璃上制作通孔和盲孔(請上圖)。

再者,康寧已與產業領導廠商進行密切合作,運用以晶圓與面板為基礎的金屬化方式來填充玻璃孔洞。TGV基板的填充方式與終端應用息息相關,成本、生產能力、導電性、密閉度等要求會影響到金屬化的方式。因此康寧與產業多個單位合作,像是RTI、Atotech、i3Electronics、工研院(ITRI)、GeorgiaTech的封裝研究中心等,證明出完整的金屬化技術的適用性和可用性。此用來驗證的玻璃基板晶片測試結果顯示出,相對于矽基板,使用玻璃孔洞能達到更好的電性、熱和可靠性表現(請見上圖)。

利用面板相關制程來達到經濟規模制造的能力,是另一項落實成本效益的重要因素。目前業界已有許多設備能被應用來制造面板形式的穿孔玻璃載板和其對應的電子元件,包括填孔步驟和微影制程。

日前康寧已與RudolphTechnologies、i3Electronics與Atotech完成合作,證明出運用現有機臺設備來制造面板形式的穿孔玻璃載板和其電子元件,包括填孔步驟和微影制程。RDL(RedistributionLayers)的結果顯示出,能準確將金屬鍍在玻璃上(請見上圖)。

據麥姆斯咨詢報道,Corning Incorporated(康寧)和Menlo Micro(以下簡稱Menlo)近日聯合宣布,Menlo革命性數字微開關(DMS)技術平臺的開發實現了重要的里程碑,Menlo將重塑電子系統最基本的構建模塊——電子開關。兩家公司共同發布展示了成功整合的玻璃通孔(TGV)封裝技術,使Menlo的高性能RF和功率產品擴展至超小型晶圓級封裝。

TGV相比傳統的鍵合封裝技術,使Menlo的產品尺寸縮小了60%以上,使其更理想地適用于那些信道密度增長,同時尺寸、重量、功率和成本降低的非常重要應用。Menlo將在本周于美國費城舉辦的IEEE MTT國際微波會議上展示這項技術。

此外,除了顯著的尺寸減小,TGV還為Menlo的DMS產品帶來的重要的性能優勢。通過更短且良好控制的金屬化通孔替代鍵合,現在Menlo得以降低75%以上的封裝寄生效應。這將幫助Menlo的產品支持更高的頻率,這對于先進的無線通訊系統、測試儀器以及眾多的航空和國防應用,正變得越來越重要。與此同時,玻璃相比硅等傳統的基板材料具有獨特的性能,可實現更低的RF損耗和更高的線性度,意味著系統將獲得更低的功耗和更高的整體效率。

通過利用TGV封裝技術,Menlo正在開發覆蓋DC~18 GHz帶寬的RF產品,并有能力逐步擴展至50 GHz以上。其DMS平臺可為RF和AC/DC產品實現數十種高價值應用,包括電池管理、家居自動化、電氣化汽車、軍事和專業無線電、無線基站以及物聯網等廣泛市場。

4、?德國LPKF

LPKF深耕激光領域多年,對于如何將激光作為工具集成為功能強大的設備有著豐富的技術經驗。LPKF激光系統立足于助力高科技領域的進步。無論是移動系統、通信系統、電力以及數字娛樂等,最終目標都是加工產品的速度更快、尺寸更小、更節能。德國LPKF始終保持著在激光技術領域的領先地位。我們的激光系統在印刷電路板、微芯片、汽車零部件、太陽能電池板以及許多其他零部件的工藝制造中都起著至關重要的作用。

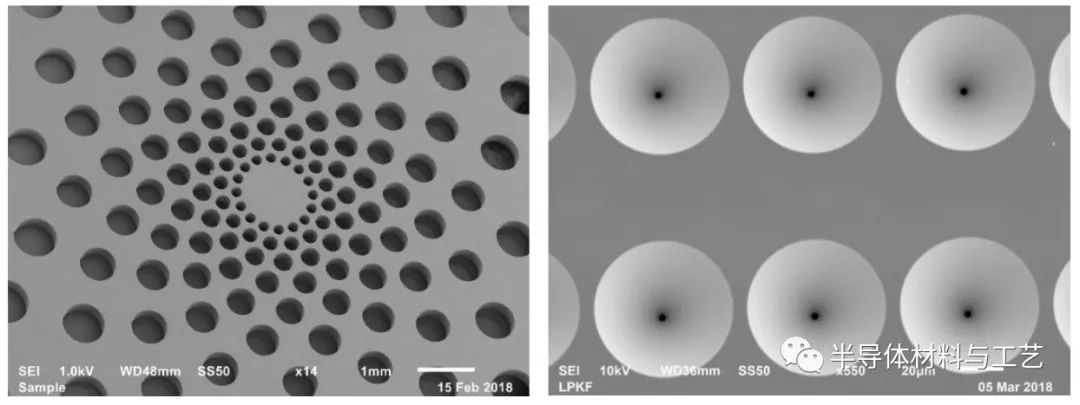

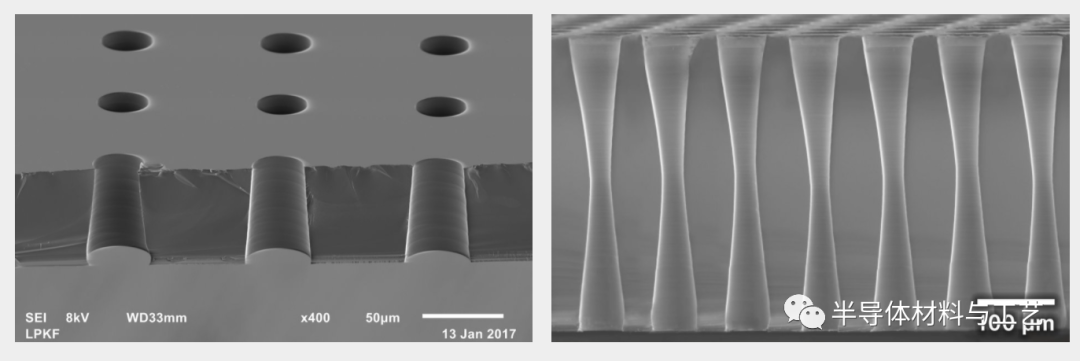

憑借幾十年的激光加工經驗,LPKF提供了前沿的技術解決方案,具有更高的精度、成品率和成本效率等系統優勢,引領不斷走向小型化的趨勢。該產品包含許多優勢:一種新型玻璃通孔(TGV)加工工藝全面開啟了薄片玻璃作為封裝基板的潛力。厚度介于50微米至500微米之間的薄片玻璃是一種非常適用于高密度高頻應用的封裝基板材料。LPKF運用激光這種非接觸精密加工工具開發的創新LIDE 工藝能夠以無以倫比的效率和質量微加工玻璃通孔。

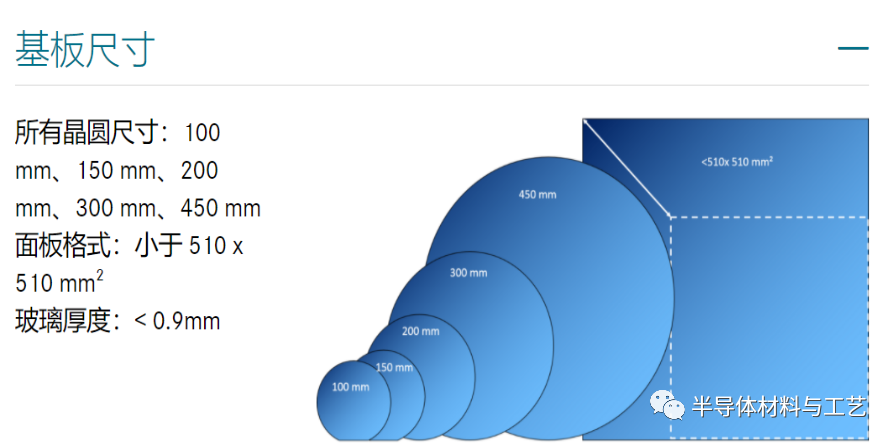

LPKF的最小通孔直徑為10 μm。通常,一個基板上的所有微孔都顯示相同的直徑。通過應用多次蝕刻運行,不同的直徑是可能的。縱橫比在 1:10 的范圍內,但根據玻璃類型,它也可以高達 1:50。LIDE 生成的微孔側壁光滑、無裂紋、無碎屑和無應力,可實現可靠的金屬化。錐角在0.1°-30°之間。LIDE 制造的微孔通常呈沙漏形狀。通過將蝕刻限制為僅從先前修改過的玻璃的一側進行,V 形微孔是可能的。加工的尺寸選擇如圖:

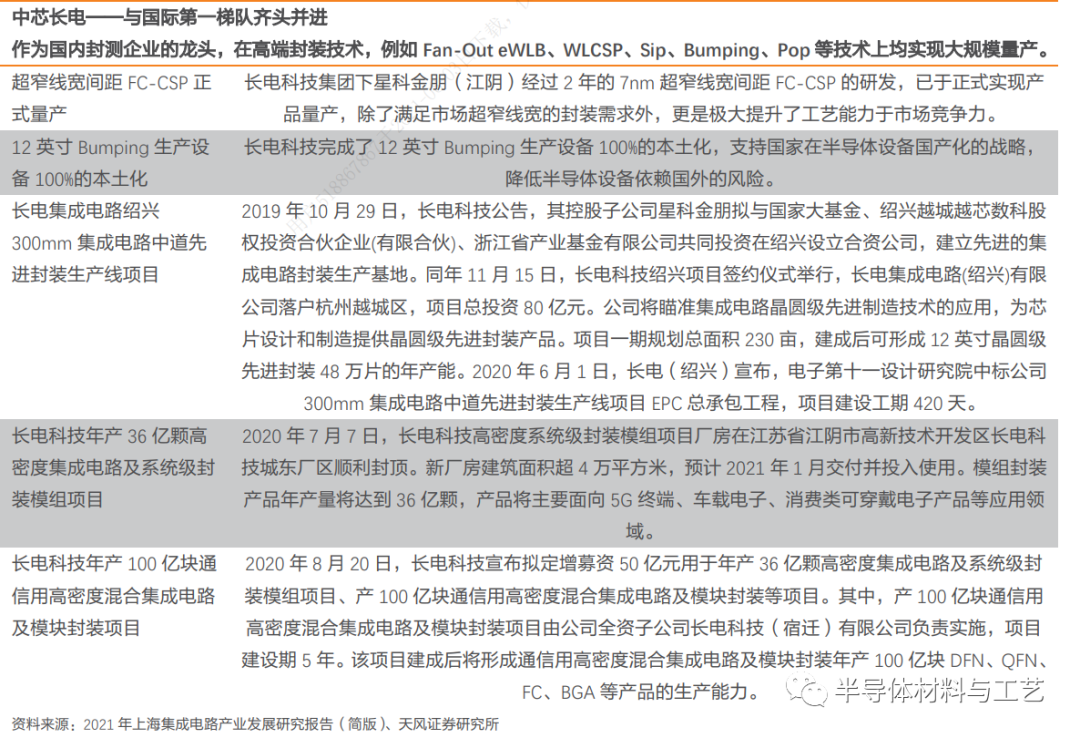

5、?中芯長電

? ? ?長電科技是全球領先的封測廠商,聚焦關鍵應用領域,在5G通信類、高性能計算、消費類、汽車和工業等重要領域,業務覆蓋高/中/低端全品類,已成為中國第一大和全球第三大封測企業。公司封測產能多地布局,互為補充,各具技術特色和競爭優勢;公司在主要封裝領域內掌握多項核心技術,在先進封裝技術覆蓋度上與全球第一的日月光集團旗鼓相當,具備行業領先的SiP、WL-CSP、FC、eWLB、PiP、PoP及2.5/3D等高端封裝技術,并定增50億元加碼SiP、QFN、BGA等高端封裝產能。公司與中芯國際戰略互通,可實現代工+封測一體化協同發展。

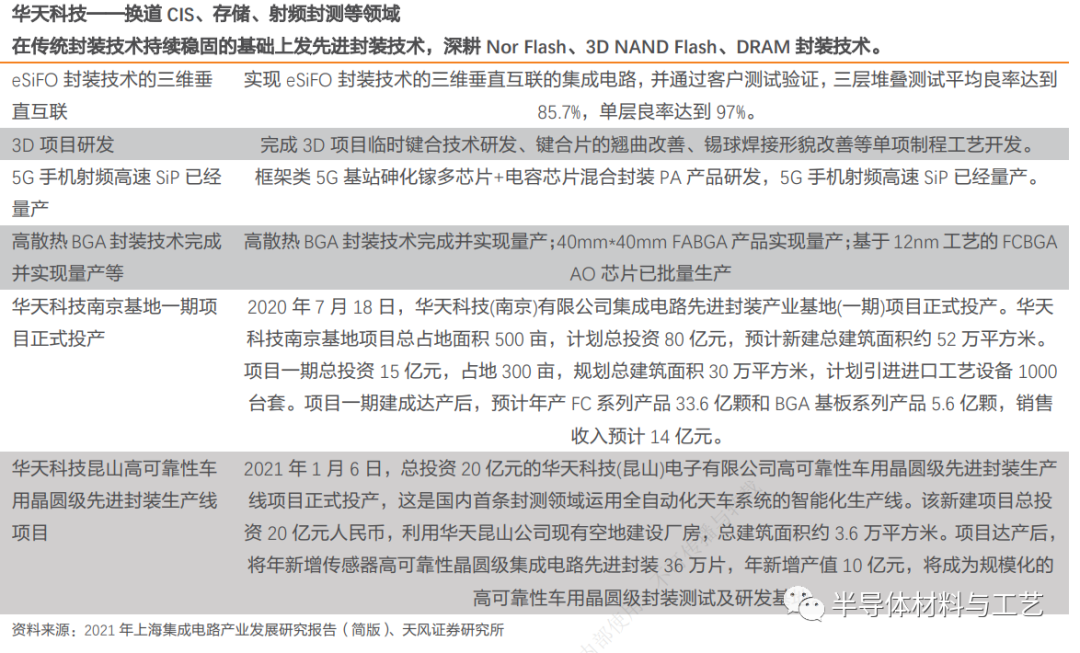

6、 華天科技

?公司在產業布局方面,積極推進先進封裝基地建設,近年來先后投資擴建了昆山、寶雞、南京等基地,打通了CIS芯片、存儲器、射頻等多種高端產品的生產線。2020年7月18日華天科技南京基地舉行了一期項目投產儀式,一期項目已竣工面積16.3萬平方米,實現FC和BGA系列產品年封測量可達40億只,今年可實現產值2億元以上。

?研發方面公司重視新產品、新技術、新工藝的研發,研發支出金額逐年增加,已自主研發出了SiP、FC、TSV、MEMS、Bumping、Fan-Out、WLP等高端封裝技術和產品。自2019下半年來,國內半導體封測行業逐步回暖,未來有望隨著新型應用領域和先進封測技術的發展進入新一輪增長。華天科技作為國內領先的集成電路封測企業,產品線布局豐富,技術水平行業領先,有望持續受益行業景氣度及國產替代加速影響,未來發展前景廣闊。

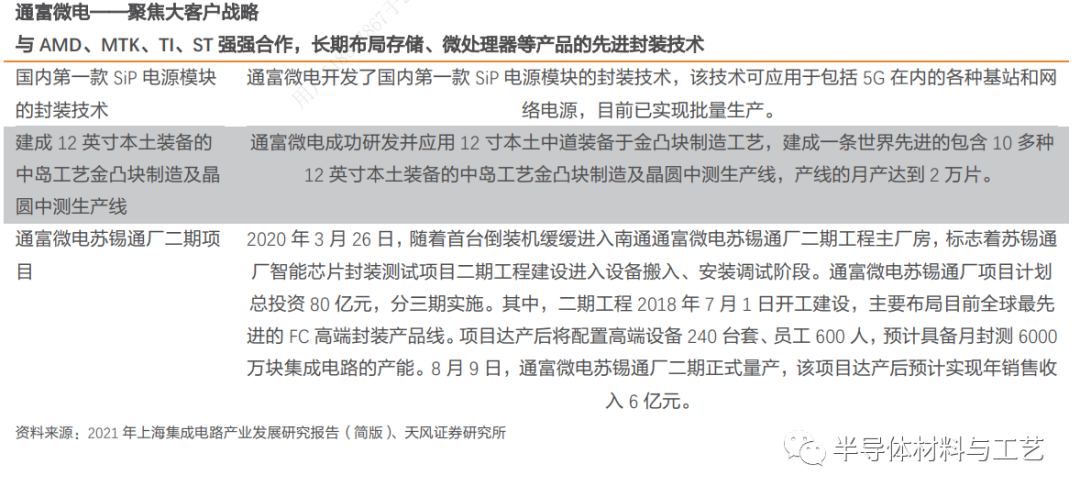

7、通富微電

通富微電為半導體封測龍頭,與AMD、MTK等大客戶共同成長。公司為全球第五大、國內第二大封測廠商,在封測技術上布局全面。早期公司以傳統封裝技術為主,2016年收購AMD蘇州、檳城兩大封測廠,得以深度綁定AMD供應鏈并占據AMD封測訂單的大部分份額。同時公司憑借在高端封裝領域的實力,成為MTK在中國大陸的重要封測合作方。展望未來,公司有望伴隨大客戶份額的提升和市場整體規模的擴大而迎來加速成長。

先進封裝因5G、AI的應用迎來快速成長,公司技術領先有望充分受益。傳統封測市場近年增速較為平穩,2011-2018年市場年復合增速在3%,至2018年空間達560億美元。然而,隨著摩爾定律的放緩,半導體性能的提升越來越多依賴于封裝技術的進步,從而對封裝技術提出更高要求。具體來看,隨著5G、AI芯片的大規模應用,以及終端設備小型化趨勢的演繹,全球先進封裝市場有望快速成長:據Yole預計,先進封裝市場至2024年有望達440億美元,2018-2024年CAGR達8%。公司通過對AMD蘇州、檳城廠的收購,增強了先進封裝的技術實力,未來有望充分受益于先進封裝市場的快速增長。

審核編輯:劉清

電子發燒友App

電子發燒友App

評論