近幾年,硅通孔 (through-silicon vias,TSV) 技術(shù)發(fā)展迅速,擁有著低功耗、小外形、高性能和高堆疊密度等優(yōu)勢的它得到工業(yè)界的廣泛認(rèn)可,具有延續(xù)摩爾定律發(fā)展的潛力。本文中作者介紹了 TSV 的工藝流程和關(guān)鍵技術(shù),對蝕刻、分離、金屬填充,以及銅暴露等重要工藝流程進(jìn)行了詳細(xì)描述。

1 概述

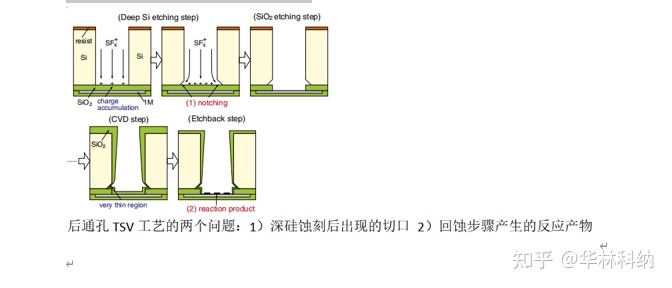

具有低功耗、小外形、高性能和高堆疊密度等特點(diǎn)的三維集成電路被視為有希望打破摩爾定律局限性的代表。要實(shí)現(xiàn)三維集成,需要用到幾個關(guān)鍵技術(shù),如硅通孔(TSV),晶圓減薄處理,以及晶圓/芯片鍵合。TSV 互連具有縮短路徑和更薄的封裝尺寸等優(yōu)點(diǎn),被認(rèn)為是三維集成的核心技術(shù)。在三維集成中 TSV 技術(shù)可分為三種類型:在 CMOS 工藝過程之前在硅片上完成通孔制作和導(dǎo)電材料填充的是先通孔技術(shù);而中通孔,在CMOS制程之后和后端制程(BEOL)之前制作通孔。最后一種后通孔技術(shù)是在 CMOS 工藝完成后但未進(jìn)行減薄處理時制作通孔。最終技術(shù)方案的選擇要根據(jù)不同的生產(chǎn)需求。

TSV 技術(shù)已經(jīng)應(yīng)用于很多產(chǎn)品,如 MEMS,手機(jī),CMOS 圖像傳感器(CIS)、生物應(yīng)用設(shè)備和存儲器。由此可見,如今已經(jīng)有了較多的 TSV 技術(shù)方面的研究和成果。目前,由于相對造價較高,三維集成中 TSV 技術(shù)的成果和先進(jìn)封裝技術(shù)的運(yùn)用還沒有普及。在本文中,作者綜述了 TSV 的工藝流程和關(guān)鍵技術(shù),對深反應(yīng)離子刻蝕(DRIE)制作通孔,絕緣層內(nèi)襯、阻擋層和種子層,通孔填充,化學(xué)機(jī)械拋光(CMP),和 Cu 暴露等重要過程進(jìn)行了詳細(xì)介紹。

2 TSV 結(jié)構(gòu)和 TSV 制造的工藝流程

2.1 TSV 結(jié)構(gòu)

TSV 結(jié)構(gòu)如圖 1[1]所示,在硅板上面有加工完成的通孔;在通孔內(nèi)由內(nèi)到外依次為電鍍銅柱、絕緣層和阻擋層。絕緣層的作用是將硅板和填充的導(dǎo)電材料之間進(jìn)行隔離絕緣,材料通常選用二氧化硅。由于銅原子在 TSV 制造工藝流程中可能會穿透二氧化硅絕緣層,導(dǎo)致封裝器件產(chǎn)品性能的下降甚至失效,一般用化學(xué)穩(wěn)定性較高的金屬材料在電鍍銅和絕緣層之間加工阻擋層。最后是用于信號導(dǎo)通的電鍍銅,最初由于一般的 TSV 結(jié)構(gòu)的尺寸較大,通孔內(nèi)的填充材料使用過熱膨脹系數(shù)比較低的鎢,但是鎢的電導(dǎo)率比較低,電導(dǎo)率較高的銅逐漸將之取代,成為工業(yè)界通孔填充材料的首選[1]。

2.2 TSV 制造的工藝流程

TSV制造的工藝流程如圖 2[2]所示。依次為:

(1)先使用光刻膠對待刻蝕區(qū)域進(jìn)行標(biāo)記,然后使用深反應(yīng)離子刻蝕(DRIE)法在硅晶圓的一面刻蝕出盲孔。

(2)依次使用化學(xué)沉積的方法沉積二氧化硅(SiO2)絕緣層、使用物理氣相沉積的方法沉積鈦(Ti)作為阻擋層、銅(Cu)作為種子層。

(3)選擇一種電鍍方法在盲孔中進(jìn)行填充電鍍銅。

(4)使用化學(xué)機(jī)械拋光(CMP)法將硅晶圓表面上多余的銅去除。

(5)在硅晶圓上有盲孔的一面上制作電路層(RDL)。

(6)使用可溶膠把硅晶圓上有電路層(RDL)的一面粘合在載體晶圓上。

(7)使用化學(xué)機(jī)械拋光(CMP)和背面磨削法將盲孔中電鍍銅柱的另一端暴露出來。

(8)在暴露出電鍍銅后的硅晶圓的背面開始制作電路層和微凸點(diǎn)下的銅墊(UBM)。

(9)在硅晶圓背面開始制作微凸點(diǎn)。

(10)將制作了微凸點(diǎn)的晶圓從載體晶圓上取下然后清除晶圓正面的可溶膠[1]。

3 TSV 制作流程中關(guān)鍵技術(shù)

3.1 TSV 刻蝕

TSV 刻蝕是三維集成的關(guān)鍵技術(shù),并且目前深硅刻蝕首選技術(shù)為干法刻蝕或稱博世刻蝕。博世刻蝕工藝的刻蝕速率高達(dá) 5~10μm/min,對光刻膠的選擇性為 50~100,對氧化物掩膜的刻蝕率高達(dá)200。博世工藝包括以下流程:(1)利用六氟化硫(SF6)作為蝕刻劑進(jìn)行硅刻蝕;(2)填充八氟環(huán)丁烷(C4F8)氣體,以產(chǎn)生良好的鈍化膜來保護(hù)刻蝕出的側(cè)壁;(3)用定向離子進(jìn)一步刻蝕六氟化硫(SF6)等離子體中的鈍化層和硅層。然后,使用 O2和 Ar 等離子體清洗鈍化層[2,3]。然而,這種工藝造成側(cè)壁缺口粗糙,可能會造成接下來的步驟出現(xiàn)差錯,引發(fā)漏電和可靠性問題。在深硅刻蝕中,側(cè)壁粗糙度受刻蝕和鈍化到兩個流程的影響[4]。側(cè)壁粗糙會增大 TSV 的空隙,進(jìn)而影響到絕緣層、阻擋層和銅種子層的覆蓋范圍。因此,隨著 TSV 尺寸的減小,側(cè)壁糙度需要控制在最小。

3.2 TSV絕緣層

TSV 的金屬填充需要用到絕緣層來對硅襯底進(jìn)行充分的電氣隔離。絕緣層的工藝要求包括良好的階梯覆蓋率,無漏電流,低應(yīng)力,高擊穿電壓,以及不同的 TSV 集成引起的加工溫度的限制[5]。二氧化硅(SiO2)或氮化硅(Si3N4)是常用于等離子體增強(qiáng)化學(xué)氣相沉積(PECVD)或減壓化學(xué)氣相沉積(SACVD)的絕緣層。然而,當(dāng) TSV 直徑小于 3 μm 時,絕緣層更適用于原子層沉積(ALD)。ALD有幾個優(yōu)勢,如較低的熱預(yù)算,比現(xiàn)有流程更好的階梯覆蓋率,無需再進(jìn)行表面處理,并且由于較薄的絕緣層,降低了 TSV 的 CMP 加工時間。

3.3 TSV阻擋層和種子層

接下來的過程是阻擋層沉積,目的是防止銅原子在溫度 400 ℃下的退火過程的 TSV 中擴(kuò)散。另外,阻擋層也作為絕緣層和銅層之間的粘合層。常見的作為阻擋層的的材料是 Ti、Ta、TaN、TiN;根據(jù) TSV 的尺寸來選擇物理氣相沉積(PVD)、化學(xué)氣相沉積(CVD)或原子層沉積(ALD)法來實(shí)現(xiàn)。

金屬阻擋層使用 PVD 沉積,如鉭和鈦。溫度要求低是這種方法最大的特點(diǎn),但是其階梯覆蓋率也低,很容易產(chǎn)生較高縱橫比(>10:1)的TSV[6]。沉積較厚的金屬阻擋層可以克服階梯覆蓋低的缺點(diǎn),但會使生產(chǎn)成本變高。TiN 或 TiN 阻擋層可以用化學(xué)氣相沉積法沉積,具有均勻性好的優(yōu)點(diǎn)、但需要較高的加工溫度。

在下面的過程中,銅種子通常采用物理氣相沉積法沉積在 TSV 中。在 IMEC 研究中[7],采用 ALD 法 TiN 作為阻擋層,制造了均勻性約 80%,尺寸 2×30 μm 的 TSV(縱橫比 =15)。成本和減少阻擋層和種子層過程的熱預(yù)算是 TSV 應(yīng)用中的關(guān)鍵挑戰(zhàn)。

在后端工序互聯(lián)之后用于設(shè)備可靠性檢測的溫度是一個值得關(guān)注的問題。采用低溫下進(jìn)行的全濕法對高縱橫比的 TSV 的阻擋層和銅種子層實(shí)現(xiàn)無電鍍沉積,用金納米粒子(Au NPs)或鈀納米粒子(Pd NPs)作為催化劑[8]實(shí)現(xiàn)鈷-鎢和銅的阻擋層/種子層的無電鍍沉積。一個 TSV 不同位置的吸附鈀納米粒子在室溫下 3 小時后的形態(tài),如圖 3 所示。Pd NPs 沉積均勻地分布在整個尺寸為 2×24 μm 的 TSV 中,沒有觀察到鈀結(jié)塊。盡管全濕法阻擋層和種子層在較低溫度下有較好的階梯覆蓋率,但它的可靠性還需要更多的實(shí)驗來證明。

3.4 TSV 填充

TSV 填充電鍍銅有三種方法:共形電鍍[9,10],自下而上的密封凸點(diǎn)電鍍[11,12],和超共形電鍍[13]。電鍍方法是以各種三維集成應(yīng)用為基礎(chǔ)的。總的來說,TSV 的結(jié)構(gòu)是深度在 10 到 200μm 之前的典型的圓柱形孔。TSV 的深度取決于芯片或晶圓鍵合時的所需厚度,而 TSV 縱橫比的大小則由介電膜、阻擋層和種子層和填充過程決定的。

3.4.1 共形電鍍

共形度銅與晶圓級芯片規(guī)模封裝中線路鍍銅相似。以 CIS 應(yīng)用作為一個例子,它的主要過程包括硅的深反應(yīng)離子刻蝕到 CMOS 金屬層,通孔的氧化物隔離,阻擋層和種子層 PVD 沉積,最后對 RDL[14]共形鍍銅。在抗蝕劑掩模中銅厚 5~10μm[9]。然而,由于銅種子層的不連續(xù)性,僅有縱橫比為 3 的 TSV 得以應(yīng)用。

3.4.2 自下而上密封凸點(diǎn)電鍍

TSV 自下而上密封凸點(diǎn)電鍍法的一個優(yōu)點(diǎn)是能夠有效避免通孔填充過程中產(chǎn)生空隙[15,16]。此外,自下而上填充法適合后通孔工藝。它通常需要在底部的銅種子層的臨時鍵合或粘貼技術(shù)來完成填充過程。載體晶圓的去除會帶來額外的花費(fèi)和可靠性問題,因此圖 4 展示了一種新型的 TSV 自下而上密封凸點(diǎn)電鍍銅填充法。該工藝流程為:(1)TSV 刻蝕,(2)減薄,(3)氧化隔離,(4)種子層沉積,(5)光刻膠標(biāo)記,(6)制造密封凸點(diǎn),(7)TSV 凸點(diǎn)電鍍,(8)最終刻蝕。掃描電鏡、光學(xué)顯微鏡和 X 射線分析都能觀察到,自下而上填充法不會產(chǎn)生缺陷。如圖 5 所示,(a)干法刻蝕的 25 μm TSV 剖面;(b)TSV 填充之前的密封凸點(diǎn)制造;(c)X 射線下觀察的 TSV 無縫填充;(d)黑色的點(diǎn)是 TSV,白色區(qū)域是 SiO2,灰色的是金屬線;(e)兩側(cè)有銅凸點(diǎn)的 TSV 截面;(f)帶有銅凸點(diǎn)的最終 TSV 結(jié)構(gòu)[12]。用一步電鍍法制作 TSV 和凸點(diǎn)結(jié)構(gòu)來簡化工藝流程,使其適用于三維集成方案中的后通孔方法。

3.4.3 超共形電鍍

超共形電鍍銅填充的適用尺寸有較大的范圍,從鑲嵌尺寸到用于應(yīng)用設(shè)備的較大尺寸。通過 X 射線觀測到銅覆蓋層和阻擋層用 CMP 去除后,TSV 中沒有縫隙。

圖 6 [17]顯示了 TSV 填充的原理,包括電鍍方法的特點(diǎn)和有機(jī)添加劑的性能[17]。圖中,(a)未優(yōu)化直流電鍍;(b)附加過程;(c)PPR 電流波形法。由于標(biāo)準(zhǔn)直流電鍍中的夾斷問題,電鍍方法的選擇是 TSV 填充的一個關(guān)鍵因素,如圖 6a 所示。圖 6b 展示了添加劑沉積的結(jié)果。電鍍方法的確定時用到了四個重要參數(shù),包括反向脈沖時間(TR),目前暫停時間(TOFF),正向脈沖時間(Tf),和相應(yīng)的電流密度(JF,Jr)常數(shù),如圖 6C 所示[18,19]。

此外,三步 PPR 電流波形法減少了銅填充時間和 TSV 填充[20,21]的缺陷。然而,由于使用可以減少通孔側(cè)壁銅離子的脈沖反向電流,填充高縱橫比的 TSV 需要很長的時間。因此,三維集成中縮短 TSV 填充時間是很有必要的。提高充填效率的優(yōu)化方法有多種,包括陽極位置優(yōu)化,多級 TSV 填充,電鍍電流密度優(yōu)化[22]。

最后,使用 CMP 來去除晶片表面的銅覆蓋層和阻擋層。總的來說,這項技術(shù)需要兩個步驟。第一步是去除通孔填充后的厚的銅凹坑或凹槽,到阻擋層停止。第二步是去除阻擋層,到絕緣層停止。選擇不同的漿料來實(shí)現(xiàn)隔離,避免凹陷和侵蝕[23]。

3.5 TSV銅暴露

另一個關(guān)鍵步驟是由于銅材料和硅襯底之間熱膨脹系數(shù)不匹配[24,25]帶來的 TSV 擠壓或 TSV 凸點(diǎn)問題。銅的熱膨脹系數(shù)為 17.6 ppm/℃,高于硅的 2.6 ppm/℃,引起電介質(zhì)層開裂和分層等可靠性問題。通過對一系列不同條件下退火工藝的實(shí)驗,得出了退火工藝的影響。Cu 從退火溫度在 350 ℃ 開始凸起,一直到 450 ℃。銅的突出現(xiàn)象,有兩種可能的機(jī)制。第一個機(jī)制是在退火過程中垂直擴(kuò)展的銅材料塑性變形。第二種機(jī)制是由于當(dāng) TSV 中應(yīng)力分布不均勻引起的擴(kuò)散蠕變[26]。通過對電鍍工藝之后的 TSV 進(jìn)行適當(dāng)?shù)念A(yù)退火處理來減少硅應(yīng)力是很有必要的,然后,用 CMP 去除多余銅。

4 結(jié)語

本文綜述了三維集成中各種 TSV 制造技術(shù),包括工藝的發(fā)展,銅的填充方法的各種應(yīng)用,和電介質(zhì)層,阻擋層,銅種子層的應(yīng)用克服了硅側(cè)壁粗糙,利用高縱橫比的 TSV 的濕法工藝解決了銅種子的不連續(xù)性問題。TSV 的銅填充有三種電鍍方法:共形電鍍、用于無縫填充的自下而上的密封凸點(diǎn)填充、用于轉(zhuǎn)接板和設(shè)備應(yīng)用的超共形電鍍。此外,還介紹了 TSV 的空隙也可能導(dǎo)致電氣故障和可靠性問題,和它的根本原因。同時,也對用于三維集成的 TSV 關(guān)鍵技術(shù)作出了展望,擁有著小外形、高密度、低成本諸多優(yōu)勢的它具有非常廣闊的應(yīng)用前景。

-

TSV

+關(guān)注

關(guān)注

4文章

117瀏覽量

81740 -

硅通孔

+關(guān)注

關(guān)注

2文章

24瀏覽量

11921 -

刻蝕

+關(guān)注

關(guān)注

2文章

195瀏覽量

13250

原文標(biāo)題:三維集成中的 TSV 技術(shù)

文章出處:【微信號:appic-cn,微信公眾號:集成電路應(yīng)用雜志】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

TSV工藝流程與電學(xué)特性研究

評論