allegro pcb editor規(guī)則設(shè)置類別優(yōu)先順序

- pcb(383717)

- PCB設(shè)計(82997)

- allegro(143955)

- 可制造性設(shè)計(15288)

- 華秋DFM(3866)

相關(guān)推薦

Allegro中如何進(jìn)行顏色設(shè)置

Allegro中如何進(jìn)行顏色設(shè)置

在ALLEGRO中,如何對網(wǎng)絡(luò)設(shè)置顏色?比如對POWER網(wǎng)絡(luò),我想讓它顯示為紅顏色!怎么做?RichardLC網(wǎng)友回復(fù):我想你

2008-03-22 16:40:44 11362

11362

11362

11362

Allegro布線規(guī)則的設(shè)置

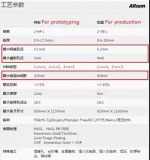

PCB布線經(jīng)常會要求對重要的信號線進(jìn)行規(guī)則的設(shè)置。布線規(guī)則的設(shè)置通常包括線寬和線距兩大部分。下面就以一主板Layout guide

2010-06-21 08:48:22 10808

10808

10808

10808

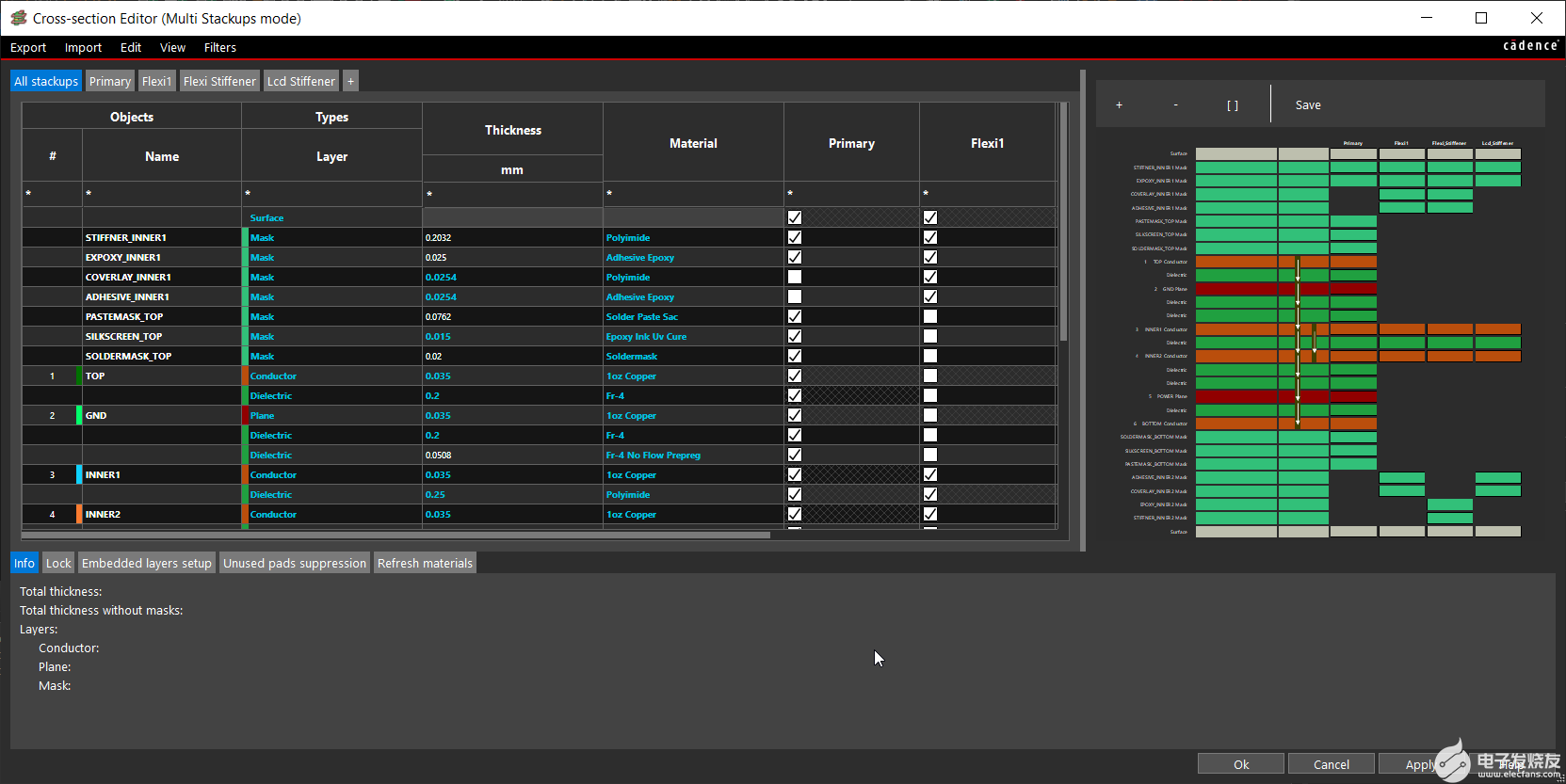

Allegro PCB設(shè)計技巧 為多層剛性和柔性堆疊指定層信息

能。 Allegro ?布局編輯器 – Allegro ? PCB Editor 和 Allegro ? Package Designer Plus – 包括基于電子表格的用戶界面、橫截面編輯器,可幫助您使用關(guān)鍵層信息定義準(zhǔn)確的層堆疊,以避免任何電子元件設(shè)計失敗。層信息包括層數(shù)和用于疊層中的層的材料,

2022-03-25 18:16:02 10792

10792

10792

10792

Allegro PCB Editor Win8.1 64位失去響應(yīng)問題

Allegro PCB Editor Win8.1 64位失去響應(yīng)問題,大家有遇到過的嗎?OrCAD可以正常使用。怎么解決,求高手指點(diǎn)。

2015-05-19 18:03:15

Allegro PCB Editor啟動失敗求助

cadence能正常打開ORCAD組件,但打開PCB Editor里面的組件就會提示如下,重裝也這樣,有人知道什么問題嗎?搞了一天了一直搞不定,不想重裝系統(tǒng)。

2019-03-26 21:45:49

Allegro PCB設(shè)計極速入門(一)

。目錄(Allegro PCB設(shè)計最精簡流程與常見問題處理辦法)一、原理圖相關(guān)處理(默認(rèn)原理圖設(shè)計完畢,進(jìn)入PCB設(shè)計環(huán)節(jié))1、添加封裝屬性(操作細(xì)節(jié))2、原理圖設(shè)計規(guī)則檢查3、導(dǎo)出網(wǎng)絡(luò)表二、PCB板邊

2016-09-12 20:14:36

Allegro PCB軟件畫板技巧總結(jié)

斷裂的鋸齒狀,很難看,讓人搞不清楚是不是連接有問題還是電腦顯卡問題。查資料與搜索一下,原理是Allegro PCB軟件可以設(shè)置與修改顯示的樣子。修改方式如下:

2019-07-08 07:55:11

Allegro怎么放置后臺元器件 PCB圖文教程

點(diǎn)擊Place-QuickPlace,按照原理圖設(shè)置好的Room進(jìn)行規(guī)則放置。1、 Allegro的快捷鍵怎么設(shè)置,有哪幾種方式?(圖文詳解見附件)

2019-08-26 14:27:57

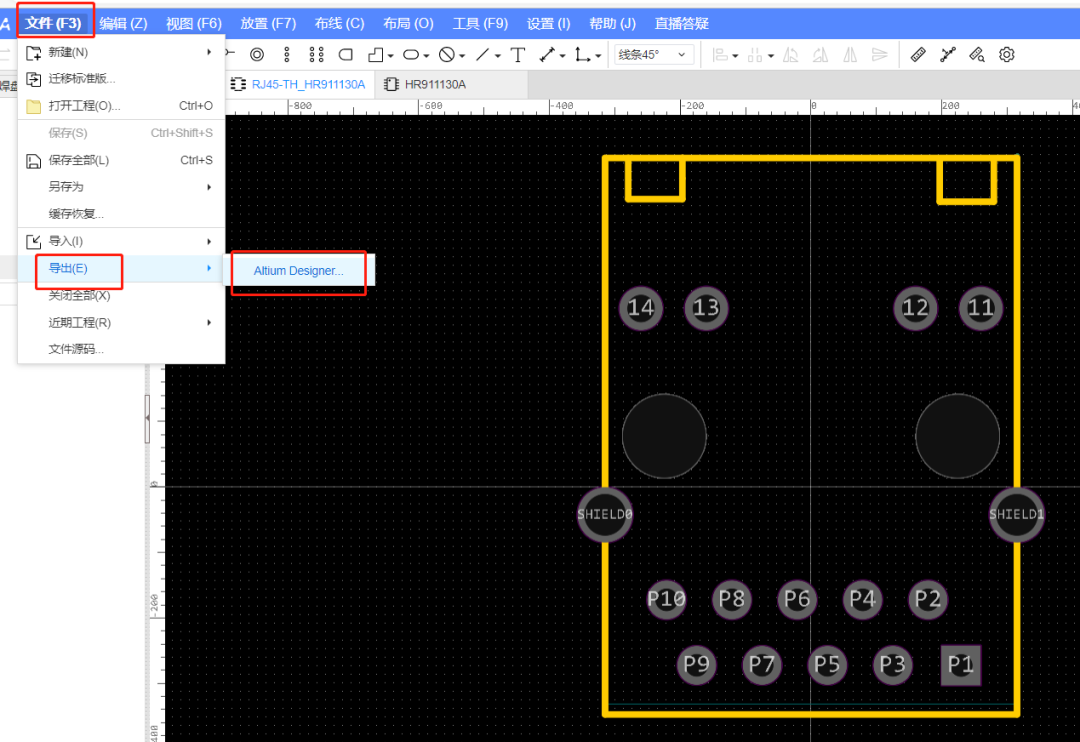

Allegro轉(zhuǎn)Altium Designer教程

從Cadence Allegro PCB Editor到Altium Designer的轉(zhuǎn)換

2019-03-29 09:14:52

PCB layout - PCB設(shè)計操作流程和注意事項(xiàng)

PCB設(shè)計操作流程和注意事項(xiàng)最后修改時間:2014-12-10本文主要描述PCB設(shè)計的流程和注意事項(xiàng)。匯總了一些小技巧和軟件設(shè)置。主要使用的軟件有:Cadence Allegro 15.5

2019-07-09 06:00:30

PCB設(shè)計規(guī)則

請問PCB設(shè)計規(guī)則怎樣設(shè)置?怎樣設(shè)置PCB的電氣規(guī)則檢查?比如說線寬,焊盤間的距離,線與線之間的間距,焊盤與線之間的間距怎樣定義設(shè)置?

2016-08-13 16:57:56

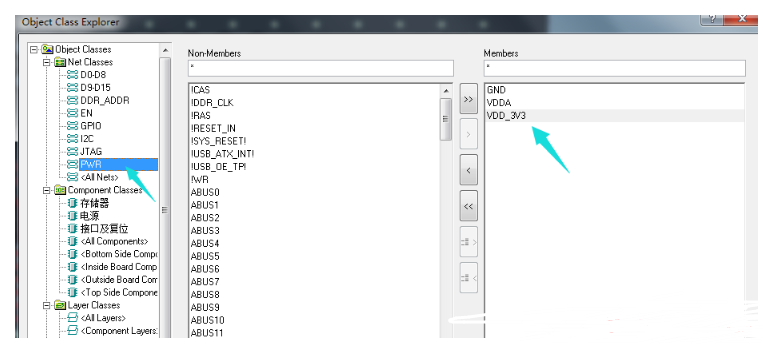

PCB設(shè)計軟件allegro16.6演示區(qū)域規(guī)則的設(shè)置

前一期對物理規(guī)則和間距規(guī)則進(jìn)行了設(shè)置,本期板兒妹繼續(xù)給大家介紹區(qū)域約束規(guī)則設(shè)置。用PCB設(shè)計工具進(jìn)行畫板,對于不同的走線,線寬與線距要求是不同的,比如電源走線、時鐘走線、差分走線等,但是這些走線

2016-12-28 10:45:56

PCB設(shè)計軟件藍(lán)牙音箱實(shí)操│網(wǎng)表導(dǎo)出導(dǎo)入和封裝路徑設(shè)置

`PCB設(shè)計軟件allegro藍(lán)牙音箱案例實(shí)操講解,以藍(lán)牙音箱為案例將PCB設(shè)計基礎(chǔ)知識融進(jìn)實(shí)際案例中,通過操作過程講解PCB設(shè)計軟件功能及實(shí)用經(jīng)驗(yàn)技巧,全文著重講解網(wǎng)表導(dǎo)出導(dǎo)入和封裝路徑設(shè)置

2018-07-31 14:15:07

allegro中等長設(shè)置總結(jié)

個人小結(jié),希望能對那些還不會用allegro設(shè)置等長規(guī)則的朋友有點(diǎn)作用。也歡迎同行交流。

2013-12-26 15:53:24

allegro格點(diǎn)設(shè)置詳解

allegro 格點(diǎn)設(shè)置,格點(diǎn)設(shè)置詳解by---博勵pcb培訓(xùn)在PCB設(shè)計過程中,合理的設(shè)置格點(diǎn)對PCB設(shè)計有很大幫助。根據(jù)不同設(shè)計階段,可選擇不同的格點(diǎn)。首先,我們討論布局階段。在布局階段,我們

2019-02-13 23:31:26

AD17軟件設(shè)置了線寬規(guī)則,為啥走線沒有按照設(shè)置的規(guī)則走線?

我們有很多的朋友在設(shè)置了規(guī)則后,可規(guī)則偏偏沒有起到作用,這主要是應(yīng)為規(guī)則設(shè)置錯誤、優(yōu)先級錯誤和規(guī)則未使能造成的。a、 優(yōu)先級:優(yōu)先級搞錯,這是大家經(jīng)常會犯得錯,所以一定要注意。比如圖三中我在這設(shè)置了

2018-11-19 10:52:08

Altium Designer PCB與Allegro PCB相互轉(zhuǎn)換

Allegro PCB轉(zhuǎn)Allegro PCB:(1)把Altium Designer PCB轉(zhuǎn)換成PADS PCB,并且導(dǎo)出5.0版本的ASC文件。(2)然后打開Allegor Designer

2019-11-21 14:12:49

Cadence 17.4支持約束規(guī)則的雙向設(shè)置及同步

問題,在17.4的版本,OrCADCapture直接可以調(diào)用Constraintmanager約束管理,在電路設(shè)計的過程中就可以直接進(jìn)行約束規(guī)則的設(shè)置,直接將設(shè)置號的規(guī)則同步到Allegro PCB文件里面

2020-07-06 15:00:43

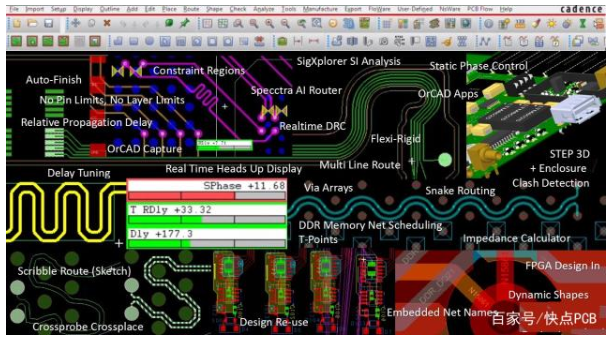

Cadence Allegro與OrCAD PCB軟件全新功能與特性

Cadence 宣布推出其最新版Cadence? Allegro? 與 OrCAD?印刷電路(PCB) 軟件,它擁有的全新功能與特性能夠提高PCB工程師的績效與效率。Allegro與OrCAD

2018-09-10 16:37:20

Cadence如何設(shè)置焊盤的路徑

`在 allegro pcb editor 中設(shè)置路徑 ,path 中 library 無法設(shè)置,如下圖所示:請教各位大俠。`

2017-08-14 17:06:39

PADS畫PCB時規(guī)則如何設(shè)置優(yōu)先級?

我想使走線穿過一個元件的兩個pad之間,但規(guī)則設(shè)置trace和pad之間間距6mil,我就將這個封裝的Decal Rules設(shè)置成Trace和Pad,SMD都為0,如上圖所示,但是依然報錯。請問是哪里出了問題?不要說將Default里的間距改成0,這我知道。

2023-04-13 16:22:46

Pads文件轉(zhuǎn)換Allegro PCB后封裝如何按PAD大小規(guī)則的重命名

Pads文件轉(zhuǎn)換Allegro PCB后封裝如何按PAD大小規(guī)則的重命名,避免設(shè)計出錯。 封裝PAD名字規(guī)則重命名 1、導(dǎo)出整板PCB封裝到一個新的lib文件路徑 2、任意打開一個封裝,可以看出PAD

2023-03-31 15:19:17

cadence 的PCB editor 設(shè)置

cadence 的PCB editor每次打開都自動顯示上次的pcb 封裝文件,怎么關(guān)閉?。還有就是setup的圖紙大小數(shù)字有時不能改,怎么解決呢

2012-10-19 21:06:19

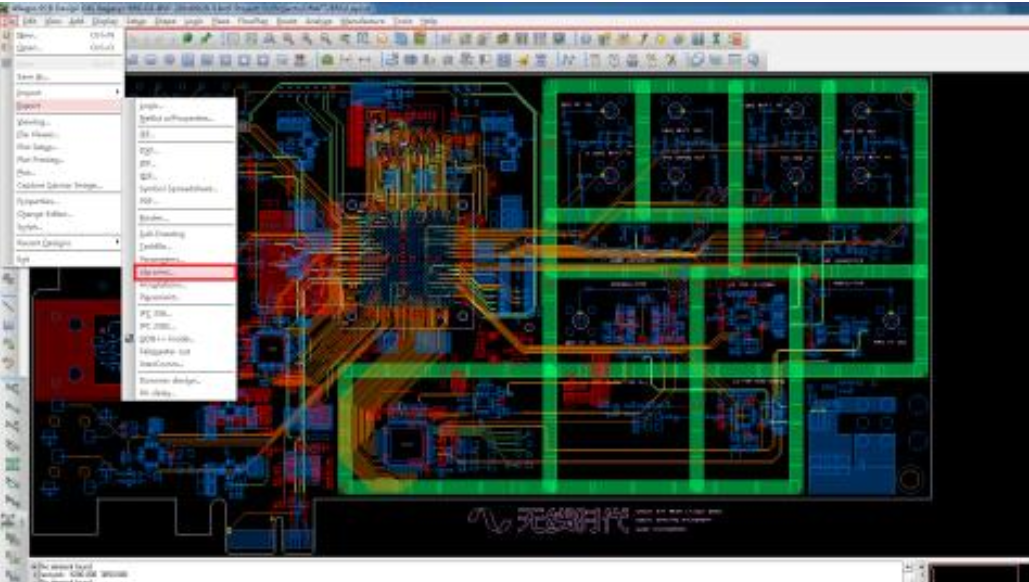

portel的PCB文件可以如何導(dǎo)入allegro

portel的PCB文件可以如何導(dǎo)入allegro[hide]1.我所用軟件ad6.8(altium desigener6.8) 和spb16.02.在ad6.8里打開一個PCB圖后點(diǎn)文件- 另存為

2010-03-18 14:43:50

【Altium小課專題 第142篇】Altium Designer PCB如何轉(zhuǎn)換成Allegro PCB?

(1)把Altium Designer PCB轉(zhuǎn)換成PADS PCB,并且導(dǎo)出5.0版本的ASC文件。(2)打開Allegro PCB Editor,執(zhí)行菜單命令“Import-CAD

2021-08-06 09:51:39

不能差分布線

新人,第一次用allegro,在pcb editor里布線,設(shè)置了差分對規(guī)則,返回布線的時候,選中差分對其中的一個引腳布線,但是只拉出來了一根線,右鍵里也沒有單根走線模式可選。求解。。。。。。

2015-04-15 17:38:54

中斷優(yōu)先級的基本規(guī)則

單片機(jī)芯 片: STC12C5A60S2 晶振是11.0592MHZ中斷優(yōu)先級的基本規(guī)則1.低優(yōu)先級中斷可被高優(yōu)先級中斷所中斷2.任何中斷都不被同級中斷所中斷然而datashhet里

2021-11-25 06:32:12

關(guān)于PCB EDITOR 中導(dǎo)入DXF文件的問題

,保存文件,文件類型選擇“...R12/R14...(DXF)”這種類型;3:在PCB EDITOR中導(dǎo)入步驟2中的DXF文件,設(shè)置好后導(dǎo)入,但導(dǎo)入后只有"BOARD

2013-04-28 07:14:51

分享:Cadence OrCAD and Allegro 17.20.015 Hotfix

is enabled.1620210 ALLEGRO_EDITOR UI_GENERAL Need to run PCB Editor from both 17.2-2016 and 16.6

2017-03-28 08:43:23

分享:Cadence OrCAD and Allegro 17.20.020 Hotfix

Allegro PCB Designer in 17.2 S0161742084 ALLEGRO_EDITOR DATABASE Running DB Doctor on DRA files

2017-06-13 10:54:30

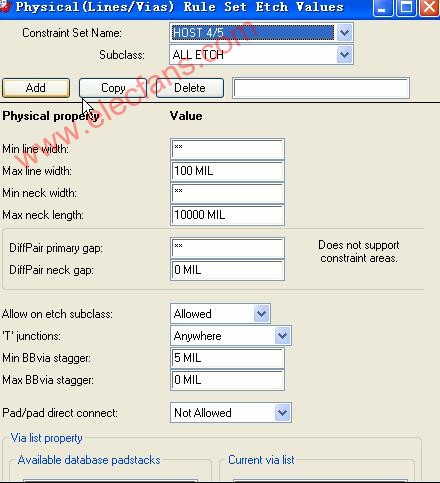

原創(chuàng)|高速PCB設(shè)計軟件allegro中與網(wǎng)絡(luò)有關(guān)的約束規(guī)則設(shè)置

在allegro pcb的設(shè)計過程中,設(shè)計約束規(guī)則包括時序規(guī)則、間距規(guī)則、信號完整性規(guī)則以及物理規(guī)則等,本期主要詳細(xì)講解與物理、間距與電氣約束中的線寬、線間距物理規(guī)則的設(shè)置。一、線寬設(shè)置(1)設(shè)置

2016-12-23 17:08:25

高速PCB設(shè)計系列基礎(chǔ)知識43 | 差分信號的規(guī)則設(shè)置

本節(jié)繼續(xù)講解PCB設(shè)計中差分信號的規(guī)則設(shè)置。差分信號的規(guī)則可以在電氣規(guī)則下面建立,也可以在物理規(guī)則下面建立;電氣規(guī)則下建立的差分信號規(guī)則是全局性的,不受區(qū)域規(guī)則的約束,在BGA等需要密集出線的地方

2017-08-15 10:27:49

高速PCB設(shè)計軟件allegro16.6演示差分規(guī)則的設(shè)置

上一期我們介紹了高速PCB設(shè)計軟件allegro16.6差分信號的設(shè)定在高速PCB布線前需要對差分信號的規(guī)則進(jìn)行設(shè)置因此本期重點(diǎn)介紹在電氣規(guī)則和物理規(guī)則下是如何建立差分信號的規(guī)則1、在電氣規(guī)則下建立

2017-01-06 09:46:41

ALLEGRO PCB ROUTER L, XL

ALLEGRO PCB ROUTER L, XLThe Cadence Allegro PCB Router routing environment is the leading solution

2008-10-16 09:42:52 0

0

0

0Allegro PCB SI L XL /ALLEGRO P

ALLEGRO PCB SI L, XLALLEGRO PCB PI OPTION XLCadence Allegro PCB SI offers an integrated high-speed

2008-10-16 09:45:20 0

0

0

0ALLEGRO PCB LIBRARIAN 610

ALLEGRO PCB LIBRARIAN 610AUTOMATED LIBRARY PART CREATION AND VALIDATIONCadence Allegro PCB

2008-10-16 09:55:40 0

0

0

0ALLEGRO PCB ROUTER

ALLEGRO PCB ROUTER今天領(lǐng)先的互連布線解決方案

Cadence Allegro印制電路板布線器,作為Allegro系統(tǒng)互連設(shè)計平臺的一個部分,是市場上領(lǐng)先的用于自動或者交互式互連布線的

2010-06-09 15:03:56 0

0

0

0Allegro PCB設(shè)計流程一

Allegro PCB設(shè)計流程一

Allegro PCB SI 的設(shè)計流程包括如下六個步驟:

Pre-Placement

&nbs

2009-11-18 10:17:00 2580

2580

2580

2580電腦啟動順序設(shè)置

電腦啟動順序設(shè)置

最后,我們來設(shè)置系統(tǒng)的啟動順序,這是一個很重要的內(nèi)容,尤其是對新安裝的電腦。選擇主菜單的這一項(xiàng),讓我們看一下設(shè)置

2010-01-14 09:48:44 5994

5994

5994

5994allegro規(guī)則設(shè)置里常見縮寫的含義

allegro規(guī)則設(shè)置里常見縮寫詞的含義,Dsn Design整個設(shè)計

2011-11-22 10:51:53 5136

5136

5136

5136學(xué)習(xí)allegro從了解如何建焊盤開始

學(xué)習(xí)allegro從了解如何建焊盤開始,啟動焊盤設(shè)計器,執(zhí)行開始/程序/Cadence psd 16.2/Allegro Utilities/Padstack Editor, 啟動焊盤設(shè)計器,

2011-11-22 11:04:35 3550

3550

3550

3550Allegro16.3常用的四大模塊

Allegro 包括供設(shè)計輸入的Orcad Capturer ,供數(shù)字與混合訊號模擬用的 PSpiceR A/D Basics,供PCB設(shè)計的 pcb editor 以及供高密度PCB電路板自動繞線的pcb editor

2011-11-23 13:51:42 3868

3868

3868

3868Allegro中尺寸標(biāo)注文字的設(shè)置

本內(nèi)容介紹了Allegro中尺寸標(biāo)注文字的設(shè)置,這里我們介紹文字參數(shù)的設(shè)置。

2012-06-26 15:03:51 6046

6046

6046

6046

Allegro中尺寸標(biāo)注參數(shù)的設(shè)置

Allegro中尺寸標(biāo)注有很強(qiáng)大的功能,包括線性標(biāo)注,角度標(biāo)注,引線標(biāo)注等。下面介紹一下Allegro中尺寸標(biāo)注參數(shù)的設(shè)置

2012-06-26 15:09:10 17869

17869

17869

17869

Allegro16.6約束規(guī)則設(shè)置詳解(圖文并茂)

詳細(xì)介紹了ALLEGRO16.6 約束規(guī)則設(shè)置方法,適合初學(xué)者

2015-11-20 15:45:08 0

0

0

0AD PCB封裝轉(zhuǎn)Allegro封裝或者AD PCB轉(zhuǎn)Allegro PCB

AD封裝轉(zhuǎn)ALLEGRO封裝時,要把所有封裝放到一張PCB上或者分批次的放到PCB上,把PCB轉(zhuǎn)成ALLEGRO格式的,然后再用ALLEGRO導(dǎo)出PCB封裝

2018-04-05 17:06:00 47055

47055

47055

47055

DSP中斷如何設(shè)置優(yōu)先級

原以為2812中斷不能設(shè)置優(yōu)先級。實(shí)際上硬件上優(yōu)先級是做好的。但軟件上有辦法來設(shè)置優(yōu)先級。

2018-04-08 17:20:48 19

19

19

19ALLEGRO 焊盤設(shè)計器菜單流程

執(zhí)行開始/程序/Cadence spb 16.5/Allegro Utilities/Padstack Editor, 啟動焊盤設(shè)計器, 焊盤設(shè)計器。

2018-05-10 17:16:00 1622

1622

1622

1622

Allegro PCB設(shè)計時等長設(shè)置的一些方法與技巧解析

本文檔的主要內(nèi)容詳細(xì)介紹的是Allegro PCB設(shè)計時等長設(shè)置的一些方法與技巧解析。以DDR3(4pcs,fly-by 結(jié)構(gòu))為例,講述一下在allegro 中如何添加電氣約束(時序等長)。

2018-11-27 16:02:57 0

0

0

0PCB設(shè)計的規(guī)則流程及注意事項(xiàng)介紹

PCB設(shè)計規(guī)則、層定義、過孔設(shè)置、CAM輸出設(shè)置已經(jīng)作成缺省啟動文件,名稱為Default.stp,網(wǎng)表輸入進(jìn)來以后,按照設(shè)計的實(shí)際情況,把電源網(wǎng)絡(luò)和地分配給電源層和地層,并設(shè)置其它高級規(guī)則。在所

2019-04-30 12:00:00 5326

5326

5326

5326PCB設(shè)計之Allegro軟件問題

Allegro是Cadence推出的先進(jìn) PCB 設(shè)計布線工具,也是目前最高端、最主流的PCB軟件代表之一,華為、中興這類大型公司使用的也是Allegro。

2019-10-11 16:40:38 8617

8617

8617

8617

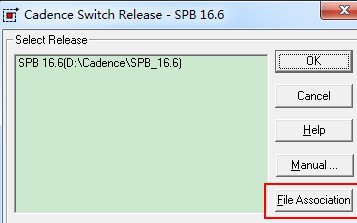

allegro設(shè)置SCH和pcb文件的默認(rèn)打開方式方法

設(shè)計好的SCH和pcb文件我都需要先打開軟件,通過軟件才能打開工程文件,allegro 不能設(shè)置成默認(rèn)打開方式

2019-10-13 09:27:00 18227

18227

18227

18227

PCB設(shè)計之電氣(Electrical)規(guī)則設(shè)置

電氣(Electrical)規(guī)則設(shè)置是設(shè)置電路板在布線時必須遵守的規(guī)則,包括安全距離、開路、短路方面的設(shè)置。這幾個參數(shù)的設(shè)置會影響所設(shè)計PCB的生產(chǎn)成本、設(shè)計難度及設(shè)計的準(zhǔn)確性,應(yīng)嚴(yán)謹(jǐn)對待。

2020-10-09 11:39:41 13532

13532

13532

13532

PCB設(shè)計的線寬線距與孔徑規(guī)則設(shè)置注意事項(xiàng)

這些不同的需求都可以在規(guī)則里定義不同網(wǎng)絡(luò)不同的線寬值,然后根據(jù)重要程度設(shè)置規(guī)則應(yīng)用優(yōu)先級。同樣,對于線距來說,在規(guī)則頁面Design - Rules - Electrical - Clearance 里定義不同網(wǎng)絡(luò)之間的電氣安全間距,當(dāng)然也包括線距。

2020-09-21 15:16:58 6513

6513

6513

6513

如何設(shè)置HDI PCB布局

HDI PCB布局可能非常局促,但是正確的設(shè)計規(guī)則集將幫助您成功設(shè)計。 更高級的PCB將更多的功能包裝在更小的空間中,通常使用定制的IC / SoC,更高的層數(shù)和更小的跡線。要正確設(shè)置這些設(shè)計的布局

2020-12-18 13:14:56 2346

2346

2346

2346pcb設(shè)計如何設(shè)置多個網(wǎng)絡(luò)的規(guī)則

執(zhí)行菜單命令Design→Rules(快捷鍵DR),進(jìn)入規(guī)則設(shè)置欄;新建個線寬規(guī)則,在規(guī)則設(shè)置欄選擇“ net class”,選擇對應(yīng)的class

2020-10-20 10:32:08 5379

5379

5379

5379

orcad產(chǎn)生Cadence Allegro的網(wǎng)表操作步驟

第一方網(wǎng)表參數(shù)設(shè)置示意圖 第三步,輸入Allegro第一方網(wǎng)表需要注意下面幾個地方: 1)?需要勾選Creat PCB Editor Netlist,才會生成網(wǎng)表; 2)?下面的Netlist Files是輸出網(wǎng)

2021-11-16 14:50:03 10184

10184

10184

10184

cortex M內(nèi)核優(yōu)先級設(shè)置

Cortex M內(nèi)核中每個中斷都有一個8位的優(yōu)先級設(shè)置寄存器這個8位的寄存器可以分為搶占優(yōu)先級和子優(yōu)先級兩個部分(通過設(shè)置優(yōu)先級組設(shè)置)搶占優(yōu)先級和子優(yōu)先級有什么用?舉例說明:有兩個中斷A、BA

2021-12-01 11:51:05 4

4

4

4Cadence Allegro的快捷鍵設(shè)置

Cadence Allegro是一款功能比較強(qiáng)大的軟件,相比較其他的PCB設(shè)計軟件來說,界面交互比較友好。其中的快捷鍵設(shè)置就是比較強(qiáng)大,我見過朋友完全使用快捷鍵進(jìn)行畫圖的。

2022-09-20 09:37:06 17087

17087

17087

17087PCB布局布線的規(guī)則

你知道什么是PCB嗎?那你知道什么是PCB布局布線規(guī)則嗎?一、元器件布局的10條規(guī)則:遵照“先大后小,先難后易”的布置原則,即重要的單元電路、核心元器件應(yīng)當(dāng)優(yōu)先布局。

2022-10-28 10:03:33 2352

2352

2352

2352Cadence Allegro在PCB中手動或者自動添加差分對屬性

Cadence Allegro在PCB中手動或者自動添加差分對屬性 設(shè)計PCB過程中,若設(shè)計中有差分對信號,則需要將是差分的2個信號設(shè)置為差分對,設(shè)置差分對有2種方式:手動添加及自動添加 一、手動

2022-12-16 08:00:07 1077

1077

1077

1077Cadence Allegro PCB多根走線及其間距設(shè)置

Cadence Allegro PCB多根走線及其間距設(shè)置 在進(jìn)行PCB布線的時候,當(dāng)遇到一把一把的總線的時候,如果是一根一根線的去走,是很費(fèi)時間的,所以呢,這里講解一下,在Allegro

2022-12-24 11:30:05 3417

3417

3417

3417Cadence Allegro PCB過孔添加與設(shè)置

Cadence Allegro PCB過孔添加與設(shè)置 在進(jìn)行PCB設(shè)計時,都必須使用到過孔,對走線進(jìn)行換層處理。在走線進(jìn)行打過孔之前,必須先要添加過孔,這樣在PCB布線時才可以使用過孔,具體操作

2023-04-12 07:40:06 16719

16719

16719

16719嘉立創(chuàng)EDA專業(yè)版網(wǎng)絡(luò)規(guī)則設(shè)置

在“設(shè)計規(guī)則”中的“規(guī)則管理”界面將PCB的各個設(shè)計規(guī)則如線寬規(guī)則、差分規(guī)則、過孔規(guī)則等設(shè)置完成之后,就需要將PCB中每個網(wǎng)絡(luò)所對應(yīng)的規(guī)則進(jìn)行驅(qū)動,那么就可以設(shè)置“網(wǎng)絡(luò)規(guī)則”。在“網(wǎng)絡(luò)規(guī)則”中可以對當(dāng)前PCB內(nèi)的所有網(wǎng)絡(luò)進(jìn)行規(guī)則分配,繼而讓對應(yīng)網(wǎng)絡(luò)遵守其設(shè)置的規(guī)則。

2023-05-29 17:21:19 1452

1452

1452

1452

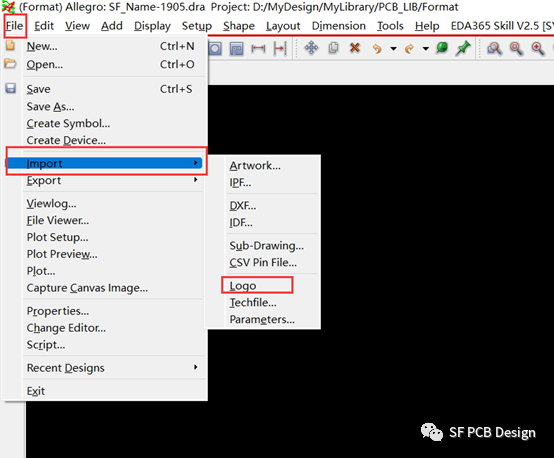

使用Allegro PCB Editor制作Logo封裝

在設(shè)計電路板時,一個漂亮的Logo絲印往往會給電路板增色不少(雖然對電路板的性能并沒有實(shí)質(zhì)性的影響)。對于Allegro PCB Editor,網(wǎng)上有一些教程12,給出了制作Logo的方法,但是

2023-06-21 15:33:06 2190

2190

2190

2190

pcb規(guī)則設(shè)置主要有哪些

分類的創(chuàng)建和差分規(guī)則設(shè)置:PCB上存在一對USB差分線,首先需要創(chuàng)建差分類,然后針對這對差分線來設(shè)置差分規(guī)則。

2023-08-01 10:06:21 2296

2296

2296

2296

pcb走線的規(guī)則設(shè)置方法

pcb板的厚度是規(guī)則設(shè)置中的一個重要參數(shù)。通常情況下,pcb板的厚度是0.8-3.2mm,厚度的選擇取決于電路的復(fù)雜性和應(yīng)用環(huán)境。在選擇pcb板厚度時,必須考慮到板層的內(nèi)部金屬層和銅線的直徑,以確保有效的接地和穩(wěn)定的耦合。

2023-08-26 12:07:22 1731

1731

1731

1731ad覆銅規(guī)則怎么設(shè)置距離

AD覆銅規(guī)則是指在PCB板上通過化學(xué)方法將銅層覆蓋在絕緣層上,用于實(shí)現(xiàn)電路連接和信號傳輸。距離是指AD覆銅之間的間距,通常也稱為覆銅間距。合理的AD覆銅規(guī)則設(shè)置能夠保證電路的正常工作和可靠性,同時

2023-12-20 10:46:29 945

945

945

945pcb走線的規(guī)則設(shè)置方法介紹

隨著電子產(chǎn)品的迅速發(fā)展,PCB(Printed Circuit Board)在電子設(shè)計中扮演著重要的角色。設(shè)計PCB走線時,合理設(shè)置規(guī)則是確保電路在安全、穩(wěn)定、高效工作的基礎(chǔ)。本文將詳細(xì)介紹PCB

2024-01-09 10:45:15 430

430

430

430 電子發(fā)燒友App

電子發(fā)燒友App

評論