AD版本要用AD6.9的,AD9不行,另存時(shí)會(huì)有錯(cuò)誤,步驟如下:

工程師的巨大福利,首款P_C_B分析軟件,點(diǎn)擊免費(fèi)領(lǐng)取

1.直接建一個(gè)只有原理圖的項(xiàng)目。

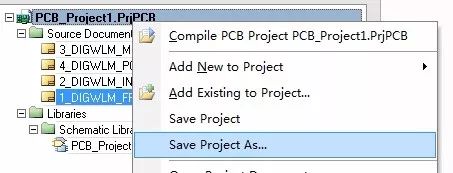

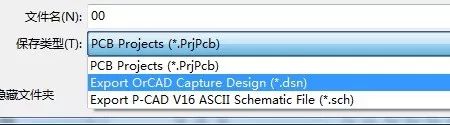

2.另存為OrCAD (.dsn)項(xiàng)目。如下圖:

另存

選擇OrCAD格式

3.用Capture 打開保存的DSN文件即可。打開時(shí)會(huì)等一會(huì),原理圖尺寸大的會(huì)等的久一點(diǎn)。

4.注意點(diǎn):原理圖尺寸不能太大張,原理圖尺寸在A3或A3以下轉(zhuǎn)出來(lái)比較好,太大張會(huì)出現(xiàn)器件丟失的現(xiàn)象。小尺寸會(huì)也會(huì)出現(xiàn)小問(wèn)題,如,器件錯(cuò)位,一般是電阻電容類會(huì)有錯(cuò)位。我估計(jì)是AD原理圖用的同一類器件時(shí)引用的庫(kù)不一樣引起的。

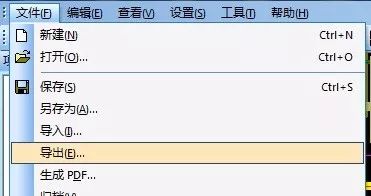

二.AD原理圖庫(kù)轉(zhuǎn)OrCAD原理圖庫(kù)

步驟如下:

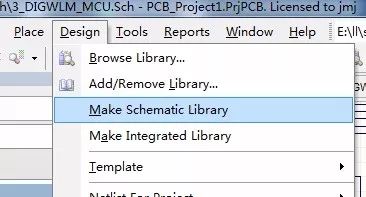

1.先在AD原理圖導(dǎo)出AD 的原理圖庫(kù),如果本來(lái)就有原理圖庫(kù)可以不用導(dǎo)出。

打開有原理圖的工程,菜單命令:Design => Make Schematic Library

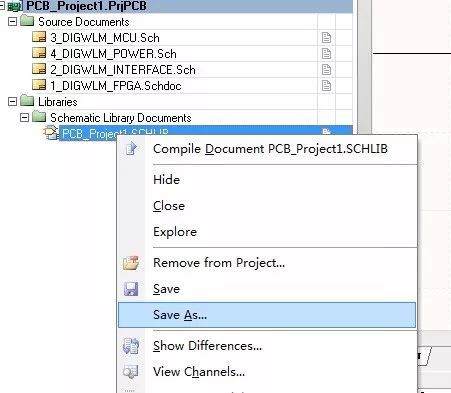

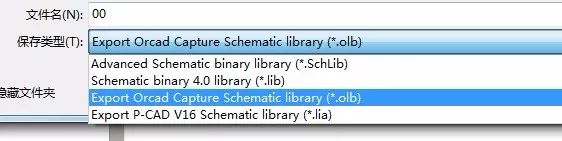

2.另存為OrCAD 格式的庫(kù)文件

另存

選擇OrCAD格式庫(kù)文件

3.另存后直接用Capture打開即可

4.注意:AD原理圖庫(kù)轉(zhuǎn)OrCAD原理圖庫(kù)時(shí),AD版本沒(méi)有要求,我試了AD6.9和AD9都可以。

三.AD PCB封裝轉(zhuǎn)Allegro封裝或者AD PCB轉(zhuǎn)Allegro PCB.

AD封裝轉(zhuǎn)ALLEGRO封裝時(shí),要把所有封裝放到一張PCB上或者分批次的放到PCB上,把PCB轉(zhuǎn)成ALLEGRO格式的,然后再用ALLEGRO導(dǎo)出PCB封裝

步驟如下:

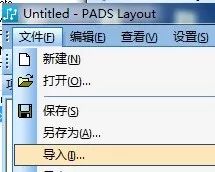

1.用PADS Layout (PADSVX.0)直接導(dǎo)入AD格式的PCB

導(dǎo)入

選擇AD格式的PCB

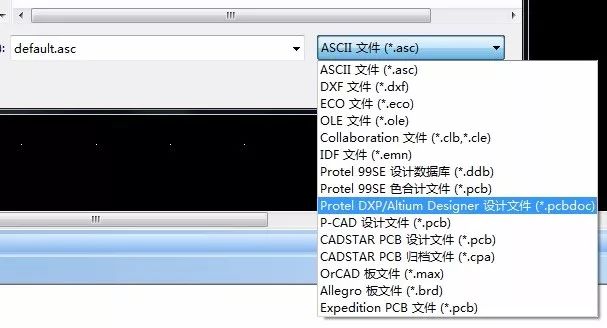

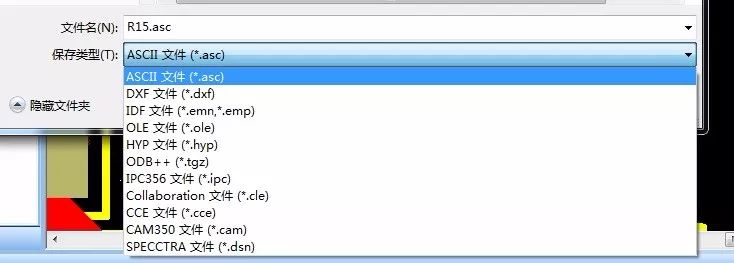

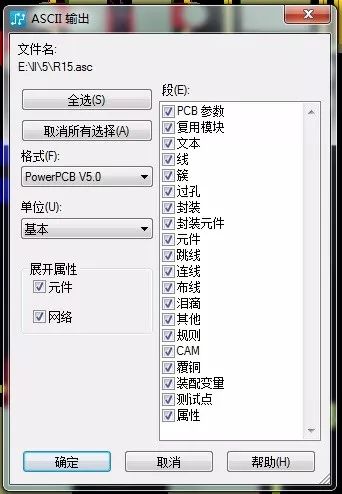

2. PADS Layout (PADSVX.0)導(dǎo)出ASCII文件(*.asc)

導(dǎo)出

選擇導(dǎo)出ASCII文件(*.asc)

ASCII選項(xiàng)如上圖,格式可選Power PCBV3.0 到V5.0,以及PADS Layout9.3以下版本都可以。

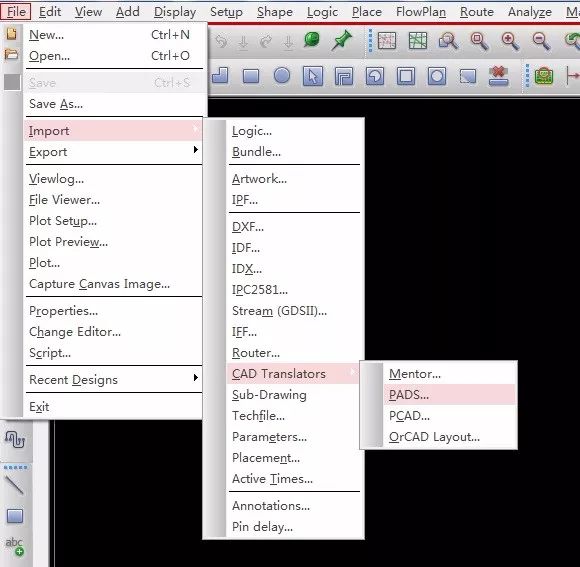

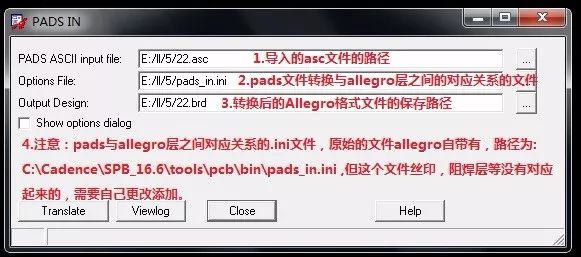

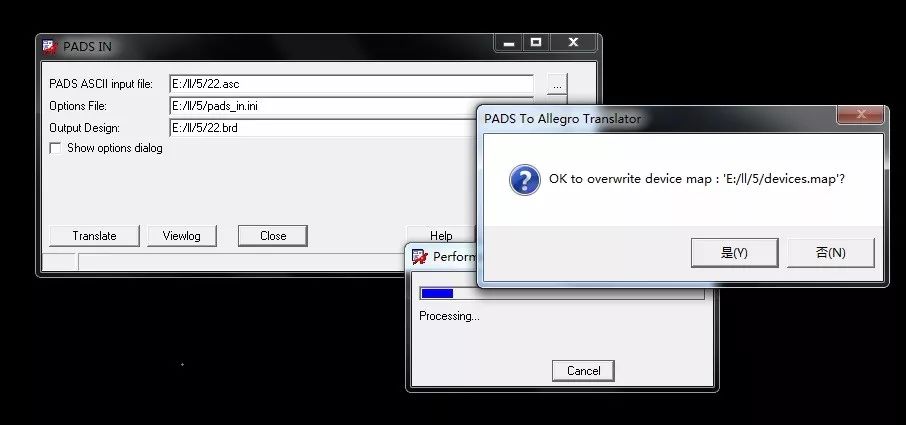

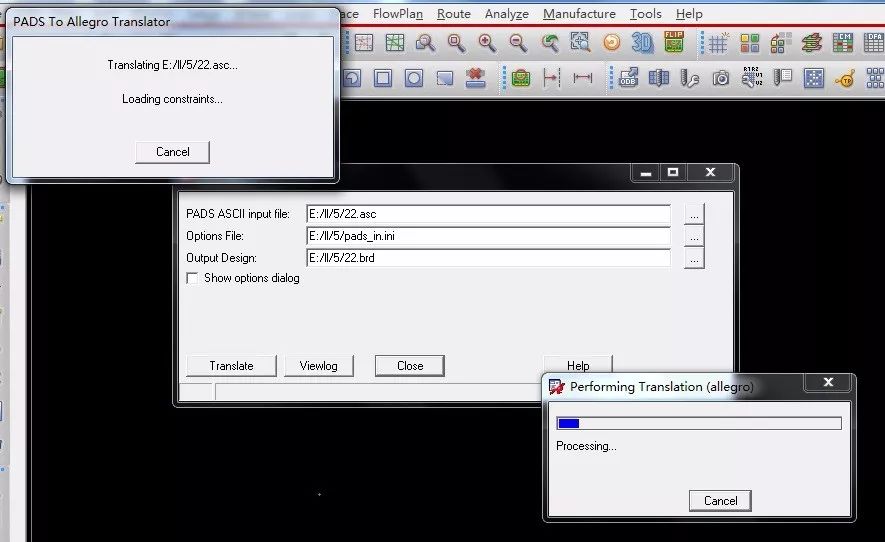

3.把ASCII文件(*.asc)導(dǎo)入到ALLEGRO,ALLEGRO 用的是V16.6版本的,其他的版本沒(méi)有試。

如下:

選擇導(dǎo)入PADS格式的文件

導(dǎo)入和轉(zhuǎn)換后輸出文件路徑選擇,以及層的配置文件選擇。

按轉(zhuǎn)換會(huì)彈出這窗口出來(lái),按“是”確認(rèn)。

左上角會(huì)有一個(gè)窗口彈出來(lái),等待讓它轉(zhuǎn)換完成。

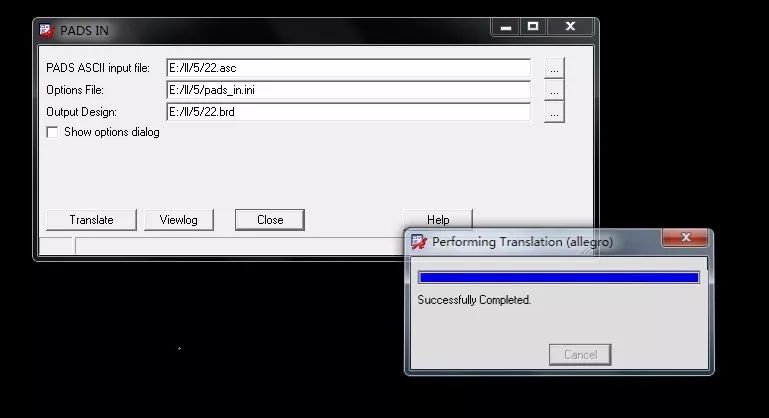

轉(zhuǎn)換完成并成功

4.用Allegro打開剛才轉(zhuǎn)換成功并保存的文件

絲印框和阻焊層都有。

5.Allegro 到處PCB封裝方法:執(zhí)行菜單命令:File => Export => Librarys

6.不足:轉(zhuǎn)換的層配置文件,層配置好后仍然有一些封裝焊盤的阻焊層和鋼網(wǎng)層沒(méi)有出來(lái)。需要手工進(jìn)行完善。

7.ini層配置文件說(shuō)明:

allegro自帶的原始文件類容如下:

[Options]

CreateSolderLayers=0

SolderOversize=0

[Line Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Copper Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Text Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Decal Map]

0=PACKAGE GEOMETRY|SILKSCREEN_TOP

1=PACKAGE GEOMETRY|SILKSCREEN_TOP

2=UNUSED|-

3=UNUSED|-

4=UNUSED|-

5=UNUSED|-

6=UNUSED|-

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Pad Map]

0=ETCH|internal_pad_def

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Via Map]

0=VIA CLASS|internal_pad_def

1=VIA CLASS|TOP

2=VIA CLASS|INTERNAL1

3=VIA CLASS|INTERNAL2

4=VIA CLASS|INTERNAL3

5=VIA CLASS|INTERNAL4

6=VIA CLASS|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

我自己更改后的層配置文件類容如下:

[Options]

CreateSolderLayers=0.0254這里我改了發(fā)現(xiàn)也沒(méi)變化

SolderOversize=0.0254這里我改了發(fā)現(xiàn)也沒(méi)變化

[Line Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Copper Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Text Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Decal Map]

0=PACKAGE GEOMETRY|SILKSCREEN_TOP

1=PACKAGE GEOMETRY|SILKSCREEN_TOP

2=UNUSED|-

3=UNUSED|-

4=UNUSED|-

5=UNUSED|-

6=UNUSED|-

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Pad Map]

0=ETCH|internal_pad_def

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=UNUSED|-

30=UNUSED|-

[Via Map]

0=VIA CLASS|internal_pad_def

1=VIA CLASS|TOP

2=VIA CLASS|INTERNAL1

3=VIA CLASS|INTERNAL2

4=VIA CLASS|INTERNAL3

5=VIA CLASS|INTERNAL4

6=VIA CLASS|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=UNUSED|-

30=UNUSED|-

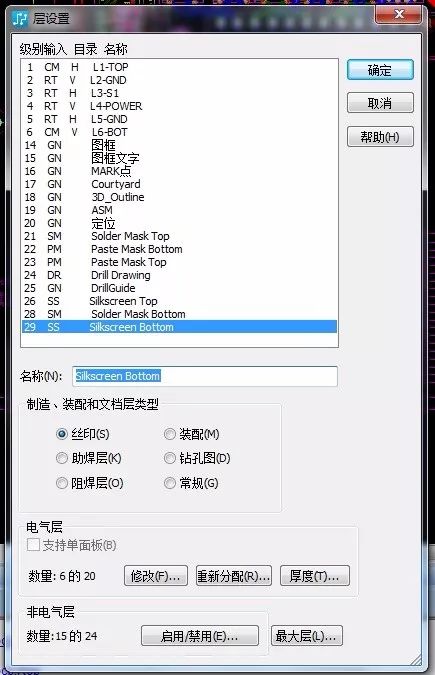

配置層的關(guān)系從哪里看出來(lái)的呢?從PADSLayout 里面的層定義可以看出來(lái),執(zhí)行如下的菜單命令:設(shè)置=》層定義,然后會(huì)彈出如下的窗口:

然后從這個(gè)層定義去看絲印或者阻焊是屬于哪一層的,比如:

Silkscreen Top是第26層;Silkscreen Bottom是在第29層,Solder Mask Top是在第21層,Solder Mask Bottom 是在第28層,然后在相應(yīng)的對(duì)象類型里面給他指定對(duì)應(yīng)關(guān)系。

比如在Pad 焊盤這中類型[Pad Map]里面加上Solder Mask Top,和 Solder MaskBottom這個(gè)兩層的對(duì)應(yīng)關(guān)系,因?yàn)楹副P這種類型原則上是沒(méi)有Silkscreen Top和Silkscreen Bottom的,所以焊盤里面可以不用加絲印的層對(duì)應(yīng)關(guān)系。然后分別在21和28改為如下的對(duì)應(yīng)關(guān)系。

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

-

pcb

+關(guān)注

關(guān)注

4319文章

23111瀏覽量

398314 -

AD

+關(guān)注

關(guān)注

27文章

868瀏覽量

150397 -

Cadence

+關(guān)注

關(guān)注

65文章

923瀏覽量

142222 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4690瀏覽量

85781 -

可制造性設(shè)計(jì)

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15607 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3494瀏覽量

4568

原文標(biāo)題:AD轉(zhuǎn)cadence詳細(xì)方法說(shuō)明【包括原理圖,原理圖庫(kù),PCB封裝庫(kù),PCB設(shè)計(jì)文件】

文章出處:【微信號(hào):pcbgood,微信公眾號(hào):奈因PCB電路板設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

PROTEL轉(zhuǎn)ALLEGRO的方法

通過(guò)Allegro軟件繪制PCB封裝的步驟說(shuō)明

allegro更新PCB封裝

ad13的pcb文件轉(zhuǎn)allegro報(bào)錯(cuò)

Altium的pcb文件轉(zhuǎn)allegro的方法

pads pcb封裝轉(zhuǎn)到allegro的方法

【Altium小課專題 第139篇】Allegro PCB如何轉(zhuǎn)換成Altium Designer PCB?

Allegro PCB SI L XL /ALLEGRO P

ALLEGRO PCB LIBRARIAN 610

ALLEGRO PCB ROUTER

簡(jiǎn)易pcb軟件allegro中手工封裝技術(shù)

PCB設(shè)計(jì)常用資料 ALLEGRO常用元件封裝庫(kù)

allegro 快速更新封裝

allegro與PADS的區(qū)別及創(chuàng)建PCB封裝的步驟

AD PCB封裝轉(zhuǎn)Allegro封裝或者AD PCB轉(zhuǎn)Allegro PCB

AD PCB封裝轉(zhuǎn)Allegro封裝或者AD PCB轉(zhuǎn)Allegro PCB

評(píng)論