引言

本系列文章共三個(gè)部分,第1部分重點(diǎn)介紹了如何準(zhǔn)確地估算某個(gè)時(shí)鐘源的抖動(dòng),并將其與ADC的孔徑抖動(dòng)組合。在本文即第2部分中,這種組合抖動(dòng)將用于計(jì)算ADC的信噪比 (SNR),之后將其與實(shí)際測(cè)量情況進(jìn)行比較。

濾波采樣時(shí)鐘測(cè)量

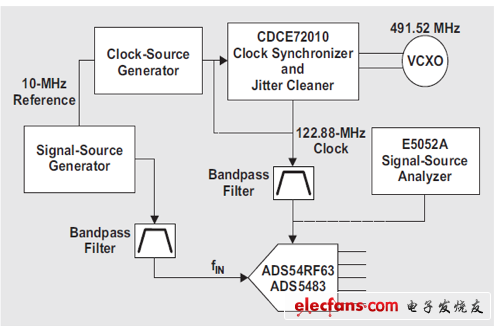

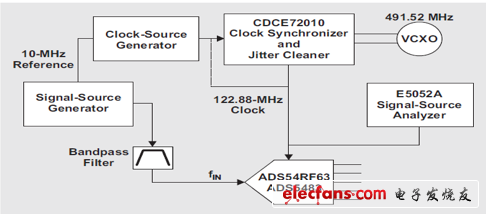

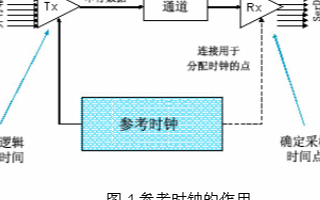

我們做了一個(gè)試驗(yàn),目的是檢查測(cè)得時(shí)鐘相位噪聲與提取自ADC測(cè)得SNR的時(shí)鐘抖動(dòng)的匹配程度。如圖11所示,一個(gè)使用Toyocom 491.52-MHz VCXO的TI CDCE72010用于產(chǎn)生122.88-MHz采樣時(shí)鐘,同時(shí)我們利用Agilent的E5052A來(lái)對(duì)濾波相位噪聲輸出進(jìn)行測(cè)量。利用一個(gè)SNR主要受限于采樣時(shí)鐘抖動(dòng)的輸入頻率對(duì)兩種不同的TI數(shù)據(jù)轉(zhuǎn)換器(ADS54RF63和ADS5483)進(jìn)行評(píng)估。快速傅里葉變換 (FFT) 的大小為131000點(diǎn)。

?

圖11 濾波后時(shí)鐘相關(guān)性測(cè)試裝置結(jié)構(gòu)

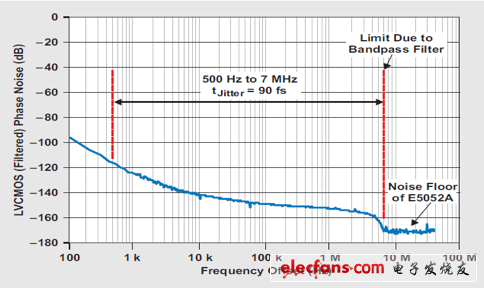

圖12所示曲線(xiàn)圖描述了濾波后CDCE72010 LVCMOS輸出的測(cè)得輸出相位噪聲。131000點(diǎn)的FFT大小將低積分帶寬設(shè)定為~500Hz。積分上限由帶通濾波器設(shè)定,其影響在相位噪聲曲線(xiàn)圖中清晰可見(jiàn)。超出曲線(xiàn)圖所示帶通濾波器限制的相位噪聲為E5052A的噪聲底限,不應(yīng)包括在抖動(dòng)計(jì)算中。濾波后相位噪聲輸出的積分帶來(lái)~90 fs的時(shí)鐘抖動(dòng)。

?

圖12 濾波后時(shí)鐘的測(cè)得相位噪聲

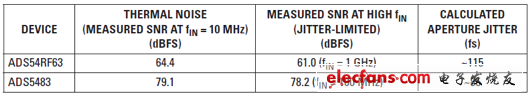

接下來(lái),我們建立起了熱噪聲基線(xiàn)。我們直接從~35 fs抖動(dòng)的時(shí)鐘源生成器使用濾波后采樣時(shí)鐘對(duì)兩種ADC采樣,而CDCE72010被繞過(guò)了。將輸入頻率設(shè)定為10MHz,預(yù)計(jì)對(duì)時(shí)鐘抖動(dòng)SNR無(wú)影響。然后,通過(guò)增加輸入頻率至SNR主要為抖動(dòng)限制的頻率,確定每個(gè)ADC的孔徑抖動(dòng)。由于采樣時(shí)鐘抖動(dòng)遠(yuǎn)低于估計(jì)ADC孔徑抖動(dòng),因此計(jì)算應(yīng)該非常準(zhǔn)確。另外還需注意,時(shí)鐘源的輸出振幅應(yīng)會(huì)增加(但沒(méi)有多到超出ADC的最大額定值),從而升高時(shí)鐘信號(hào)的轉(zhuǎn)換率,直到SNR穩(wěn)定下來(lái)為止。

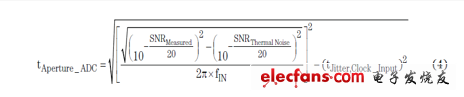

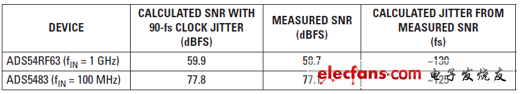

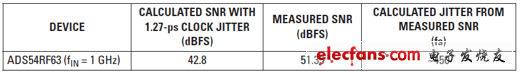

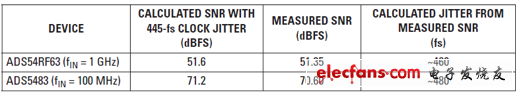

我們知道時(shí)鐘源生成器濾波后輸出的外部時(shí)鐘抖動(dòng)為~35 fs,因此我們可以利用測(cè)得的SNR結(jié)果,然后對(duì)第1部分(請(qǐng)參見(jiàn)參考文獻(xiàn)1)中的方程式1、2和3求解孔徑抖動(dòng)值,從而計(jì)算得到ADC孔徑抖動(dòng),請(qǐng)參見(jiàn)下面的方程式4。表3列舉了每種ADC測(cè)得的SNR結(jié)果以及計(jì)算得孔徑抖動(dòng)。

?

表3 測(cè)得的SNR和計(jì)算得抖動(dòng)

利用ADC孔徑抖動(dòng)和CDCE72010的采樣時(shí)鐘抖動(dòng),可以計(jì)算出ADC的SNR,并與實(shí)際測(cè)量結(jié)果對(duì)比。使用ADC孔徑抖動(dòng)可以通過(guò)測(cè)得SNR值計(jì)算出CDCE72010的采樣時(shí)鐘抖動(dòng),如表4所列。乍一看,預(yù)計(jì)SNR值有些接近測(cè)得值。但是,將兩種ADC計(jì)算得出的采樣時(shí)鐘抖動(dòng)與90fs測(cè)得值對(duì)比時(shí),出現(xiàn)另一幅不同的場(chǎng)景,其有相當(dāng)多的不匹配。

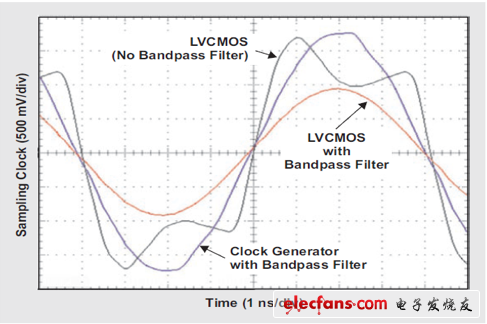

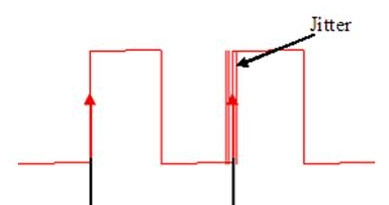

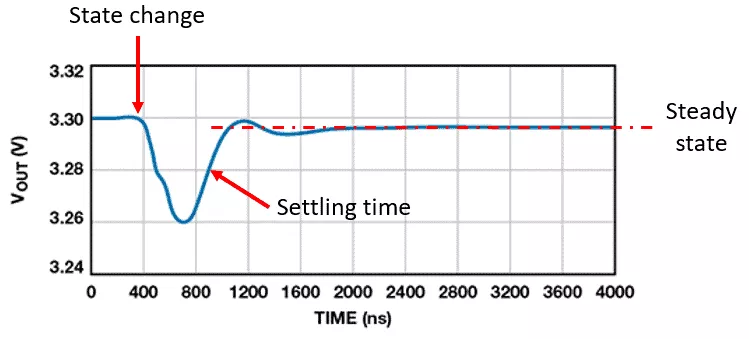

不匹配的原因是,計(jì)算得出的孔徑抖動(dòng)是基于時(shí)鐘源生成器的快速轉(zhuǎn)換速率。CDCE72010的LVCMOS輸出消除了時(shí)鐘信號(hào)的高階諧波,其有助于形成快速升降沿。圖13所示波形圖表明了帶通濾波器急劇降低未濾波LVCMOS輸出轉(zhuǎn)換速率,以及將方波轉(zhuǎn)換為正弦波的過(guò)程。

?

圖13 時(shí)鐘抖動(dòng)對(duì)采樣時(shí)鐘轉(zhuǎn)換速率的影響

?

?

表4 90-fs時(shí)鐘抖動(dòng)的SNR結(jié)果

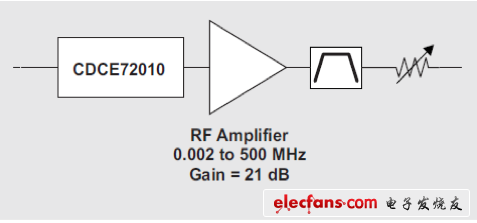

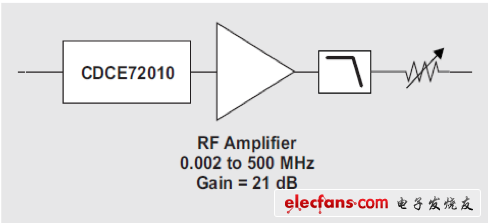

改善轉(zhuǎn)換速率的一種方法是:在CDCE72010的LVCMOS輸出和帶通濾波器之間添加一個(gè)具有相當(dāng)量增益的低噪聲RF放大器,參見(jiàn)圖14。該放大器應(yīng)該放置于濾波器前面,這樣便可以將其對(duì)時(shí)鐘信號(hào)的噪聲影響程度限定在濾波器帶寬,而非ADC的時(shí)鐘輸入帶寬。由于下一個(gè)試驗(yàn)的放大器具有21dB的增益,因此我們?cè)趲V波器后面增加了一個(gè)可變衰減器,旨在匹配濾波后LVCMOS信號(hào)到時(shí)鐘生成器濾波后輸出的轉(zhuǎn)換速率。該衰減器可防止ADC的時(shí)鐘輸入超出最大額定值。

?

圖14 帶通濾波器前面添加RF放大器來(lái)降低轉(zhuǎn)換速率

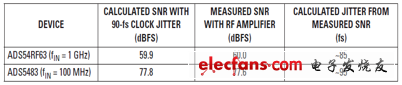

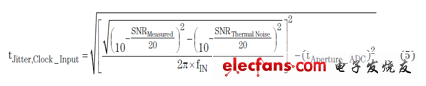

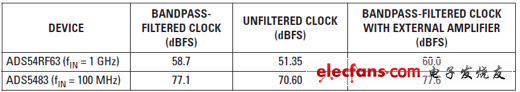

通過(guò)在時(shí)鐘輸入通路中安裝低噪聲RF放大器,兩個(gè)數(shù)據(jù)轉(zhuǎn)換器重復(fù)進(jìn)行了高輸入頻率的SNR測(cè)量,其結(jié)果如表5所示。我們可以看到,測(cè)得SNR和預(yù)計(jì)SNR匹配的非常好。使用下面的方程式 5,計(jì)算得到的時(shí)鐘抖動(dòng)值在90-fs時(shí)鐘抖動(dòng)的5fs以?xún)?nèi),其結(jié)果通過(guò)相位噪聲測(cè)得推導(dǎo)得出。

?

表5 90-fs時(shí)鐘抖動(dòng)和RF放大器的SNR結(jié)果

?

未濾波采樣時(shí)鐘試驗(yàn)

為了強(qiáng)調(diào)濾波采樣時(shí)鐘的重要性,在下一個(gè)試驗(yàn)中,我們將時(shí)鐘帶通濾波器從CDCE72010輸出端去除。在圖15所示結(jié)構(gòu)中,我們使用了E5052A相位噪聲分析儀來(lái)捕獲時(shí)鐘相位噪聲。但是不幸的是,該分析儀對(duì)相位噪聲的測(cè)量?jī)H達(dá)到40-MHz載波頻率偏移,并且在這點(diǎn)以外沒(méi)有給出任何相位噪聲特性的相關(guān)信息。

?

圖15 未濾波采樣時(shí)鐘輸入的測(cè)試裝置結(jié)構(gòu)

要設(shè)定使用未濾波時(shí)鐘時(shí)的正確積分上限,我們必須再一次復(fù)習(xí)一下采樣理論。CDCE72010的未濾波時(shí)鐘輸出看起來(lái)像一種具有快速升降沿的方波,而其升降沿由時(shí)鐘頻率的基頻正弦波高階諧波引起。這些諧波的振幅比基頻低,且其振幅隨諧波階增加而下降。

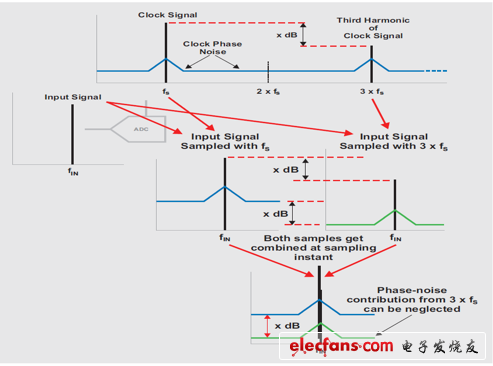

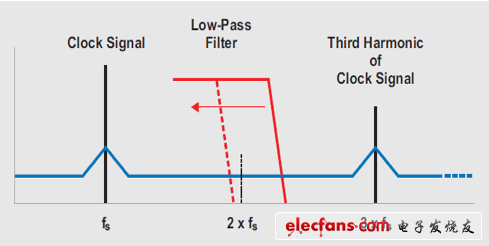

在采樣時(shí)間,基頻正弦波及高階諧波與輸入信號(hào)混頻,如圖16所示。(為了簡(jiǎn)單起見(jiàn),僅顯示了一個(gè)諧波。)因此,三階諧波周?chē)南辔辉肼暸c輸入信號(hào)混頻,而第三諧波也形成一個(gè)混頻結(jié)果。但是,由于時(shí)鐘信號(hào)的第三諧波的振幅更低,因此該混頻結(jié)果的振幅也被降低。

?

圖16 采樣時(shí)間時(shí)鐘基頻及其諧波與輸入信號(hào)混頻

兩個(gè)采樣信號(hào)組合在一起時(shí),我們可以看到,一旦振幅差異超出~3 dB時(shí),由第三諧波引起的總相位噪聲減弱為最小。由于基頻和第三諧波之間的交叉點(diǎn)為2 × fs,將寬帶相位噪聲積分至2 × fs可以得到相當(dāng)準(zhǔn)確的結(jié)果。

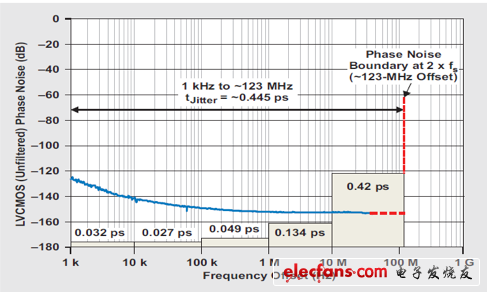

如后面圖19所示,CDCE72010的未濾波LVCMOS輸出相位噪聲在–153 dBc/Hz附近穩(wěn)定,其始于~10 MHz偏移頻率,原因可能是LVCMOS輸出緩沖器的熱噪聲。ADS54RF63 EVM具有~1 GHz(受限于變壓器)的時(shí)鐘輸入帶寬;因此理論上而言,應(yīng)該可以對(duì)相位噪聲求積分為~1GHz(在900-MHz偏移頻率的3dB時(shí)下降)。這會(huì)帶來(lái)~1.27ps的采樣時(shí)鐘抖動(dòng),并將fIN = 1GHz的SNR降至~42.8 dBFS!

?

圖17 低通濾波器前面添加RF放大器來(lái)降低轉(zhuǎn)換速率

?

圖18 不同低通濾波器限制相位噪聲

?

圖19 外推 (extrapolate) 123-MHz偏移頻率的未濾波相位噪聲

實(shí)際SNR測(cè)量結(jié)果比表6所列要好不少。對(duì)比實(shí)際測(cè)量結(jié)果,計(jì)算得時(shí)鐘抖動(dòng)和SNR之間存在巨大的差異。這表明,LVCMOS輸出的相位噪聲實(shí)際較好地限定在由變壓器決定的900-MHz偏移頻率界限以?xún)?nèi)。

?

表6 1.27-ps時(shí)鐘抖動(dòng)的SNR結(jié)果

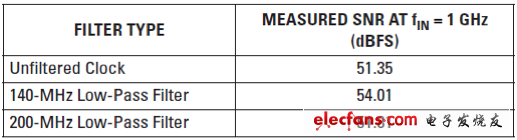

為了證明未濾波時(shí)鐘信號(hào)的相位噪聲需要積分至約兩倍采樣頻率,我們實(shí)施了如下試驗(yàn):在CDCE72010輸出和ADS54RF63時(shí)鐘輸入之間添加不同的低通濾波器。

需要注意的是,與先前試驗(yàn)中的帶通濾波器一樣,3X時(shí)鐘頻率以下帶寬的低通濾波器降低了時(shí)鐘信號(hào)的轉(zhuǎn)換速率。低通濾波器消除了會(huì)產(chǎn)生更快速時(shí)鐘信號(hào)升時(shí)間和轉(zhuǎn)換速率的高階諧波,從而增加了ADC的孔徑抖動(dòng)。正因如此,我們將前面試驗(yàn)的相同低噪聲RF放大器添加到時(shí)鐘通路,并且利用可變衰減器讓轉(zhuǎn)換速率匹配信號(hào)生成器(參見(jiàn)圖17)。

將不同轉(zhuǎn)角頻率的低通濾波器用于ADS54RF63的采樣時(shí)鐘(如圖18所示),得到了一些如表7所列有趣值。該試驗(yàn)結(jié)果表明,LVCMOS輸出對(duì)時(shí)鐘抖動(dòng)的相位噪聲影響被限制在約200到250 MHz,其相當(dāng)于122.88-MHz時(shí)鐘信號(hào)的80-MHz到130-MHz偏移頻率,并約為2x采樣頻率。因此,將寬帶相位噪聲擴(kuò)至123-MHz偏移頻率,會(huì)產(chǎn)生~445 fs的時(shí)鐘抖動(dòng),如圖19所示。理想情況下,積分下限應(yīng)該位于500 Hz處(原因是選擇的131000點(diǎn)FFT);但是,500-Hz到1 kMz偏移頻率的抖動(dòng)貢獻(xiàn)值極其低,因此為了簡(jiǎn)單起見(jiàn)其在本測(cè)量中被忽略。

?

表7 ADS54RF63的測(cè)得SNR

利用調(diào)節(jié)后的相位噪聲曲線(xiàn)圖,計(jì)算得抖動(dòng)較好地匹配了SNR測(cè)量結(jié)果,其在ADS54RF63和ADS5483的10到30fs范圍內(nèi)(參見(jiàn)表8)。考慮到在第三諧波周?chē)赡艽嬖谙辔辉肼暤妮^小時(shí)鐘抖動(dòng)影響,該計(jì)算得SNR只是一種非常接近的估算結(jié)果。

?

表8 445-fs時(shí)鐘抖動(dòng)的SNR結(jié)果

?

表9 濾波后及未濾波時(shí)鐘的測(cè)得SNR

結(jié)論

本文介紹了使用某個(gè)濾波或未濾波時(shí)鐘源時(shí),如何正確地估算數(shù)據(jù)轉(zhuǎn)換器的SNR。表9概括了得到的結(jié)果。盡管時(shí)鐘輸入的帶通濾波器對(duì)于最小化時(shí)鐘抖動(dòng)是必要的,但實(shí)驗(yàn)表明它會(huì)降低時(shí)鐘轉(zhuǎn)換速率,并使ADC的孔徑抖動(dòng)降級(jí)。因此,最佳的時(shí)鐘解決方案應(yīng)包括一個(gè)限制相噪影響的帶通濾波器,以及一定的時(shí)鐘振幅放大和轉(zhuǎn)換速率,目的是最小化ADC的孔徑抖動(dòng)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論